## **Doctoral Thesis**

# A Study on the Reliability of Metal Gate–La<sub>2</sub>O<sub>3</sub> Thin Film Stacked Structures

(Summary of Doctoral Thesis)

**Joel Molina Reyes**

March 2007

Principal Supervisor: Professor **Hiroshi Iwai** Associate Supervisor: Visiting Professor **Nobuyuki Sugii**

### Abstract

This work discusses charge trapping effects and the dielectric reliability of metal-gated La<sub>2</sub>O<sub>3</sub> stacked dielectrics. It will be shown that the gate stacks suffer from severe charge trapping, which causes adverse effects on the characteristics of La<sub>2</sub>O<sub>3</sub>-gated MIS devices like flat band Vfb and threshold voltages Vth shifts after stress. On the other hand, the lifetime projection of La<sub>2</sub>O<sub>3</sub> after time-dependent dielectric breakdown measurements (TDDB) guarantees a 10 years operation period for  $La_2O_3$ -gated MIS devices at low gate voltages before breakdown. That latter result encourages us to look for alternative ways to minimize the electrical degradation found in La<sub>2</sub>O<sub>3</sub>-gated MIS devices after stress, whether by modifications in the deposition process of La<sub>2</sub>O<sub>3</sub> or by introducing post-deposition processes like thermal treatments before and after the metallization step. Moreover, the problem of IL formation atop the silicon substrate still is a great challenge to be solved since  $La_2O_3$  tends to develop this lower-k IL when deposited on silicon, thus increasing the final equivalent oxide thickness (EOT) of the whole high-k/IL stacked structure. Because of this La<sub>2</sub>O<sub>3</sub>-IL stack formation, the deterioration of the oxide stack will depend on the nature of these layers as well as the nature of the injected species (electrons or holes) under stress.

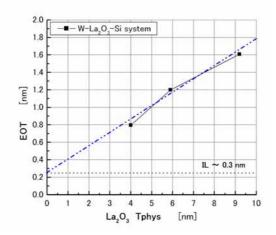

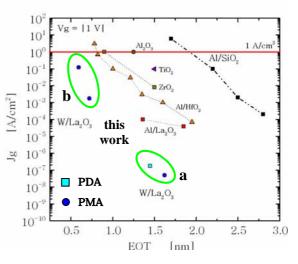

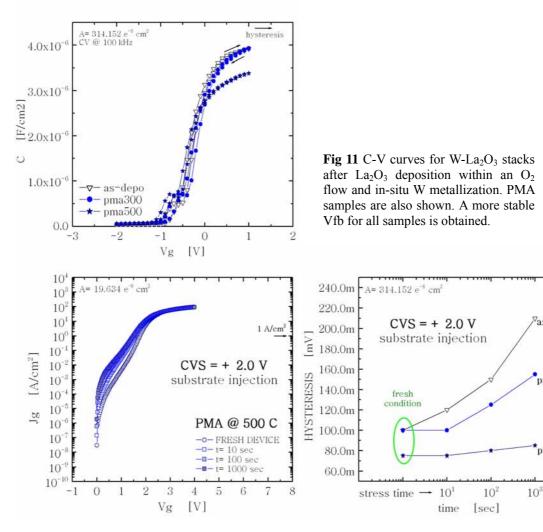

From carrier separation measurements, substrate electron injection results in a shorter time to oxide breakdown t<sub>bd</sub> as compared to gate electron injection. Nevertheless, longer t<sub>bd</sub> for La<sub>2</sub>O<sub>3</sub>/IL as well as smaller degradation of its electrical characteristics with time were obtained after improving the deposition process and post-deposition process for this oxide. Specifically, an *in-situ* metallization for La<sub>2</sub>O<sub>3</sub> minimizes the exposition of La<sub>2</sub>O<sub>3</sub> surface to environment and post-metallization annealing (PMA), can help to reduce the damage introduced into La<sub>2</sub>O<sub>3</sub> and its interfaces after the deposition by sputtering of the gate electrode, thus increasing the final reliability of La<sub>2</sub>O<sub>3</sub>-gated MOS devices. Further improvements on the physical characteristics of La<sub>2</sub>O<sub>3</sub> will increase its reliability so that this dielectric material will have good chances to replace conventional gate oxides well beyond the 45 nm node since the fabrication of La<sub>2</sub>O<sub>3</sub>-gated MIS devices with EOT < 1 nm has been already demonstrated.

### Organization of this study

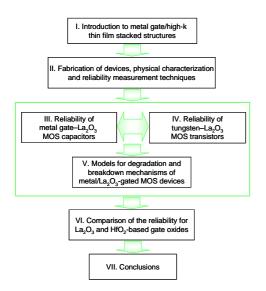

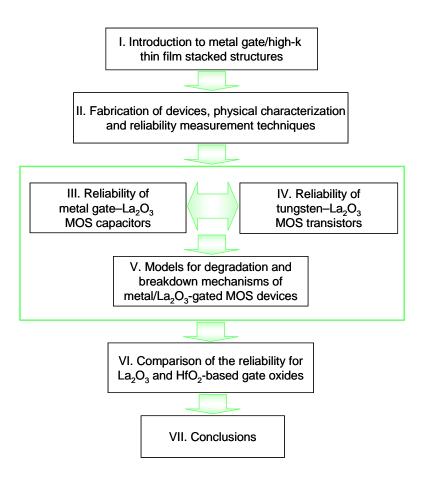

This dissertation consists of seven chapters which are described schematically in fig. 1.

Figure 1 Outline of this dissertation.

#### Chapter 1

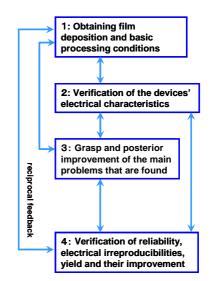

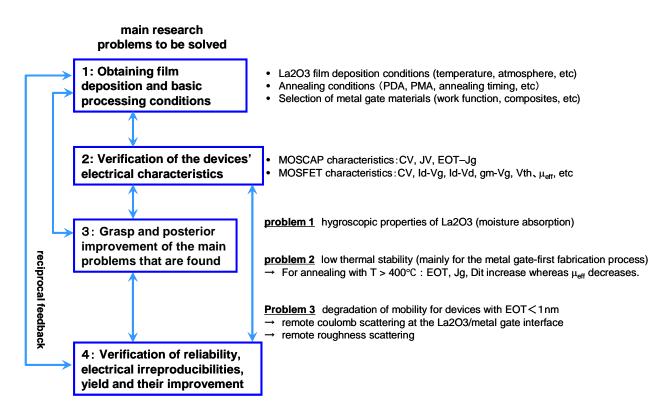

This chapter reviews and briefly discusses the long recognized necessity of conventional replacing oxides gate (SiO<sub>2</sub>-based) with the Metal/high-k gate stack structure in order to continue the scaling down of CMOSFET devices. The requirements for metal gates and high-k materials are discussed along with a brief review of the rare-earth oxides (REO) that are being considered as potential candidates for the replacement of  $SiO_2$ . Also, the main research problems that have been found for the development of La<sub>2</sub>O<sub>3</sub>-based dielectrics at Iwai Lab are discussed here, see fig. 2. Next, some results

obtained at Iwai Lab are presented and then, the reasons about the significance of researching the reliability properties of La<sub>2</sub>O<sub>3</sub> are presented.

Figure 2 Main research problems to be solved.

This is followed by the introduction to  $La_2O_3$  which is a member of the REO family, and the motivations that this material poses over other high-k dielectric materials.

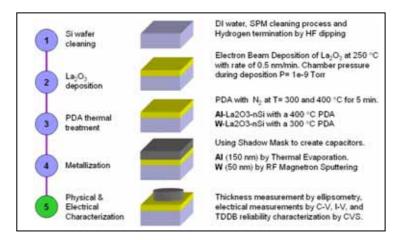

#### Chapter 2

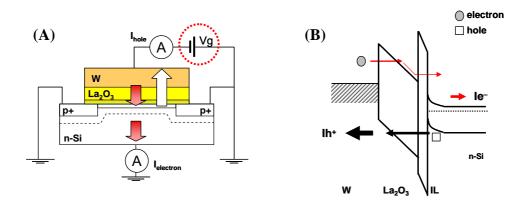

Here, we describe the fabrication and characterization methods used throughout this study. Detail fabrication flows of MOSCAP and MOSFET as well the basic principles behind all fabrication equipments were briefly discussed. The measurement setups and characterization methods used in this study were also mentioned, taking especial emphasis on the reliability characterization techniques (see table 1) that were applied to our fabricated samples. The electrical stress for the La<sub>2</sub>O<sub>3</sub>-gated MOS devices was applied by: a ramped (TZDB) or constant voltage stress (TDDB). The measurement setup for interface-states density Dit after stress is also presented. Dit was obtained after chargepumping measurements. The carrier separation measurement was also introduced in order to obtain a clearer vision on the phenomena of degradation/breakdown since this  $La_2O_3$ technique is able to separate the individual contributions of tunneling electrons and holes flowing thorough the stacked oxide.

| Measurement        | Obtained data                                    |

|--------------------|--------------------------------------------------|

| TZDB               | Breakdown strength, SILC                         |

| TDDB               | Oxide lifetime, Tbd, Qbd, SILC, Vfb and Vt shift |

| Charge pumping     | Interface-states density Dit                     |

| Carrier separation | Ielectrons, Iholes, BKD mechanism                |

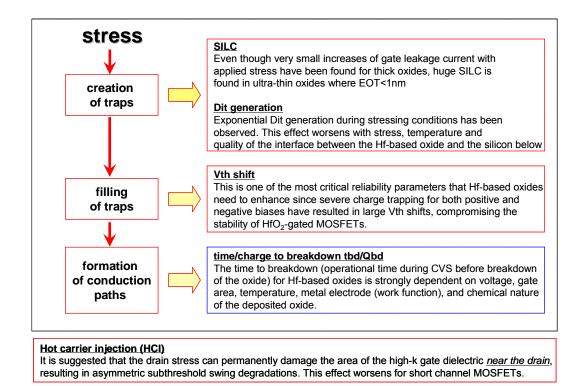

Depending on the intensity of the applied stress, electrically-induced degradation (SILC, Dit generation, Vth shift, etc) and/or breakdown condition (hard breakdown) can be reached within  $La_2O_3$ .

#### Chapter 3

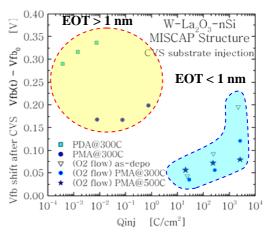

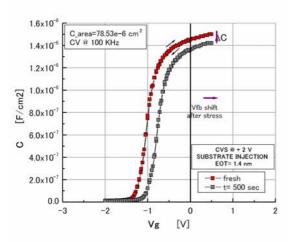

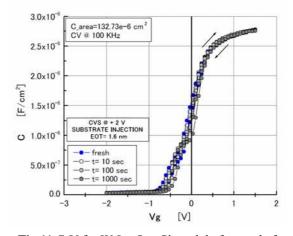

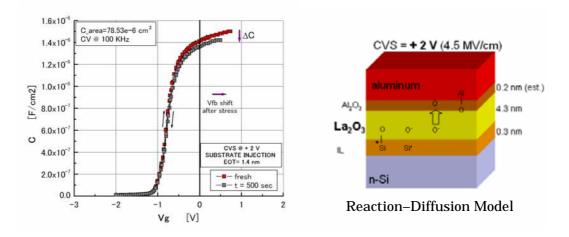

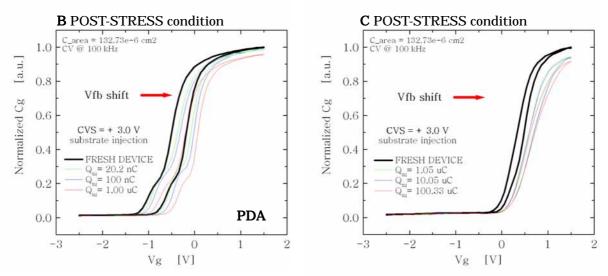

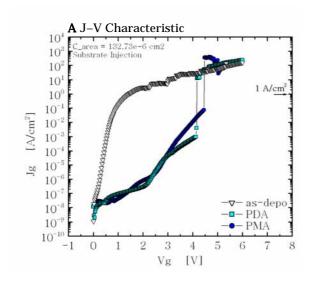

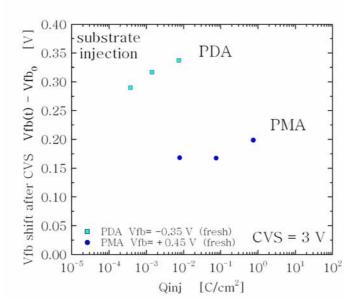

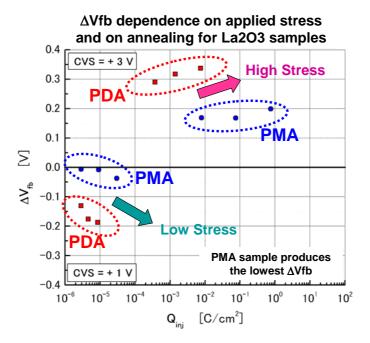

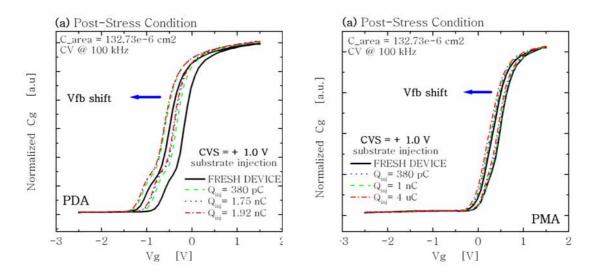

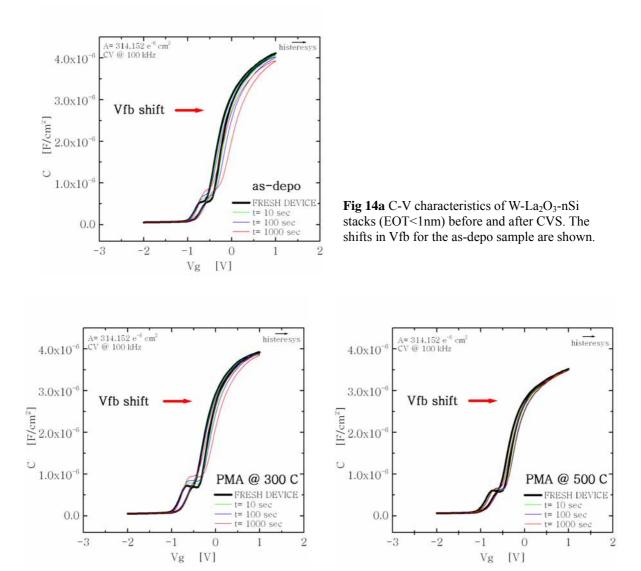

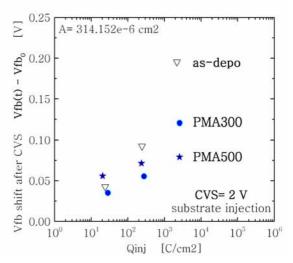

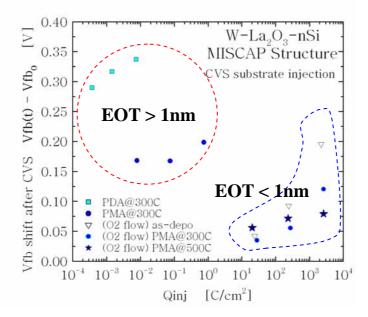

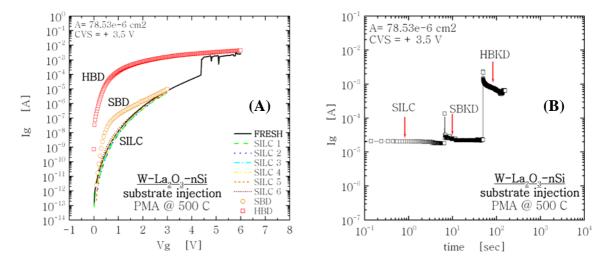

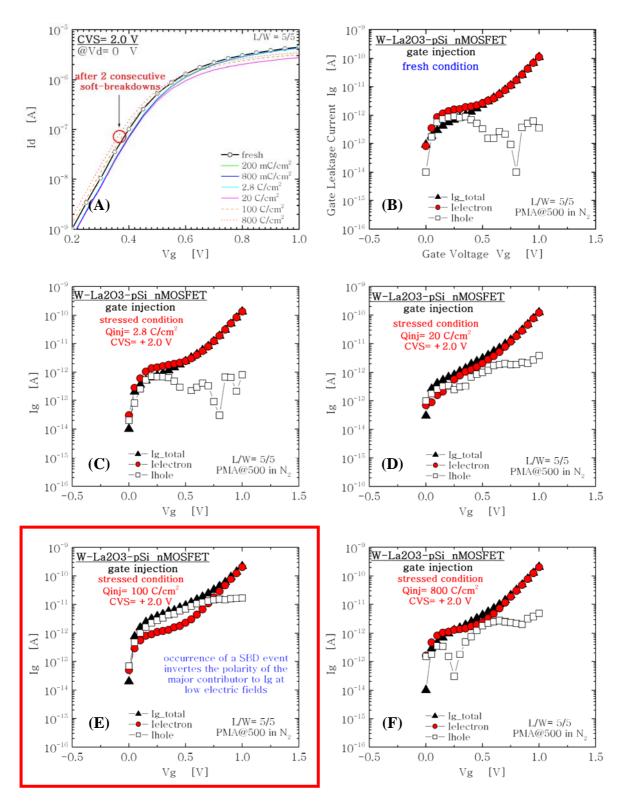

This chapter presents the results obtained from reliability characterization of metal-  $La_2O_3$  MOS capacitor devices under low and high-voltage stressing conditions. The shift in flat-band voltage Vfb for low or high-stressing conditions showed electric-field dependence after stress. By stressing  $La_2O_3$  with TDDB, the degradation/breakdown of the dielectric will produce different effects on the final electrical characteristics of the stressed devices. First, the measurements of Vfb shift after stress for thick ad thin films were quantized and both results are shown in fig. 3.

Figure 3 Vfb shift after stress for La<sub>2</sub>O<sub>3</sub>.

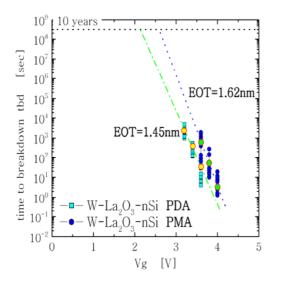

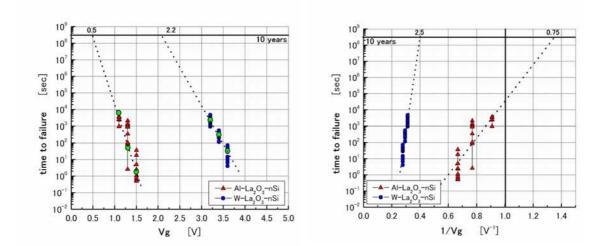

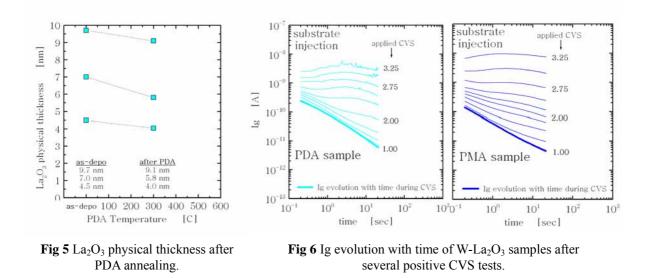

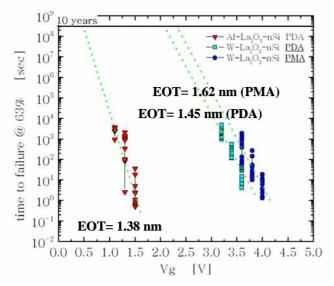

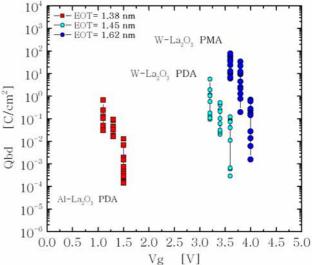

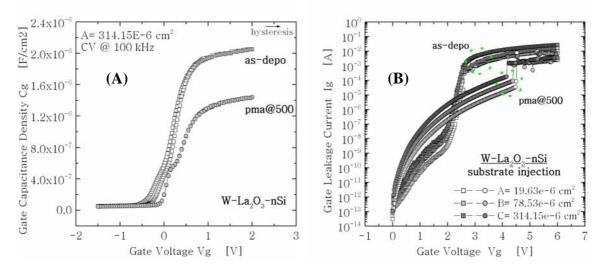

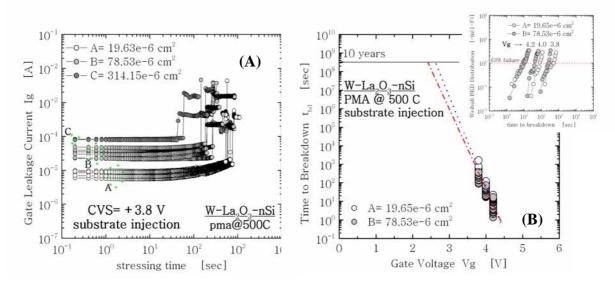

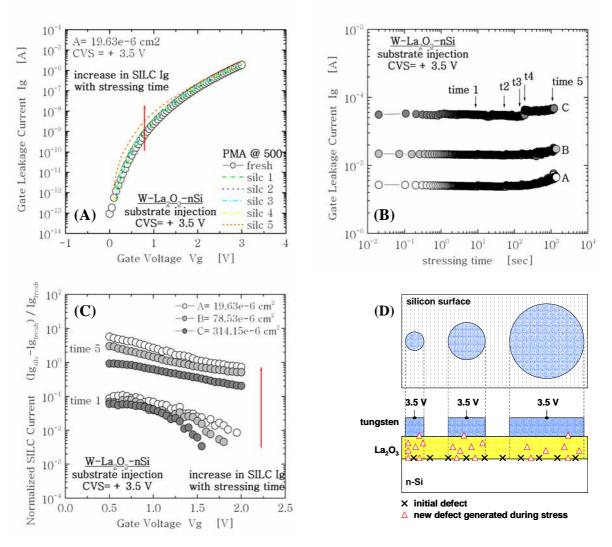

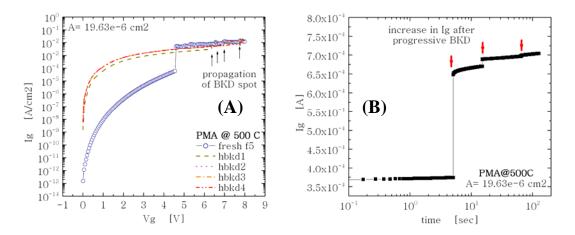

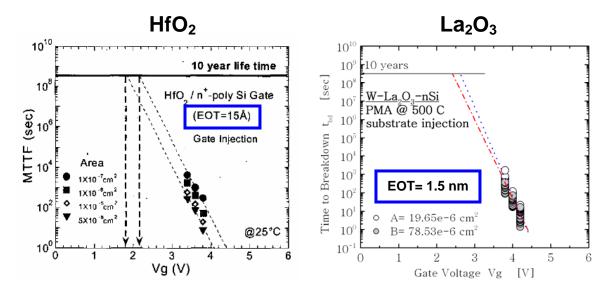

It is clearly seen that thinner films with a modified La<sub>2</sub>O<sub>3</sub> deposition process shows better reliability characteristics regarding to Vfb shift after substrate injection of electrons into the oxide. This shift in Vfb can be reduced depending on the processing conditions applied for La<sub>2</sub>O<sub>3</sub>. The use post-metallization annealing (PMA) was of great help in order to reduce Vfb shift after stress (as compared to post-deposition annealing PDA) so that better reliability properties were obtained. We also stressed the dielectric with higher and longer stressing conditions so that HBD condition would develop in order to obtain the lifetime of La<sub>2</sub>O<sub>3</sub>-gated capacitors and the required density of charge for breakdown Qbd. By extrapolating the obtained lifetime data to lower operation

voltages, lifetime expectancy for  $La_2O_3$  of 10 years was predicted by using the linear Vg model, see fig. 4. PMA increases the lifetime expectancy of  $La_2O_3$  compared to PDA thermal treatment.

Figure 4 Lifetime projection for  $W-La_2O_3$  gated MOSCAP after PDA/PMA annealing.

#### Chapter 4

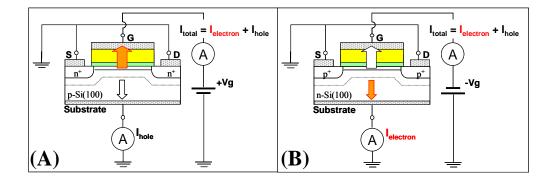

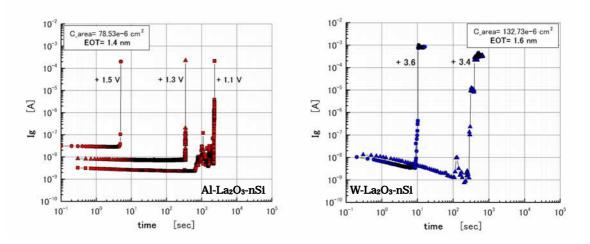

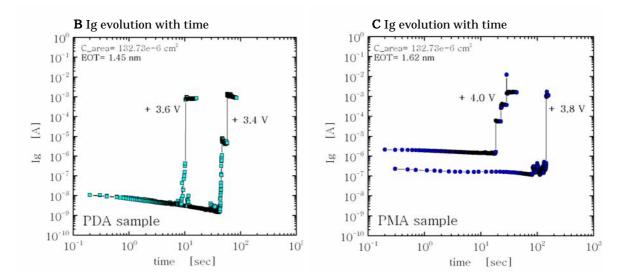

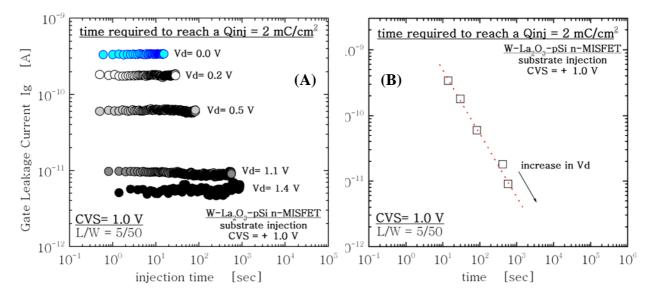

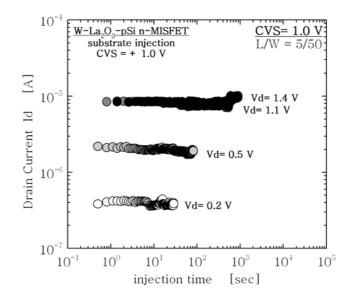

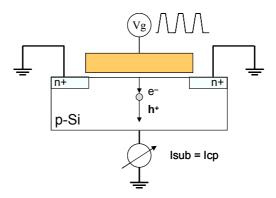

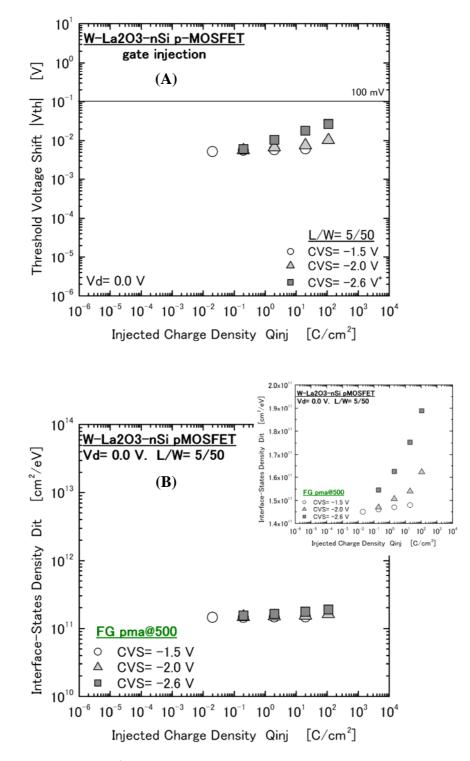

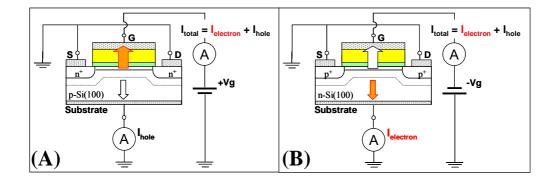

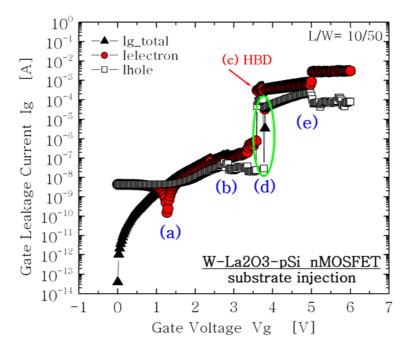

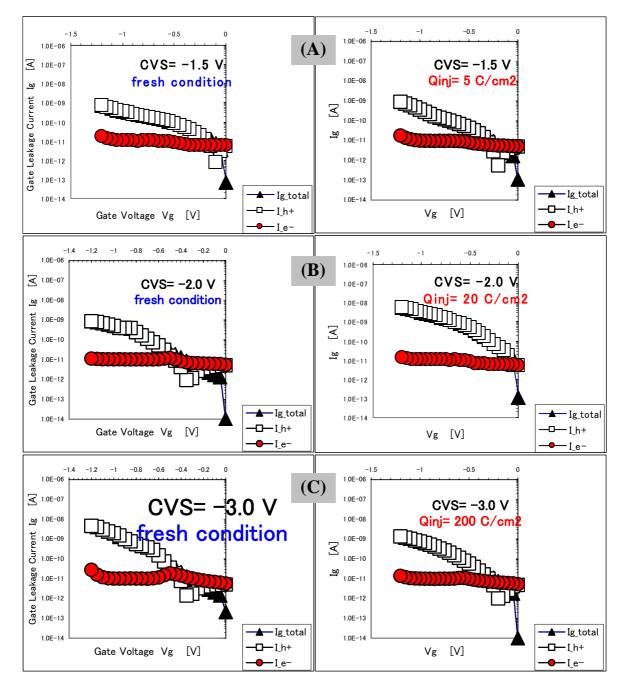

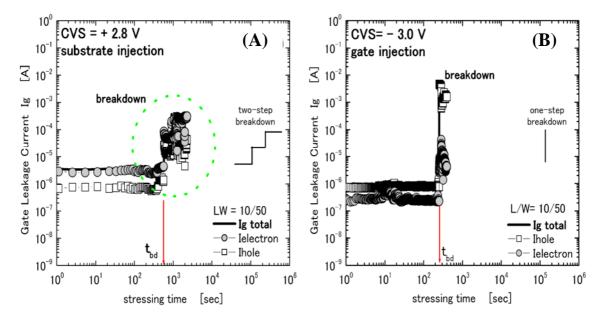

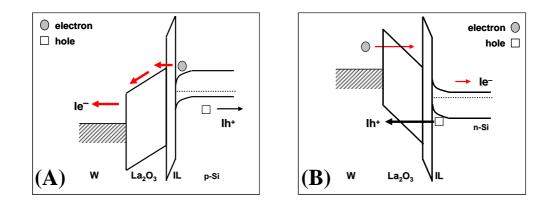

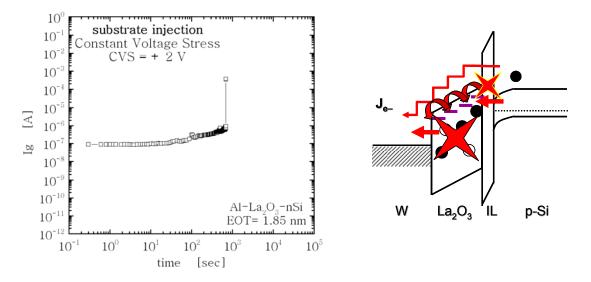

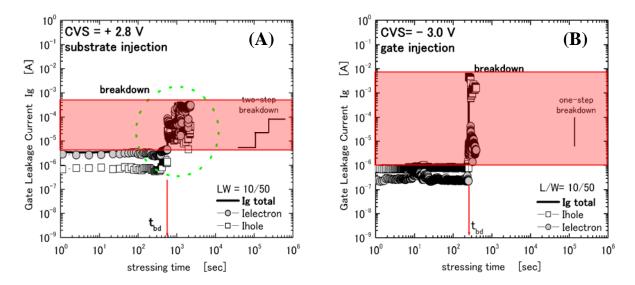

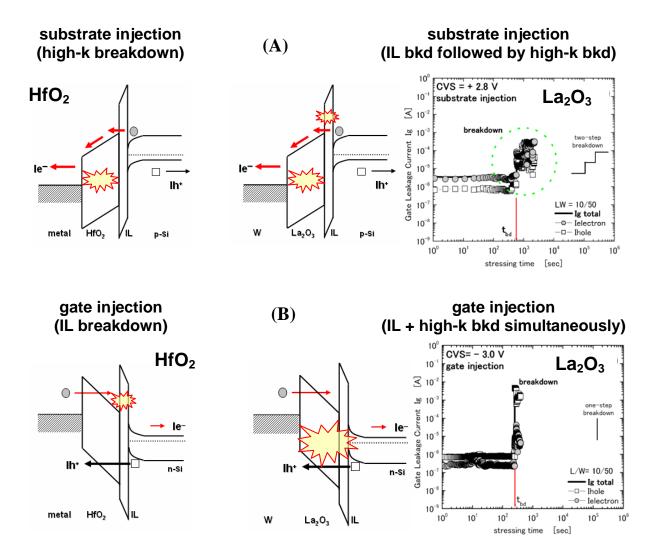

This chapter presents the results of applying electrical stress on the gate of La<sub>2</sub>O<sub>3</sub>-gated MOSFET devices. In MOS transistors, it is possible to monitor not only the gate current Ig but also the substrate current I<sub>bulk</sub> simultaneously. This is a well-known technique usually referred to as carrier separation that allows identifying the dominant carrier type on the gate leakage current. From separation carrier measurements it was observed that electron injection was the dominant component of total gate leakage current Ig under positive TDDB whereas hole injection was the dominant component under negative TDDB, see fig. 5 A-B.

Figure 5 Evolution of gate leakage current with stressing time. (A)  $I_{electron}$  is the dominant component of the total Ig during substrate injection of electrons. (B)  $I_{hole}$  is the dominant component of the total Ig during gate injection of electrons.

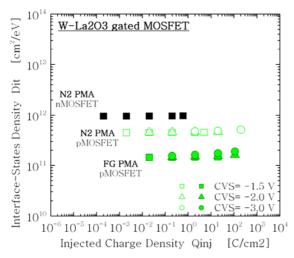

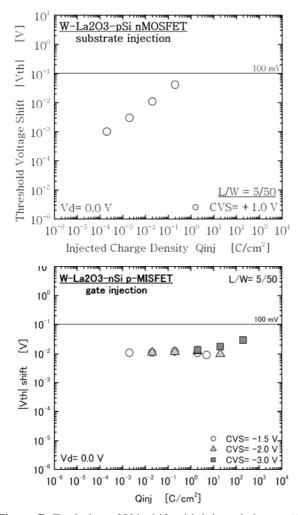

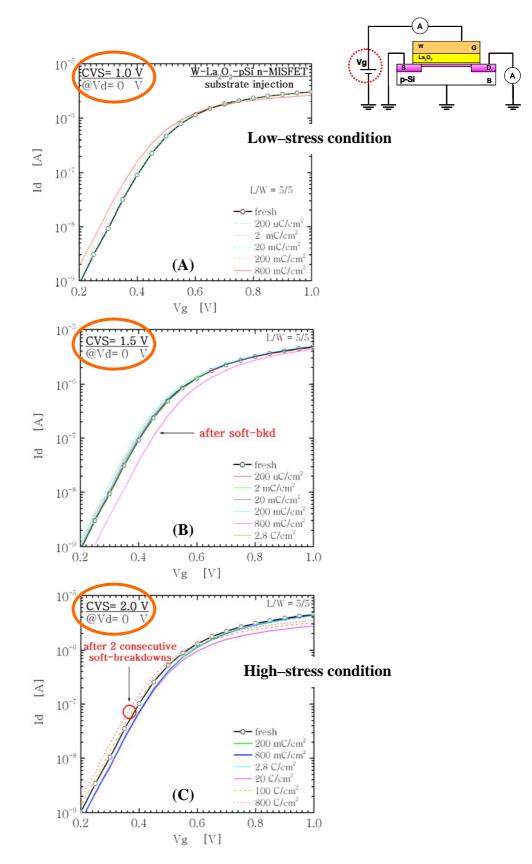

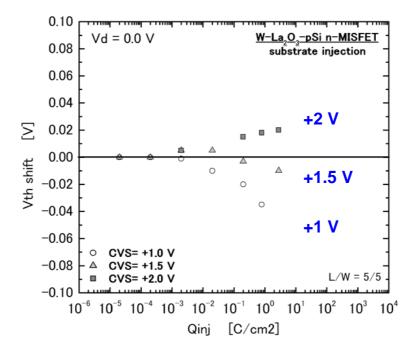

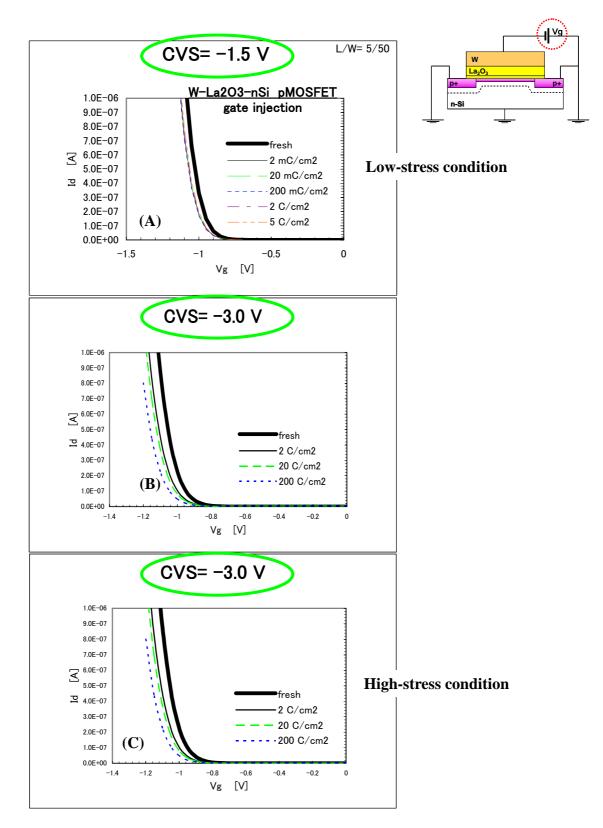

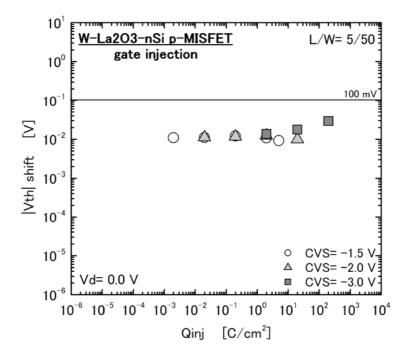

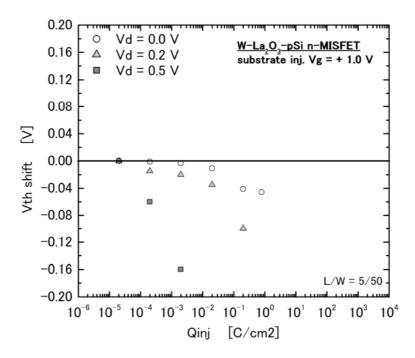

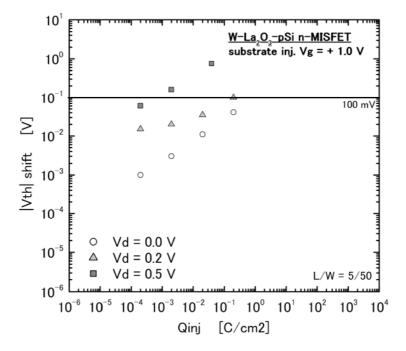

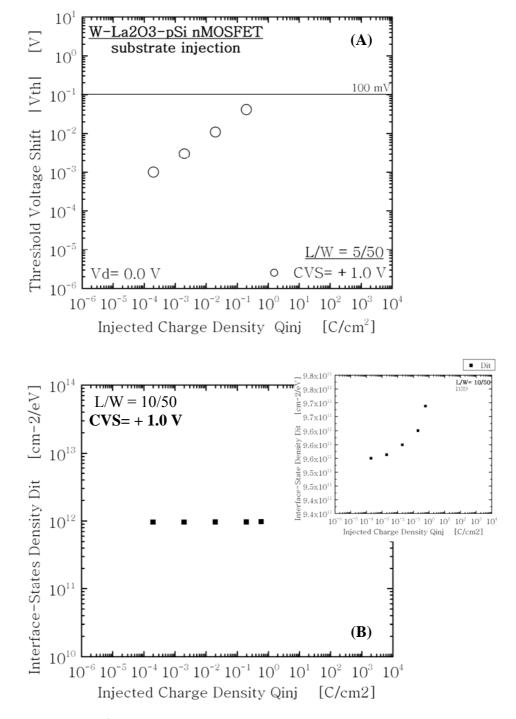

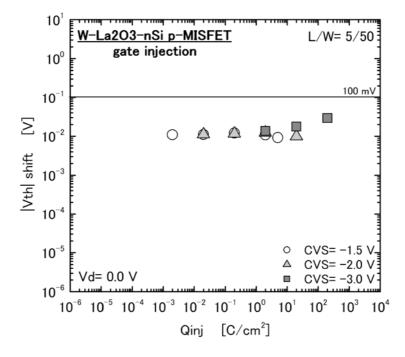

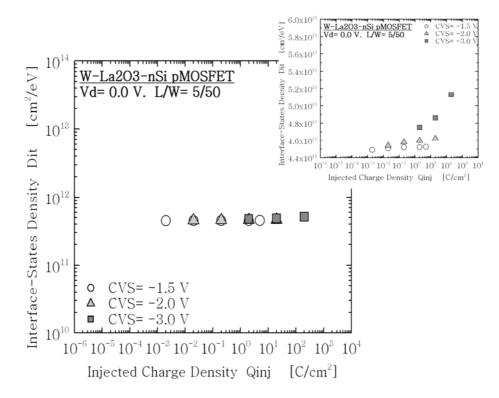

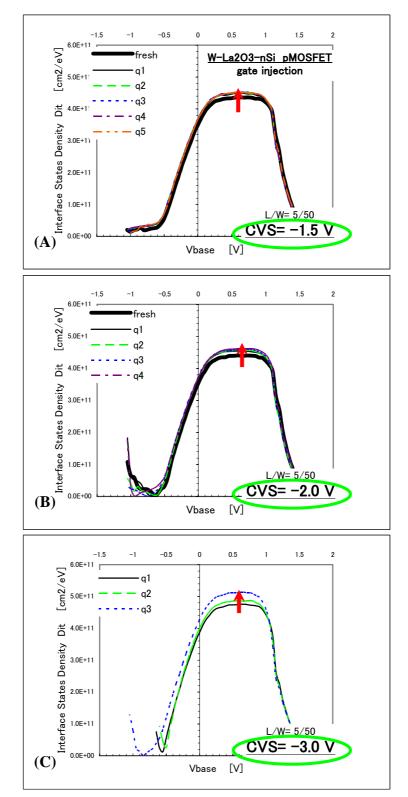

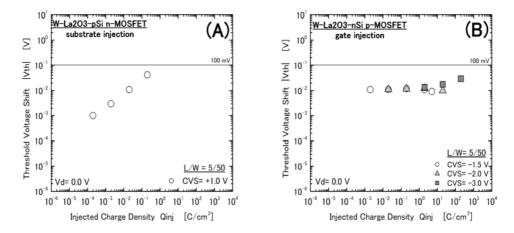

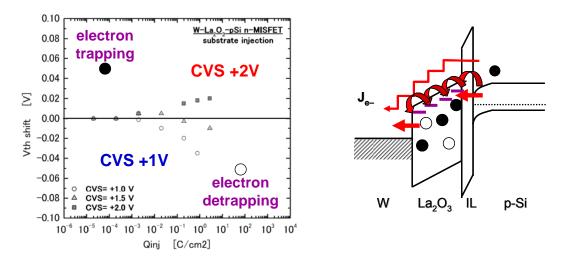

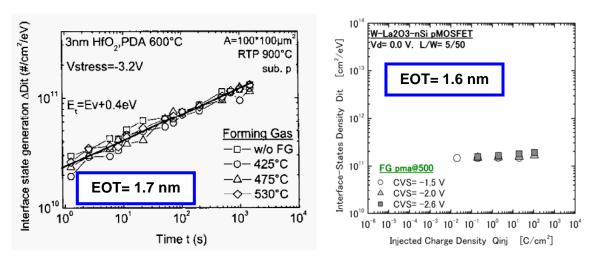

Also, since the degradation of  $La_2O_3$ involves both interfaces of the oxide with the metal and the silicon substrate, measurements of interface-state density Dit after stress were performed in order to correlate Vth shift with respect to Dit. The results are shown in fig. 6. Electrically-induced Dit generation after constant voltage stress (CVS) is almost zero for La<sub>2</sub>O<sub>3</sub> and the use of forming gas (FG) during the PMA processing reduces the initial level of Dit, which indicates that some of the dangling bonds at the silicon surface have been passivated. The shift in Vth for nMOSFET and pMOSFET devices is shown in fig. 7 A-B.

**Figure 6** Interface-states Dit measurements for nMOSFETs and pMOSFETs devices after positive and negative CVS respectively.

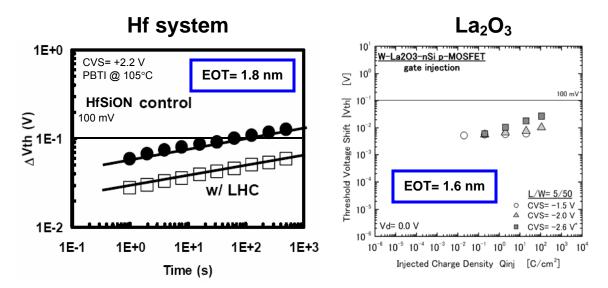

**Figure 7** Evolution of Vth shift with injected charge. (A) nMOSFET devices show an exponential shift in Vth after stress. (B) pMOSFET devices show almost no change in Vth in the same way as in the Dit generation case.

From fig. 7 A-B we can see that for pMOSFET devices, the change in Vth during stressing is very small compared to the exponentially increasing shift in Vth for nMOSFETs. The shift in Vth for the nMOSFET device would come by the increase in fixed charge (Qf) instead of the almost zero Dit after stress.

#### Chapter 5

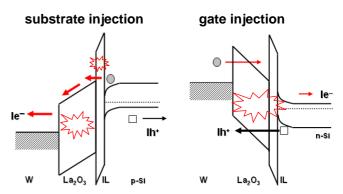

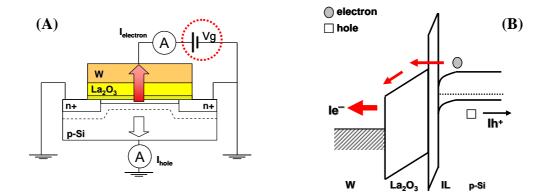

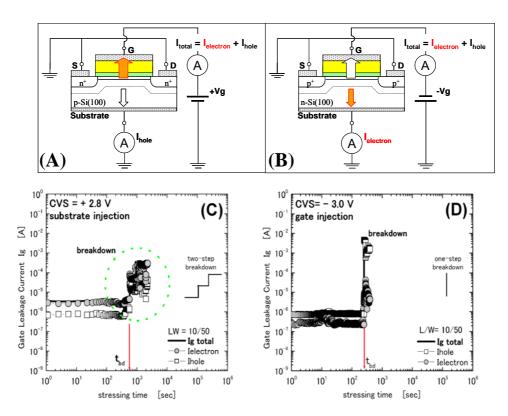

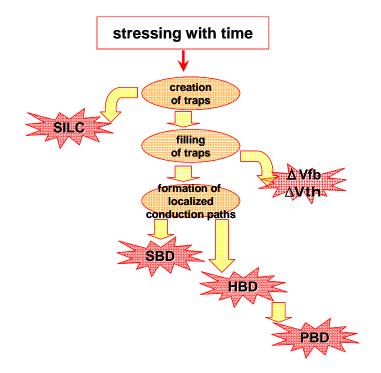

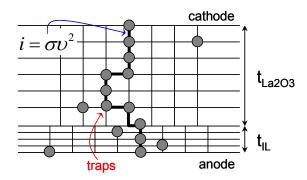

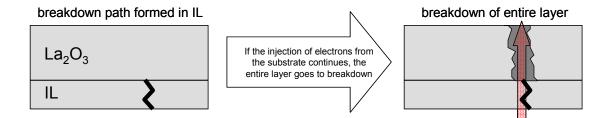

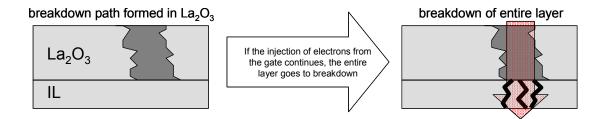

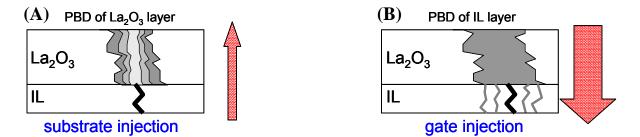

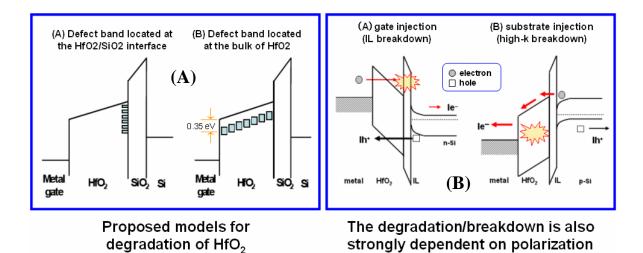

In this chapter, the previous results from the reliability characterization of  $La_2O_3$ -gated MOSCAP and MOSFET devices are joined in order to develop a more concise model explaining the mechanisms behind the degradation and breakdown of the  $La_2O_3$ -IL stacked layers on silicon; see fig. 8.

**Figure 8** Proposed models for the breakdown of La<sub>2</sub>O<sub>3</sub>-gated MOS devices during substrate/gate injection conditions after positive/negative CVS.

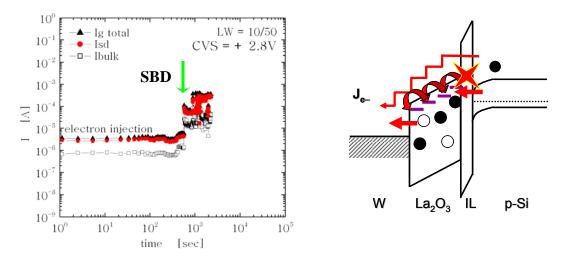

At this stage, it has been concluded that during substrate injection,  $La_2O_3$  presents IL breakdown followed by the breakdown of the  $La_2O_3$  film. For the gate injection case, simultaneous breakdown of both the IL and the  $La_2O_3$  film is proposed. Lastly, we briefly propose methods to improve reliability so that better projections and enhanced degradation and lifetime characteristics of La2O3 after stress can be obtained.

#### **Chapter 6**

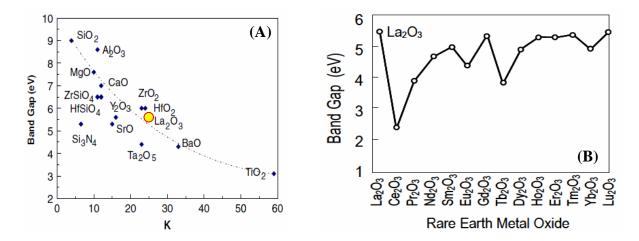

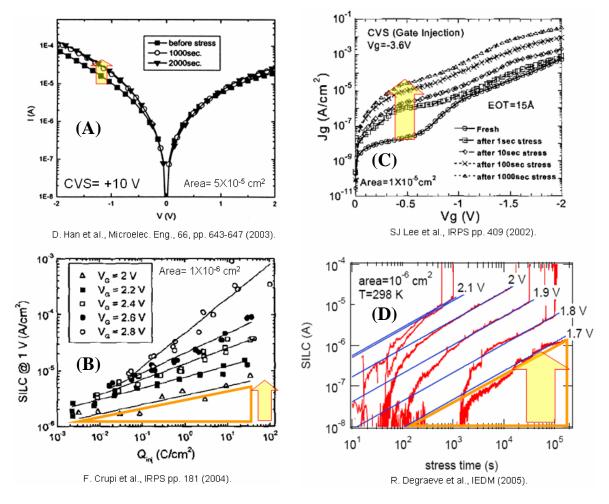

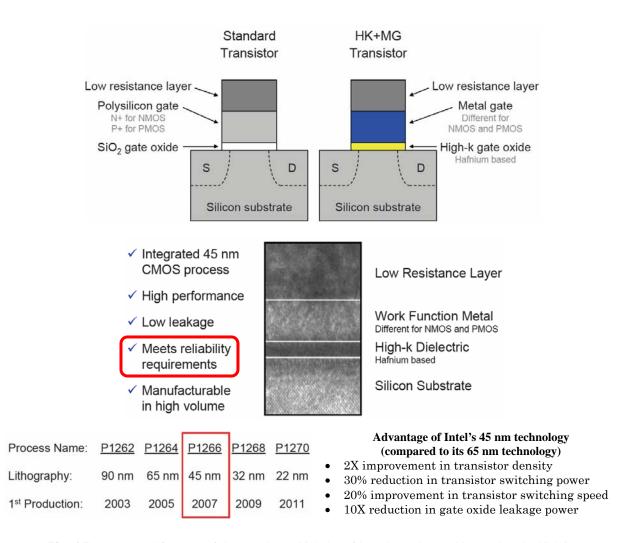

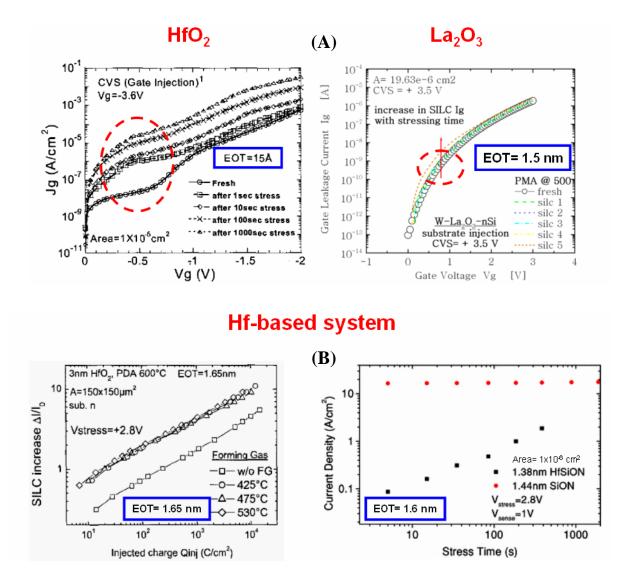

Here, a comparison of the reliability properties for Hf-based oxides and La<sub>2</sub>O<sub>3</sub> is presented. In order to predict the reliability of the La<sub>2</sub>O<sub>3</sub> dielectrics for use of the gate insulator, the published data for that of HfO2-based oxides were examined and compared with that of the  $La_2O_3$ . In general, the  $La_2O_3$  dielectrics show higher reliability than that of HfO<sub>2</sub>-based dielectrics, although some of the reliability evaluations have not been carried out for the La<sub>2</sub>O<sub>3</sub>. Better SILC, Dit generation, Vth shift after stressing and time to breakdown data has been found for La<sub>2</sub>O<sub>3</sub>-gated MOS devices as compared to HfO<sub>2</sub>. On the other hand, the published data in the journal and the conference predict not sufficient reliability for the Hf-based oxide to be used in commercial products. However, Intel announced Hf-based high-k gate oxide introduction into the 45 nm CMOS with sufficiently high reliability which meets the commercial production thus the reliability of the Hf-based oxides with EOT down to sub 1 nm seems to have been already established, fig. 9 below.

n hased

Figure 9 Metal gate/high-k (Hf-based) stacked architecture developed by Intel and which meets the reliability requirements for commercial production.

At this moment, any fundamental problems for the reliability of La<sub>2</sub>O<sub>3</sub> dielectrics have not been found by this study; see table 1 below.

**Table 1**Summary of the reliability results for HfO<sub>2</sub> and La<sub>2</sub>O<sub>3</sub>-gated MOS devices.

| Material                          | La <sub>2</sub> O <sub>3</sub> *       | HfO <sub>2</sub> -based                |

|-----------------------------------|----------------------------------------|----------------------------------------|

| Property                          | EOT [nm]                               | EOT [nm]                               |

| SILC degradation                  | Estimated to be acceptable<br>[1.5 nm] | To be a problem<br>[1.5 nm]            |

| Dit generation                    | Estimated to be acceptable<br>[1.6 nm] | To be a problem<br>[1.7 nm]            |

| Vth shift                         | Estimated to be acceptable<br>[1.6 nm] | To be a problem<br>[1.8 nm]            |

| t <sub>bd</sub> , Q <sub>bd</sub> | Estimated to be acceptable<br>[1.5 nm] | Estimated to be acceptable<br>[1.5 nm] |

| HCI                               | ?                                      | Very poor                              |

\* High-temperature reliability measurements are needed.

Thus, it is expected that the  $La_2O_3$  reliability will meet the requirements for the production by the time when it is introduced into commercial devices.

#### **Chapter 7**

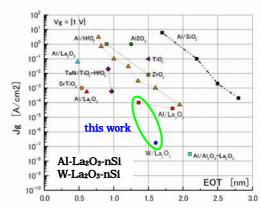

This chapter summarizes the findings and contributions of this study for the analysis of the reliability characteristics of La<sub>2</sub>O<sub>3</sub>-gated MOS devices. It was found that by using appropriate metal gate-La2O3 stacks in conjunction with thermal treatments, the problem of higher leakage current for low EOT could be substantially decreased. This has been achieved by avoiding the formation of an interfacial layer at the metal-La<sub>2</sub>O<sub>3</sub> interface by using tungsten as the gate electrode. Because of the La<sub>2</sub>O<sub>3</sub>–Silicon interfacial layers formation by annealing, the deterioration of the  $La_2O_3$ gate stack will depend on the nature of these layers as well as the nature of the injected species (electrons or holes) under the stress. In

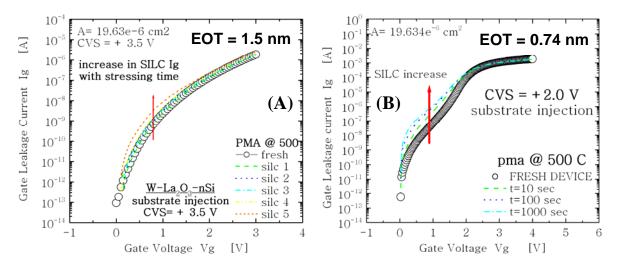

this respect, and from carrier separation measurements, the substrate injection of degrades severely electrons more the conduction characteristics of the La<sub>2</sub>O<sub>3</sub>-IL stack, where the IL degrades more severely during the stress. A longer lifetime for the breakdown of La<sub>2</sub>O<sub>3</sub> as well as smaller degradation of its electrical characteristics with time were obtained after improving the deposition process and post-deposition process for this oxide. An in-situ metallization for La<sub>2</sub>O<sub>3</sub> enhances its reliability by minimizing the exposition of La<sub>2</sub>O<sub>3</sub> surface to environment. On the other hand, by comparing the reliability properties of La<sub>2</sub>O<sub>3</sub>-gated MOS devices with those of HfO<sub>2</sub>-based gate oxides both with similar EOT, very important differences were found. It was observed that during SILC degradation, less degradation in gate leakage current after stress is found for La<sub>2</sub>O<sub>3</sub>-gated MOSCAP at the same EOT. Similarly, even though La<sub>2</sub>O<sub>3</sub> presents an initially higher density of interface-states Dit, the generation of additional Dit is lower compared to HfO<sub>2</sub>, in which an exponential generation of Dit is observed. With La<sub>2</sub>O<sub>3</sub>, additional Vth shift after electron injection is minimized. By comparing TDDB lifetime extrapolation data, a 10 years operation before breakdown for both high-k

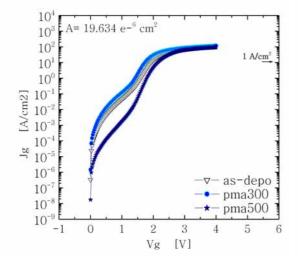

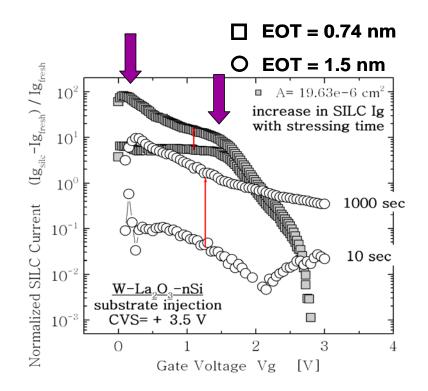

materials is guaranteed even at relatively high Vg > 1 V. Regarding to the breakdown models for these oxides, it was found that during injection. substrate a Hf-based system experiences high-k bulk breakdown whereas La<sub>2</sub>O<sub>3</sub> shows interfacial-layer (IL) breakdown followed by the breakdown of La<sub>2</sub>O<sub>3</sub> itself. During the gate injection condition, a Hf-based system mostly experiences IL breakdown whereas  $La_2O_3$  shows complete IL + high-k breakdown simultaneously. All the former results suggest that La<sub>2</sub>O<sub>3</sub>-gated MOS devices have an advantage over HfO<sub>2</sub> since better reliability results have been demonstrated for La<sub>2</sub>O<sub>3</sub>-gated devices at very similar EOT levels. By using very thin high-k films with EOT <1nm we have identified a large SILC increase for La<sub>2</sub>O<sub>3</sub>-gated devices so that it is thought that the degradation-related reliability of very thin La<sub>2</sub>O<sub>3</sub> gate oxides becomes compromised but their final lifetime before breakdown would remain within the specifications. Finally, even though the reliability results for HfO<sub>2</sub>-based gate oxides with EOT < 1nm that are found in the published literature are not good enough, the production of Hf-based MOSFET products for the 45 nm node announced by Intel make us think that the reliability issues for EOT < 1nmhave already been resolved.

**Doctoral Thesis**

# A Study on the Reliability of Metal Gate–La<sub>2</sub>O<sub>3</sub> Thin Film Stacked Structures

A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ADVANCED APPLIED ELECTRONICS INTERDISCIPLINARY GRADUATE SCHOOL OF SCIENCE AND ENGINEERING TOKYO INSTITUTE OF TECHNOLOGY FOR THE DEGREE OF DOCTOR OF ENGINEERING

**Joel Molina Reyes**

March 2007

Principal Supervisor: Professor Hiroshi Iwai

Associate Supervisor: Visiting Professor Nobuyuki Sugii

Tokyo Institute of Technology

# Contents

| Contents        |  |

|-----------------|--|

| List of tables  |  |

| List of figures |  |

| Abstract of this doctoral thesis | <br>. XIX |

|----------------------------------|-----------|

|                                  |           |

#### CHAPTER 1 INTRODUCTION TO METAL GATE/HIGH-K THIN FILM STACKED STRUCTURES 1 1.1 Brief summary of the history of semiconductor devices ..... 2 1.2 Beyond SiO<sub>2</sub>-based CMOS device scaling ..... 2 1.3 Requirements for metal gates and high-k materials 6 1.4 Review of rare-earth metal oxides ..... 9 1.5 Observations regarding the development of La<sub>2</sub>O<sub>3</sub> films ..... 11 1.6 Motivations for using $La_2O_3$ as high-k material ..... 18 1.7 Objectives and organization of this study 20

### CHAPTER 2 FABRICATION OF DEVICES, PHYSICAL CHARACTERIZATION AND RELIABILITY MEASUREMENT TECHNIQUES ..... 27

References

24

| 2.1 Intro                                      | duction                                                    |                                               | 28 |  |

|------------------------------------------------|------------------------------------------------------------|-----------------------------------------------|----|--|

| 2.2 MO                                         | S capacitor a                                              | and MOSFET fabrication                        | 29 |  |

| 2.3 Fabr                                       | ication proc                                               | ess                                           | 34 |  |

| 2.3.1                                          | Si surface                                                 | cleaning and preparation                      | 34 |  |

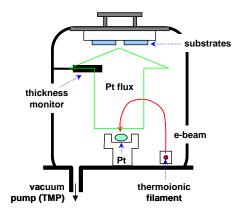

| 2.3.2                                          | E-beam ev                                                  | vaporation of La <sub>2</sub> O <sub>3</sub>  | 36 |  |

| 2.3.3                                          | .3 Low temperature annealing by rapid-thermal anneal (RTA) |                                               |    |  |

| 2.3.4 Deposition of metals for gate electrodes |                                                            | n of metals for gate electrodes               | 39 |  |

|                                                | 2.3.4.1                                                    | Thermal evaporation of Al gate electrode      | 39 |  |

|                                                | 2.3.4.2                                                    | E-beam evaporation of Pt gate electrode       | 40 |  |

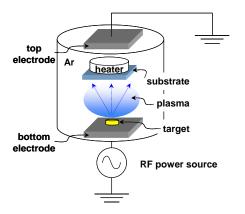

|                                                | 2.3.4.3                                                    | RF-sputtering of Ta, Ru and W gate electrodes | 41 |  |

|                                                |                                                            |                                               |    |  |

| 2.3.5 Metal gate and $La_2O_3$ etching                               | 12 |

|----------------------------------------------------------------------|----|

| 2.3.6 Photolithography 4                                             | 13 |

|                                                                      | 14 |

| 2.5 Physical characterization                                        | 15 |

|                                                                      | 15 |

| 2.5.2 Transmission electron microscopy 4                             | 17 |

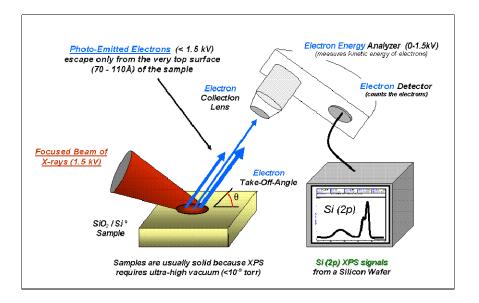

| 2.5.3 X-ray photoelectron spectroscopy (XPS) 4                       | 19 |

| 2.6 Electrical characterization 5                                    | 51 |

|                                                                      | 52 |

| 2.6.2 Ig-Vg measurement 5                                            | 53 |

| 2.6.3 Threshold voltage (Vth) determination                          | 53 |

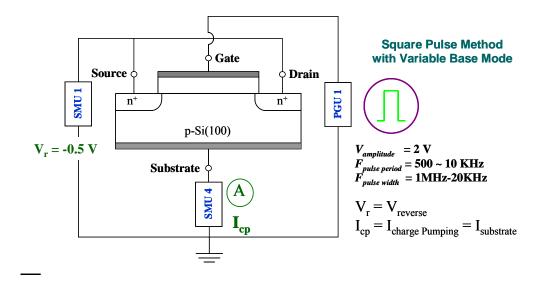

| 2.6.4 Charge pumping for interface-state density (Dit) measurement 5 | 54 |

| 1                                                                    | 56 |

| 2.7.1 TZDB and TDDB measurements                                     | 57 |

| 2.7.2 Stress Induced Leakage Current (SILC) 5                        | 59 |

| 2.7.3 Charge pumping (CP) measurement                                | 50 |

| 2.7.4 Carrier separation (CS) measurement                            | 52 |

| References                                                           | 64 |

### CHAPTER 3 RELIABILITY OF METAL GATE-La<sub>2</sub>O<sub>3</sub> MOS CAPACITORS .. 65

| 3.1 Introduction                                                                      | 66    |

|---------------------------------------------------------------------------------------|-------|

| 3.2 Influence of post-deposition annealing (PDA)                                      | 67    |

| 3.3 Influence of post-metallization annealing (PMA)                                   | . 69  |

| 3.4 Evaluation of the metal gate electrode material                                   | . 72  |

| 3.5 C-V and I-V characterization                                                      | 78    |

| 3.6 Breakdown and reliability of metal gate–La <sub>2</sub> O <sub>3</sub> thin films |       |

| after post-deposition annealing in N <sub>2</sub>                                     | . 84  |

| 3.7 Charge trapping characteristics of W-La <sub>2</sub> O <sub>3</sub> -nSi MOSCAP   |       |

| after post-metallization annealing in N <sub>2</sub>                                  | . 97  |

| 3.8 Degradation and breakdown of W-La <sub>2</sub> O <sub>3</sub> stack               |       |

| after post metallization annealing in N <sub>2</sub>                                  | . 126 |

| 3.8.1 Observations regarding breakdown of La <sub>2</sub> O <sub>3</sub>              |       |

| 3.9 La <sub>2</sub> O <sub>3</sub> post-breakdown I-V and I-t characteristics         | 138   |

| 3.9.1 Switching and noisy behavior of Ig during stress                                | . 138 |

| 3.9.2 Propagation of the breakdown event                                              | . 140 |

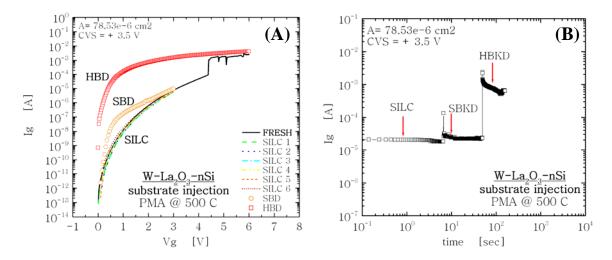

| 3.9.3 SILC-SBD-HBD of La <sub>2</sub> O <sub>3</sub> -gated MOSCAP                    | . 142 |

| 3.10 Summary                                                                          | . 143 |

| References                                                                            | . 146 |

| CHAPTER 4 RELIABILITY OF TUNGSTEN–La <sub>2</sub> O <sub>3</sub> MOS TRANSISTORS      | 154 |

|---------------------------------------------------------------------------------------|-----|

| 4.1 Introduction                                                                      | 155 |

| 4.2 Threshold voltage shift ( $\Delta V$ th)                                          | 156 |

| 4.2.1 Influence of Vth shift on drain current Id                                      | 163 |

| 4.2.2 Influence of drain voltage on Vth shift                                         | 167 |

| 4.3 Interface-state density (Dit) measurement after stress                            | 174 |

| 4.4 Comparison of degradation by substrate injection                                  |     |

| with that by gate injection                                                           | 183 |

| 4.5 Carrier separation measurements                                                   | 186 |

| 4.6 Carrier separation and Vth measurements of W-La <sub>2</sub> O <sub>3</sub> gated |     |

| MOSFET structures after electrical stress                                             | 197 |

| 4.7 Summary                                                                           | 203 |

|                                                                                       | 206 |

# CHAPTER 5MODELS FOR DEGRADATION AND<br/>BREAKDOWN MECHANISMS OF<br/>METAL/La2O3-GATED MOS DEVICES209

| 5.1 | Intro  | luction                                                                                           | 210 |

|-----|--------|---------------------------------------------------------------------------------------------------|-----|

| 5.2 | Carri  | er injection in the La <sub>2</sub> O <sub>3</sub> -SiO <sub>2</sub> system                       | 212 |

| 5.3 | Trap   | creation and interface-state generation                                                           | 217 |

| 5.4 | Failu  | re modes for degradation of La <sub>2</sub> O <sub>3</sub> -SiO <sub>2</sub> stack                | 218 |

|     | 5.4.1  | Stress-induced leakage current SILC                                                               | 219 |

|     | 5.4.2  | Charge trapping-detrapping degradation                                                            | 222 |

|     | 5.4.3  | Soft-breakdown (SBD)                                                                              | 223 |

|     | 5.4.4  | Hard-breakdown (HBD)                                                                              | 224 |

|     | 5.4.5  | Progressive breakdown (PBD)                                                                       | 225 |

| 5.5 | Towa   | rds a unified vision of breakdown in La <sub>2</sub> O <sub>3</sub> -SiO <sub>2</sub> dual layers | 231 |

| Ref | erence | s                                                                                                 | 234 |

### CHAPTER 6 COMPARISON OF THE RELIABILITY

| in in i bit o | 000000000000000000000000000000000000000                 |                            |     |     |

|---------------|---------------------------------------------------------|----------------------------|-----|-----|

|               | FOR La <sub>2</sub> O <sub>3</sub> AND HfO <sub>2</sub> | 2-BASED GATE OXIDES        |     | 237 |

|               |                                                         |                            |     |     |

| 6.1 Main r    | eliability results for Hf-b                             | ased oxides                |     | 238 |

| 6.2 Compa     | rison of reliability betwe                              | en La2O3 and Hf-based oxid | les | 247 |

| 6.2.1         | SILC degradation                                        |                            |     | 247 |

|               |                                                         |                            |     |     |

| 6    | 5.2.2      | Interface-states Dit generation                            | 248 |

|------|------------|------------------------------------------------------------|-----|

| 6    | 5.2.3      | Threshold voltage Vth shift                                | 249 |

| 6    | 5.2.4      | Time to breakdown t <sub>bd</sub>                          | 249 |

| 6    | 5.2.5      | Breakdown models for substrate and gate injection          | 250 |

| 6.3  | Remaini    | ng problems for the                                        |     |

|      | reliabilit | y of La <sub>2</sub> O <sub>3</sub> gate insulator MOSFETs | 253 |

| 6.4  | Summar     | y                                                          | 255 |

| Refe | erences    | -<br>                                                      | 256 |

| CHAPTER 7  | CONCLUSIONS               |      | 259 |

|------------|---------------------------|------|-----|

| 7.1 Conclu | usions                    |      | 260 |

| 7.2 Recon  | nmendations for future wo | orks | 267 |

| List of publications and presentations | <br>269 |

|----------------------------------------|---------|

|                                        |         |

|                                        |         |

| Acknowledgements                       | <br>272 |

# List of tables

| Table 1.1 | Scaling rules for constant-field scaling.                                                          |

|-----------|----------------------------------------------------------------------------------------------------|

| Table 1.2 | Physical properties of the metals used in this thesis.                                             |

| Table 2.1 | Sources and related effects of various contaminations.                                             |

| Table 3.1 | Obtained reliability data depending on the severity of the applied stress.                         |

| Table 6.1 | Summary of the reliability results for $HfO_2$ and $La_2O_3$ -gated MOS devices.                   |

| Table 6.2 | Summary of the reliability results for $HfO_2$ and $La_2O_3$ -gated MOS devices when $EOT < 1nm$ . |

# List of figures

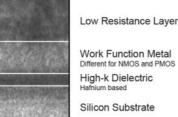

- Fig. 1.1 Cross-sectional sketch to show that the MOSFET gate capacitance Cg is made up of three capacitances in series: the oxide capacitance Cox, the capacitance due to the poly-Si depletion effect  $C_{pd}$  and a capacitance due to the finite thickness of the conducting channel  $C_{inv}$ .

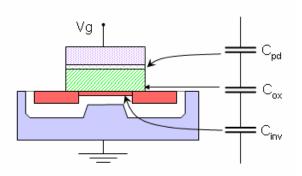

- Fig. 1.2 Schematic of direct tunneling through a  $SiO_2$  layer and the more difficult tunneling through a thicker layer of high-k oxide.

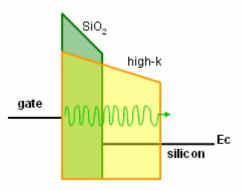

- Fig. 1.3 (A) Static dielectric constant versus band gap for candidate gate oxides.(B) Band gap for the REO of the lanthanide series.

- Fig. 1.4 Identification of some of the main problems to be solved for the posterior development of La<sub>2</sub>O<sub>3</sub>-based high-k materials within Iwai laboratory.

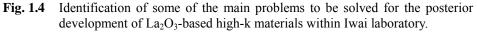

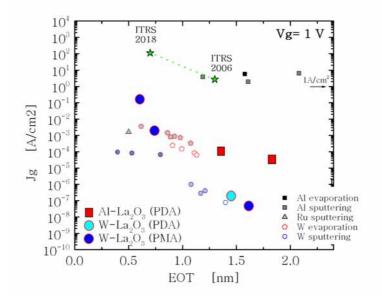

- Fig. 1.5 Gate leakage current density versus EOT at Vg= 1 V for high-k materials. Several other high-k dielectric materials are compared to  $La_2O_3$  results obtained at Iwai Lab.

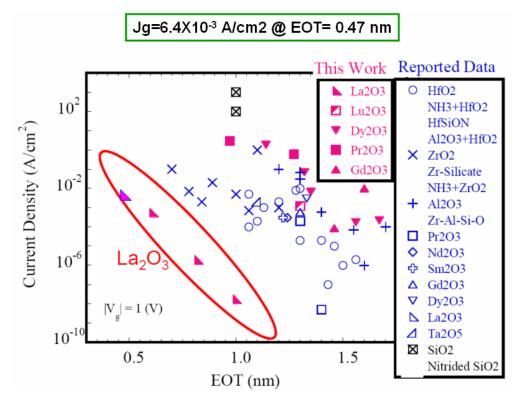

- Fig. 1.6 Effective mobility versus effective electric field for La<sub>2</sub>O<sub>3</sub>-gated n-channel MOSFET. Very high electron mobility along with very low interface-states density Dit was obtained.

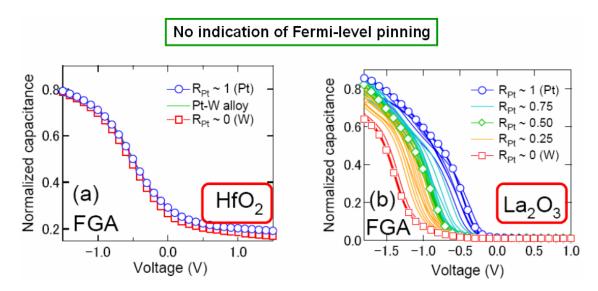

- Fig. 1.7 Normalized capacitance versus gate voltage for HfO<sub>2</sub> and La<sub>2</sub>O<sub>3</sub>-gated MOS devices on silicon. Fermi level pinning is observed only for the HfO<sub>2</sub>-based MOS device samples.

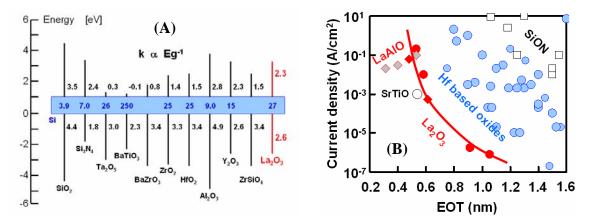

- Fig. 1.8 (A) Band offsets of several high-k candidates with silicon. Band offsets for La<sub>2</sub>O<sub>3</sub> are shown in red.

(B) Gate leakage current density of La<sub>2</sub>O<sub>3</sub>-based oxides compared to Hf-based oxides.

- Fig. 1.9 Outline and organization of this dissertation.

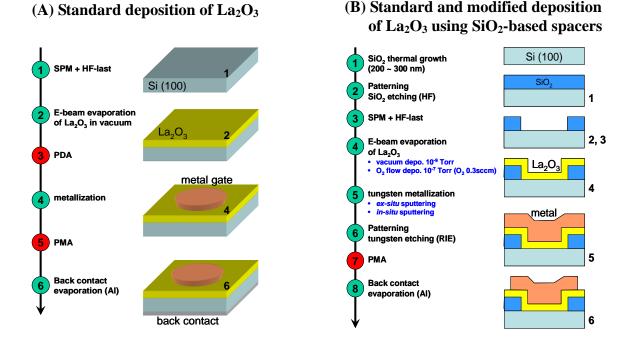

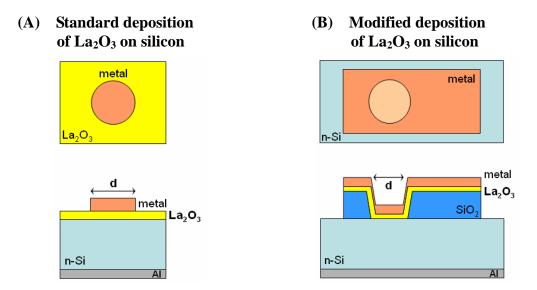

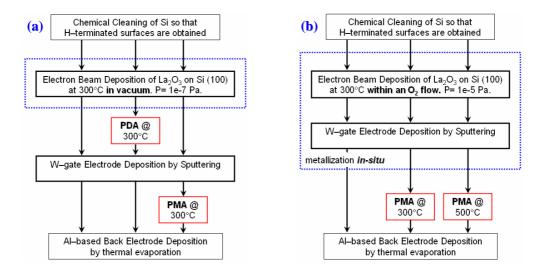

- Fig. 2.1 (A) Standard deposition of La<sub>2</sub>O<sub>3</sub> for the fabrication of MOS capacitors.

(B) Use of SiO<sub>2</sub>-based spacers for the standard and modified deposition of La<sub>2</sub>O<sub>3</sub>.

- Fig. 2.2 (A) Top and cross-sectional views of MOS capacitors after standard deposition of La<sub>2</sub>O<sub>3</sub>.

(B) Top and cross-sectional views of MOS capacitors after deposition of La<sub>2</sub>O<sub>3</sub> using SiO<sub>2</sub>-based spacers in order to reduce exposure to moisture through lateral regions of gate area.

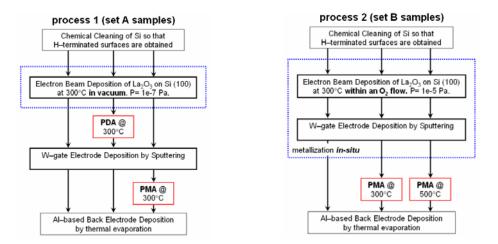

- Fig. 2.3 (A) Simplified process flow for La<sub>2</sub>O<sub>3</sub>-gated MOS capacitors after standard deposition.

(B) Simplified process flow for La<sub>2</sub>O<sub>3</sub>-gated MOS capacitors after modified deposition.

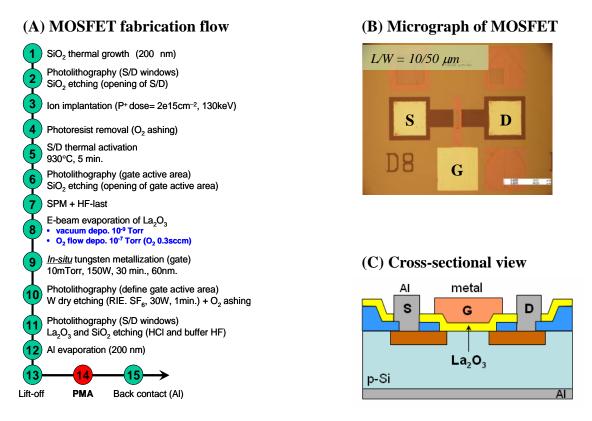

- Fig. 2.4 (A) La<sub>2</sub>O<sub>3</sub>-gated MOSFET fabrication flow (only in-situ metallization and PMA processing).

(B) Micrograph of W-La<sub>2</sub>O<sub>3</sub> gated MOSFET structure (L/W = 10/50 μm).

(C) Cross-sectional view of the MOSFET structure shown in (B).

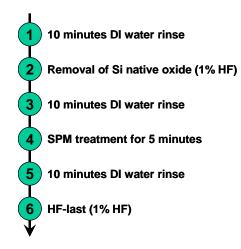

- Fig. 2.5 Si wafer cleaning and surface preparation steps.

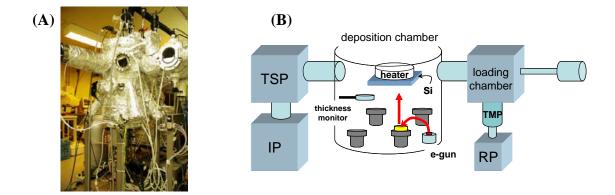

- Fig. 2.6 (A) Photograph of MBE chamber 1 used for the deposition of La<sub>2</sub>O<sub>3</sub> on Si.(B) Schematic of the La<sub>2</sub>O<sub>3</sub> deposition within MBE chamber with UHV.

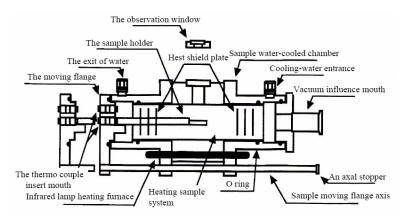

- Fig. 2.7 Schematic drawing of MILA-3000 RTA system.

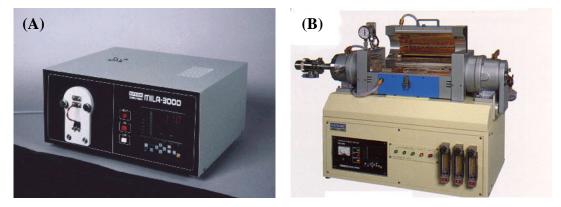

- Fig. 2.8 (A) Photograph of RTA system MILA-3000 used for the annealing of La<sub>2</sub>O<sub>3</sub> on silicon.

(B) Photograph of RTA system QHC-P610C used for the annealing of La<sub>2</sub>O<sub>3</sub> on silicon.

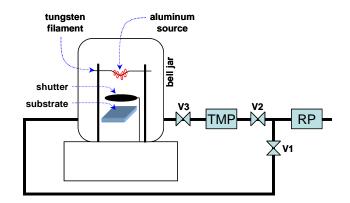

- Fig. 2.9 Schematic drawing of bell-jar type thermal evaporator system.

- Fig. 2.10 Schematic drawing of Pt-based e-beam evaporation system.

- Fig. 2.11 Schematic drawing of a typical RF sputtering system.

- Fig. 2.12 Photolithography process flow.

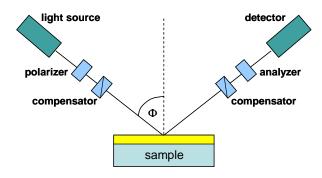

- Fig. 2.13 Schematic setup of an ellipsometry experiment.

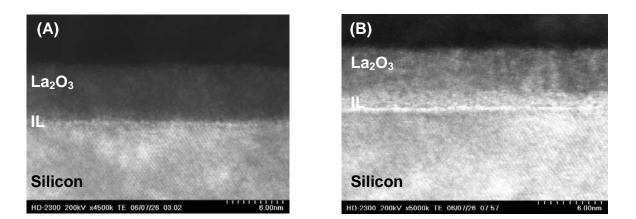

- Fig. 2.14 (A) TEM of W-La<sub>2</sub>O<sub>3</sub> without O<sub>2</sub> flow during deposition (as-depo).

(B) TEM of W-La<sub>2</sub>O<sub>3</sub> with O<sub>2</sub> flow during deposition (as-depo).

- Fig. 2.15 Basic components of a monochromatic XPS system.

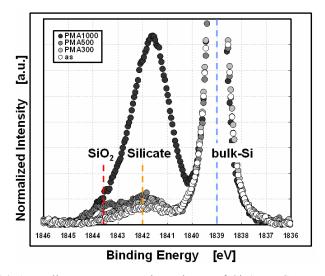

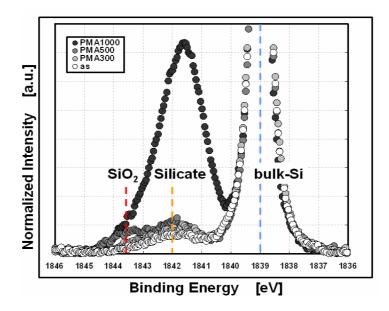

- Fig. 2.16 Annealing temperature dependence of Si 1s XPS spectrum of La<sub>2</sub>O<sub>3</sub> deposited within oxygen flow. A La-silicate IL formation is present for all samples whereas an additional SiO<sub>2</sub>-based IL formation appears for PMA at 500°C.

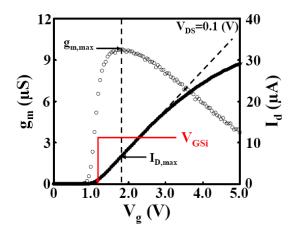

- Fig. 2.17 Linear extrapolation for Vth extraction from Id-Vg curve.

- Fig. 2.18 Charge pumping measurement setup for the extraction of Dit.

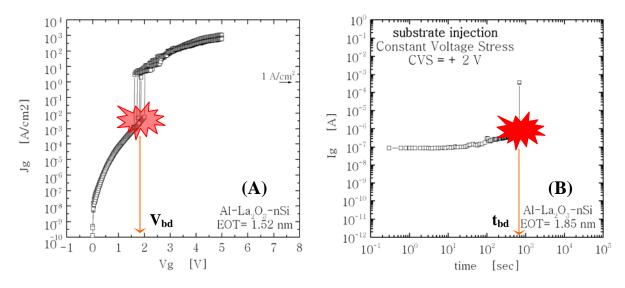

- Fig. 2.19 (A) TZDB I-V plot. Vg increases until La<sub>2</sub>O<sub>3</sub> reaches breakdown at V<sub>bd</sub> the breakdown voltage.

(B) TDDB I-t plot. For a fixed Vg, Ig evolves with time until breakdown occurs at t<sub>bd</sub>.

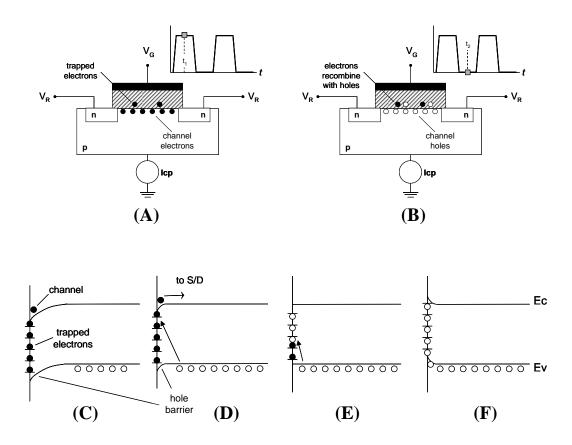

- Fig. 2.20 (A-F) Device cross-sections and energy band diagrams for charge pumping measurements. The figures are explained in the text.

- Fig. 2.21 (A) CS measurement for nMOSFETs in inversion (positive CVS). Both electron and hole current components are detected at the gate and substrate respectively.

(B) CS measurement for pMOSFETs in inversion (negative CVS). Even though both electrons and holes tunnel simultaneously through the gate oxide, only the hole current component is illustrated flowing through the oxide for clarity purposes. Both hole and electron current components are detected at the gate and substrate respectively.

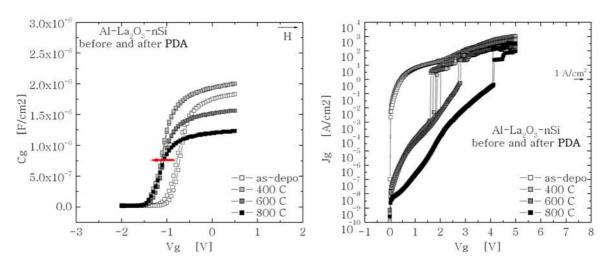

- Fig. 3.1 C-V characteristics of Al-La<sub>2</sub>O<sub>3</sub> gated MOSCAP after PDA in N<sub>2</sub> ambient at different temperatures (300°C– 800°C).

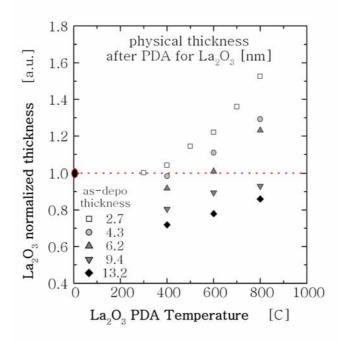

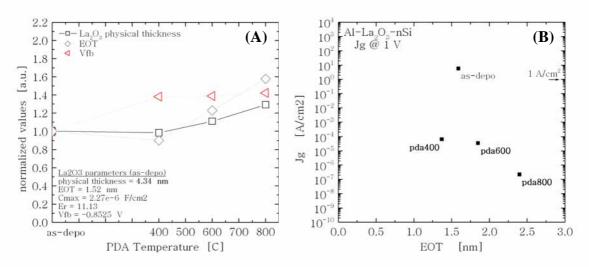

- Fig. 3.2 Changes in physical thickness for La<sub>2</sub>O<sub>3</sub> after several PDA temperatures.

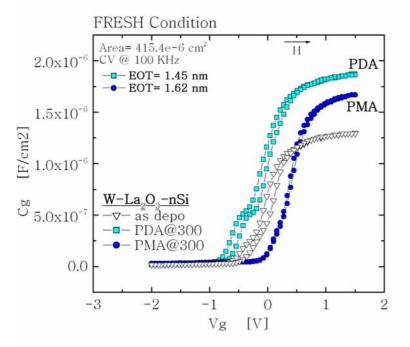

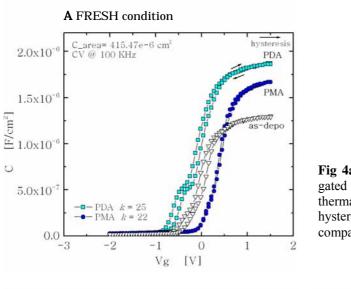

- Fig. 3.3 W-La<sub>2</sub>O<sub>3</sub> gated MOSCAP before and after thermal treatment in N<sub>2</sub> ambient at 300°C. PDA and PMA thermal treatments are both compared to the as-depo condition.

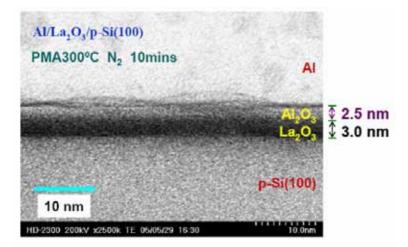

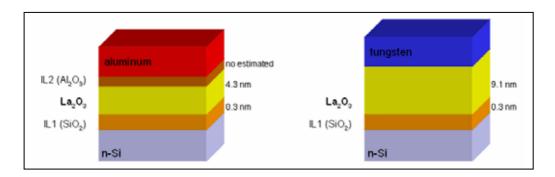

- Fig. 3.4 TEM of an aluminum-gated La<sub>2</sub>O<sub>3</sub> MOSCAP after PMA in N<sub>2</sub> at 300°C (10 min.). The existence of a low-k Al<sub>2</sub>O<sub>3</sub>-based IL at the Al–La<sub>2</sub>O<sub>3</sub> interface is shown.

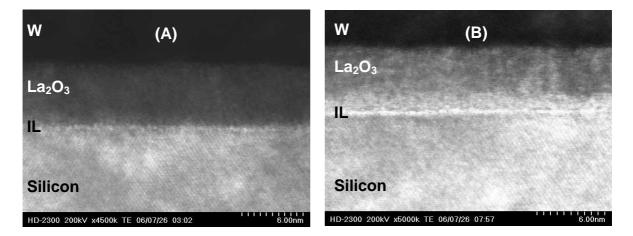

- Fig. 3.5 (A) TEM of W-La<sub>2</sub>O<sub>3</sub> without O<sub>2</sub> flow during deposition (as-depo).

(B) TEM of W-La<sub>2</sub>O<sub>3</sub> with O<sub>2</sub> flow during deposition (as-depo).

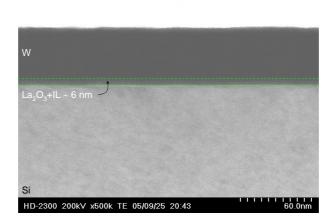

- Fig. 3.6 TEM of W-La<sub>2</sub>O<sub>3</sub> without  $O_2$  flow during deposition (PMA).

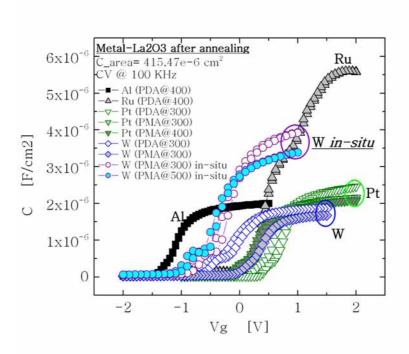

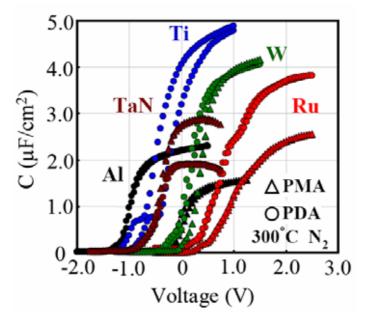

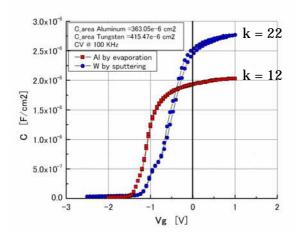

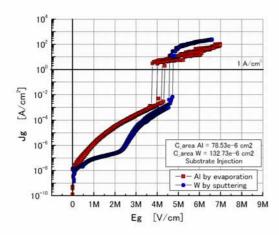

- Fig. 3.7 C-V characteristics of La<sub>2</sub>O<sub>3</sub> gated with different gate metals.

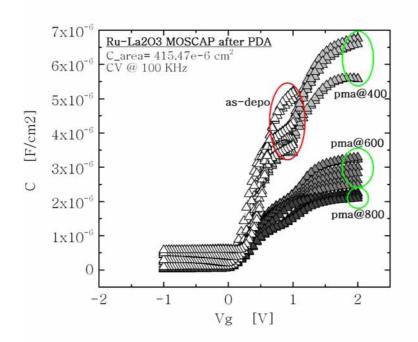

- Fig. 3.8 C-V characteristics of Ru-gated  $La_2O_3$  before and after PDA at different temperatures. The large variations between samples exist even for the PDA@800°C samples.

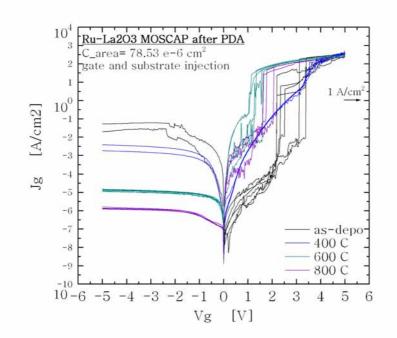

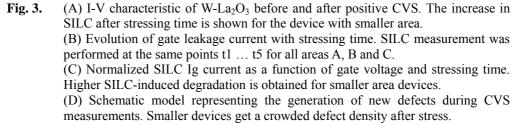

- Fig. 3.9 J-V characteristics of Ru-gated  $La_2O_3$  before and after PDA at different temperatures. It is clearly seen that there is almost no reproducibility in Jg even for the same sample.

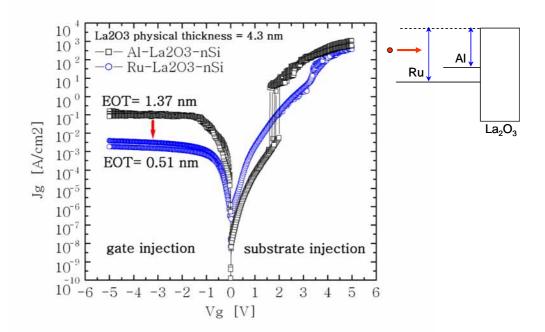

- Fig. 3.10 J-V characteristics of Al and Ru-gated La<sub>2</sub>O<sub>3</sub> after PDA in N<sub>2</sub> at 400°C. The use of a higher work function metal leads to a reduced density of leakage current (gate injection). The inset shows the difference in barrier height for electrons during gate injection.

- Fig. 3.11 C-V characteristics of metal–La<sub>2</sub>O<sub>3</sub> after PDA/PMA in N<sub>2</sub>. Even though lower EOT can be achieved with other metals, W gets the more stable and reproducible characteristics.

- Fig. 3.12 C-V and I-V characteristics of Al–La<sub>2</sub>O<sub>3</sub> before and after PDA in N<sub>2</sub>.

- Fig. 3.13 (A) Variation of some physical and electrical characteristics of Al–La<sub>2</sub>O<sub>3</sub> stacked structure before and after PDA in N<sub>2</sub>.

(B) Jg-EOT plot for the same Al–La<sub>2</sub>O<sub>3</sub> stacked structure.

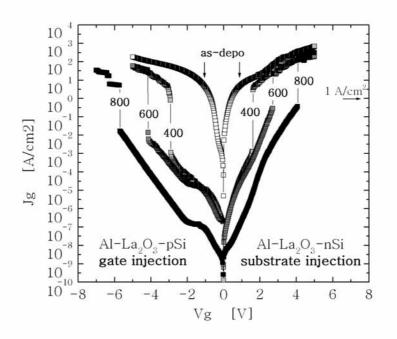

- Fig. 3.14 J-V characteristics for Al-gated  $La_2O_3$  stacked on p and n-type silicon.  $La_2O_3$  physical thickness ~ 4.3 nm for as-depo condition on both Si substrates.

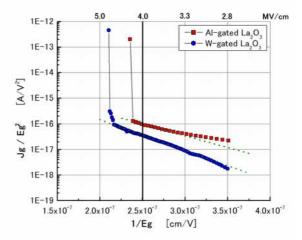

- Fig. 3.15 Jg-EOT plot for some of the Metal-La<sub>2</sub>O<sub>3</sub> stacked MOS structures evaluated in this dissertation. Jg is taken at |1V|.

- Fig. 3.16 (A) I-V data for Ru-La<sub>2</sub>O<sub>3</sub>-stacked MOSCAP showing the Ig switching characteristic during TZDB stressing conditions. The trapping-detrapping processes occur before the HBD condition is reached.

(B) I-t characteristic for W-La<sub>2</sub>O<sub>3</sub> MOSCAP. Here, the trapping-detrapping processes occur after the HBD condition. The switching characteristic of Ig can be confirmed once the La<sub>2</sub>O<sub>3</sub>-IL stack breakdown.

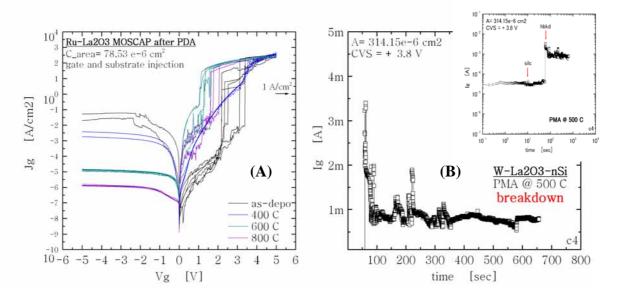

- Fig. 3.17 (A) I-V characteristic of La<sub>2</sub>O<sub>3</sub>-gated MOSCAP showing the propagation of the breakdown spot as a gradual "jump"-like increase in leakage current Ig.

(B) I-t characteristic for a different sample with the same structure in (A). The propagation of the breakdown spot is clearly visible as the tiny jumps in Ig after breakdown.

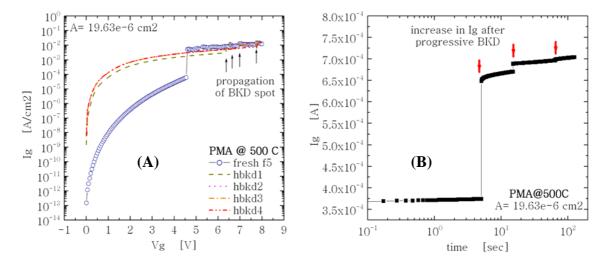

- Fig. 3.18 (A) I-V characteristic of La<sub>2</sub>O<sub>3</sub>-gated MOSCAP. The effect of the severity of stress on gate leakage current Ig is clearly shown (in real devices lower stress fields are expected).

(B) I-t characteristic showing the effect of stress on the evolution of leakage current with time. The occurrences of SILC-SBD-HBD are highlighted both in the I-V and I-t data.

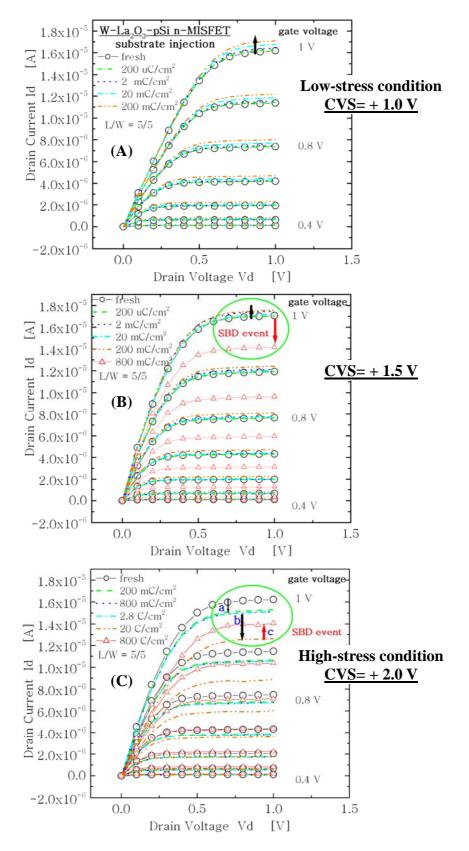

- Fig. 4.1 (A) ΔVth after CVS= 1V. Vth totally shifts to the left side in proportion to injected charge Qinj.

(B) ΔVth after CVS= 1.5V. Vth continues to shift to left side until a SBD event takes place.

(C) ΔVth after CVS= 2V. Vth increases to more positive values until SBD events changes this trend.

- Fig. 4.2 Vth shift versus injected charge density Qinj for W-La<sub>2</sub>O<sub>3</sub> gated nMOSFETs after low to high positive stressing CVS conditions.

- Fig. 4.3 (A) ΔVth after CVS= -1.5V. Vth totally shifts to the left side in proportion to injected charge Qinj.

(B) ΔVth after CVS= -2.0V. Vth continues to shift to left side as expected for pMOSFETs.

(C) ΔVth after CVS= -3.0V. ΔVth gradually increases during this higher CVS condition.

- Fig. 4.4 Vth shift versus injected charge density Qinj for W-La<sub>2</sub>O<sub>3</sub> gated pMOSFETs after low to high negative stressing CVS conditions.

- Fig. 4.5 (A) Id-Vd plot for W-La<sub>2</sub>O<sub>3</sub> gated nMOSFET before and after a positive and relatively low CVS.

(B) Id-Vd plot showing the effect that a SBD event have on drain current Id.

(C) Id-Vd plot with the expected trend in Id under high-stressing conditions and the effect of SBD.

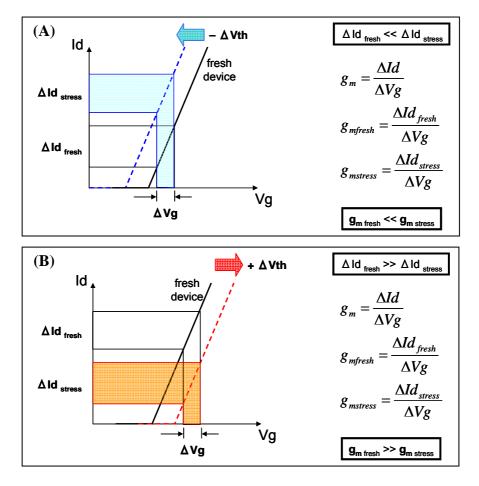

- Fig. 4.6 (A) Simplified Id-Vg diagram showing the effect of negative  $\Delta V$ th after stress. (B) Simplified Id-Vg diagram showing the effect of positive  $\Delta V$ th after stress.

- Fig. 4.7 Schematic of nMOSFET with both Vg and Vd polarization during CVS. The total gate leakage current Ig is now reduced in proportion to Vd.

- Fig. 4.8 Hot carrier generation, current components, and electron injection into the  $La_2O_3$ -IL stacked oxide structure.

- Fig. 4.9 Vth shift versus injected charge density Qinj for W-La<sub>2</sub>O<sub>3</sub> gated nMOSFETs after both low positive CVS and Vd stressing conditions.

- Fig. 4.10 Log-log plot of the data presented in fig. 4.9.

- Fig. 4.11 (A) Gate leakage current Ig versus stressing time. Ig reduces in proportion to drain voltage Vd. (B) In order to reach the same injected charge density, more time is necessary for the sample with a decreased Ig (higher Vd). The final effect is a stronger dependence of  $\Delta V$ th with Qinj.

- Fig. 4.12 Drain current Id increases with Vd until saturation occurs when the channel is cut-off at Vdsat (pinch-off condition).

- Fig. 4.13 Schematic of the charge pumping (CP) technique. CP is able to measure recombined charges at the substrate Isub=Icp.

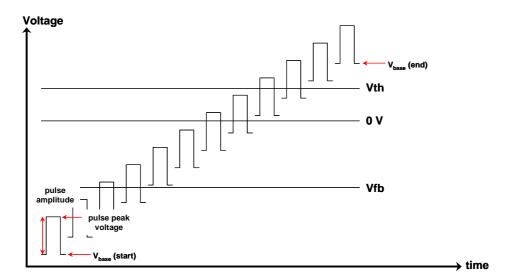

- Timing chart of square pulse method for CP measurement. Fig. 4.14

- Fig. 4.15 (A) Log-log plot of  $\Delta$ Vth versus injected charge density Qinj for nMOSFET under positive CVS. A linear relationship between  $\Delta V$ th–Qinj is observed in this plot. (B) Interface-states density Dit measured at the maximum substrate current Isub after positive stressing measurements. A log-log plot shows no correlation of  $\Delta V$ th with injected charge density. The inset shows a linear-log plot of the same data for comparison.

- Fig. 4.16 Same data as presented in fig. 4.4.

- Dit versus Qinj for pMOSFET after negative CVS. Independently of the CVS Fig. 4.17 applied, the change in Dit after stress is almost constant. The inset shows a linear-log plot of these data for comparison purposes.

- Fig. 4.18 (A) Dit-Vbase plot for W-La<sub>2</sub>O<sub>3</sub> gated pMOSFET after negative CVS = -1.5 V. (B) Dit-Vbase plot for W-La<sub>2</sub>O<sub>3</sub> gated pMOSFET after negative CVS = -2.0 V. (C) Dit-Vbase plot for W-La<sub>2</sub>O<sub>3</sub> gated pMOSFET after negative CVS = -3.0 V.

- Fig. 4.19 (A) Log-log plot of  $\Delta$ Vth versus Qinj for pMOSFET under negative CVS and FG-based PMA. As before, identical behavior for these pMOSFETs is obtained but the initial levels of Vth are slightly lower than those found in N<sub>2</sub>-based PMA devices.

(B) A log-lo plot of Dit vs. Qinj after stress shows lower levels of Dit as

compared to those found in N<sub>2</sub>-based PMA devices. It is thought that FG-based PMA is able to reduce the initial density of dangling bonds so that lower changes in Dit with stress are obtained.

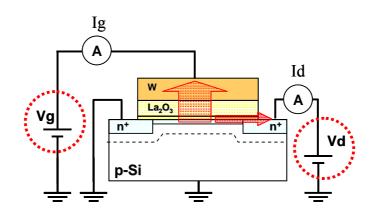

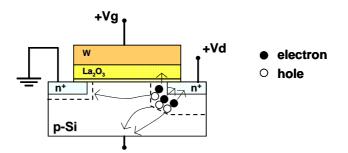

Fig. 4.20 (A) Schematic diagram showing nMOSFETs stressed with a positive CVS. The flow of both electrons and holes currents are measured at the gate and substrate respectively. (B) The energy band diagram shows that positive CVS implies injection of electrons directly from the substrate (via the inverted channel) into the IL-La<sub>2</sub>O<sub>3</sub> stacked structure.

Fig. 4.21 (A) Schematic diagram showing nMOSFETs stressed with a positive CVS. The flow of both electrons and holes currents are measured at the gate and substrate respectively. (B) The energy band diagram shows that positive CVS implies injection of electrons directly from the substrate (via the inverted channel) into the IL-La<sub>2</sub>O<sub>3</sub> stacked structure.

Fig. 4.22 (A) CS measurement for nMOSFETs in inversion (positive CVS). Both electron and hole current components are detected at the gate and substrate respectively. (B) CS measurement for pMOSFETs in inversion (negative CVS). Even though both electrons and holes tunnel simultaneously through the gate oxide, only the hole current component is illustrated flowing through the oxide for clarity purposes.

Fig. 4.23 (A) Ig versus Vg plot for nMOSFET before positive CVS (gate injection). After CS measurement, electrons were identified as the major contributors to gate leakage current. (B) After positive CVS, the Ig-Vg shape remains almost unchanged. Because of the trapping of electrons at the bulk of La<sub>2</sub>O<sub>3</sub>, Ig gets slightly lower as compared to fresh condition.

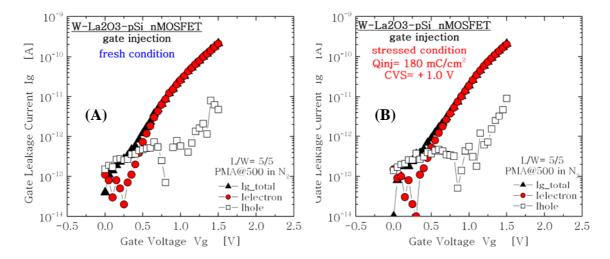

Fig. 4.24 (A) Id versus gate voltage Vg. Same as the data presented in fig. 4.1C. (B)(C)(D) CS measurement for gate leakage current under positive CVS= +2.0 V. The electron current is the main contributor to total leakage current with Ihole increasing with Qinj. (E) After a SBD event occurs, the main contributor to Ig changes from electrons to holes for low electric fields and the final effect can be seen as a net increase in Ig as well.

(F) After SBD event, Ielectron is still dominant though Ihole increases well

above its fresh value.

- Fig. 4.25 Ig-Vg plot for nMOSFET with higher Vg ramping stress. Several degradation steps occur before and after fatalistic HBD event appear.

- Fig. 4.26 (A) Plot of CS measurement of Ig vs. Vg before and after negative CVS for pMOSFET. The injection of a smaller density of injected charge did not change the major contributor to Ig.

(B) Holes still are the major contributors to Ig before and after negative CVS. The injection of a relatively higher charge density increases Ig compared to its fresh value.

(C) Similarly, at the higher CVS condition, holes are the major components of Ig after inversion of pMOSFET and the fresh levels of Ig increases after stress indicating hole trapping in the oxide.

- Fig. 4.27 (A) Evolution of gate leakage current (substrate injection) with stressing time. Ielectron is the dominant component of the total Ig. A two-step breakdown behavior is also observed.

(B) Evolution of gate leakage current (gate injection) with stressing time. Ihole is the dominant component of the total Ig. A one-step breakdown behavior is observed.

- Fig. 5.1 Schematic representation of the generation of failure modes with stressing time.

- Fig. 5.2 Schematic representation of the thinned (IL BKD) oxide approach.

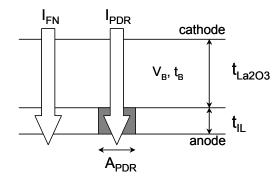

- Fig. 5.3 Schematic representation of the percolation path between electrodes and formed within both La<sub>2</sub>O<sub>3</sub> and IL lattices. For a dual-oxide, the polarization of applied stress is important to determine the "filling" of the first lattice trap sites by percolation traps and thus reach breakdown.

- Fig. 5.4 Schematic representation of the breakdown "path" followed by the injection of electrons coming from the substrate. Once the stressing continues the whole layer breaks down.

- Fig. 5.5 Schematic representation of the breakdown "path" followed by the injection of electrons coming from the gate. Once the stressing continues the whole layer breaks down.

- Fig. 5.6 SILC measurement after positive CVS for thick and thin La<sub>2</sub>O<sub>3</sub>-IL stacks.

(A) EOT= 1.5 nm (normal La<sub>2</sub>O<sub>3</sub> deposition).

(B) EOT= 0.74 nm (in-situ tungsten metallization)

- Fig. 5.7 Relative change in leakage current induced by SILC (same data as in fig. 5.6 A-B).

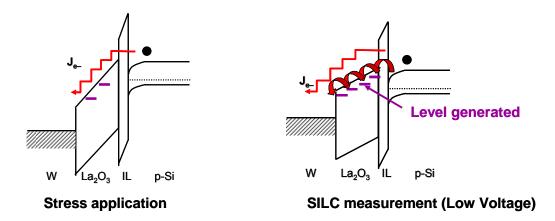

- Fig. 5.8 Left side plot shows an energy band diagram during CVS measurement (high voltage). During CVS, new energy levels of generated defects are created. Right side plot shows electrons tunneling inelastically through generated levels during SILC measurement.

- Fig. 5.9 Left side plot shows the shift in Vth for  $La_2O_3$ -gated nMOSFETs stressed under low and high positive CVS. The change in direction of  $\Delta$ Vth with stress is clear. Right side energy band diagram models the degradation phenomena occurring within the oxide stack.

- Fig. 5.10 Left side plot shows the evolution of leakage current with time under substrate injection conditions (positive CVS). At certain stressing time, the occurrence of a SBD event is detected. Right side energy band diagram models this degradation phenomenon as breakdown of the IL.

- Fig. 5.11 Left side plot shows the evolution of leakage current with time under substrate injection conditions (positive CVS). At certain stressing time, the occurrence of a HBD event is detected. Right side energy band diagram models this degradation phenomenon as total breakdown of the stacked oxide.

- Fig. 5.12 (A) Ig-Vg plot for La<sub>2</sub>O<sub>3</sub>-IL stack showing HBD characteristics and consequent propagation of the breakdown event with Vg. The post-breakdown current levels also increase in accordance to PBD.

(B) Ig-time plot for La<sub>2</sub>O<sub>3</sub>-IL stack showing HBD characteristics and consequent propagation of the breakdown event with time. During PBD, higher Ig is related to a larger size of the total breakdown spot.

- Fig. 5.13 (A) The post-breakdown leakage current for nMOSFET in inversion shows a two-step breakdown.

(B) For pMOSFET, a single-step breakdown, along with higher levels for the post-breakdown Ig is obtained.

- Fig. 5.14 (A) For substrate injection, the lateral breakdown propagation of the La<sub>2</sub>O<sub>3</sub> layer (after IL breakdown) increases the post-breakdown Ig. Opening of new breakdown spots in La<sub>2</sub>O<sub>3</sub> is also possible.

(B) In gate injection, higher post-breakdown Ig is related to the larger size in the breakdown spot within La<sub>2</sub>O<sub>3</sub>. PBD characteristics would be related to the widening/opening of same/new BKD spots.

- Fig. 5.15 (A) Ig-Vg plot for W/La<sub>2</sub>O<sub>3</sub>-IL stacked MOSCAP before and after continuous stress under substrate injection. The effect of several degradation modes on leakage current is shown.

(B) Ig-time plot for W/La<sub>2</sub>O<sub>3</sub>-IL stacked MOSCAP before and after continuous stress under substrate injection. Again, the effect of the same degradation modes on leakage current is shown.

- Fig. 6.1 Summary of the main reliability problems found for Hf-based oxides deposited on silicon. Depending on the conditions of the stressing measurements and the advance of the electrical degradation, some reliability properties will be more compromised than others.

- Fig. 6.2 SILC characteristics for several HfO<sub>2</sub>-gated MOS devices.

(A) SILC characteristic for the Pt/HfO<sub>2</sub>/Si system. EOT= 2.9 nm.

(B) SILC characteristic for the poly-Si/HfO<sub>2</sub>/Si system. EOT= 1.8 nm.

(C) SILC characteristic for the poly-Si/HfO<sub>2</sub>/Si system. EOT= 1.5 nm.

(D) SILC characteristic for the TaN/HfO<sub>2</sub>/Si system. EOT= 0.9 nm.

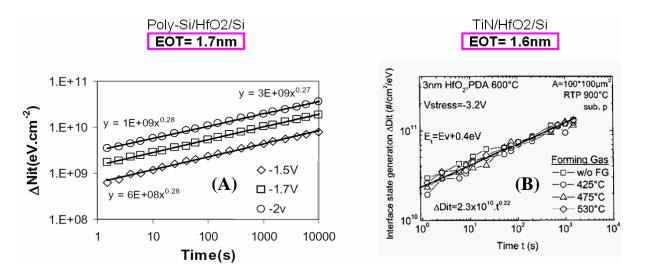

Fig. 6.3 Dit-generation characteristic for HfO<sub>2</sub>-gated MOS devices with similar EOT.

(A) Dit-generation for the poly-Si/HfO<sub>2</sub>/Si system. EOT= 1.7 nm.

(B) Dit-generation for the TiN/HfO<sub>2</sub>/Si system. EOT= 1.6 nm.

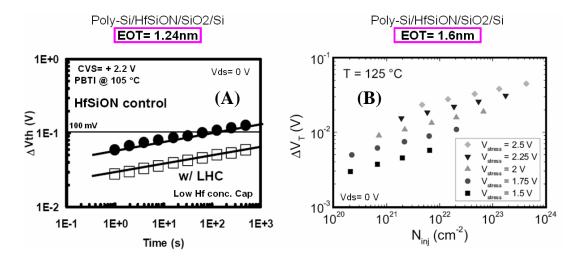

- Fig. 6.4 Vth shift characteristic for HfSiON-gated MOS devices.

(A) Vth shift for the poly-Si/HfSiON/Si system. EOT= 1.24 nm.

(B) Vth shift for the poly-Si/HfSiON/Si system. EOT= 1.6 nm.

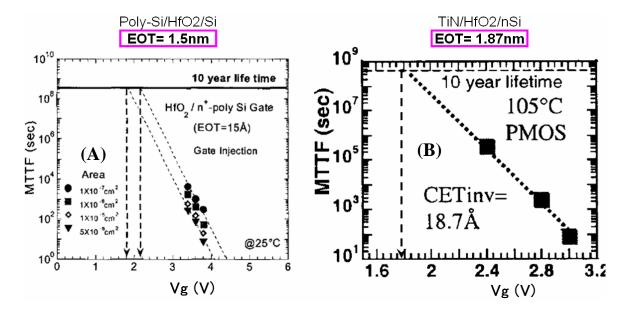

- Fig. 6.5 Lifetime extrapolation of the time to breakdown data for HfO<sub>2</sub>.

(A) Lifetime extrapolation for the poly-Si/HfO<sub>2</sub>/Si system. EOT= 1.5 nm.

(B) Lifetime extrapolation for the TiN/HfO<sub>2</sub>/Si system. EOT= 1.87 nm.

- Fig. 6.6 (A) Proposed models for the degradation of HfO<sub>2</sub>-gated MOS devices.

(B) When the degradation continues, the breakdown is modeled differently depending mainly on the polarity of the stress applied (gate and substrate injection of electrons)

- Fig. 6.7 Structural features of the metal gate/high-k (Hf-based) stacks used by Intel and which is scheduled for commercial production of MOSFETs in the 45nm node during this year.

- Fig. 6.8 (A) Less SILC degradation is found for La<sub>2</sub>O<sub>3</sub> compared to HfO<sub>2</sub>-gated MOS devices.

(B) SILC degradation for Hf-based oxides only. Exponential increase in Jg is clearly observed.

- Fig. 6.9 Comparison of the observed Dit generation between HfO<sub>2</sub> and La<sub>2</sub>O<sub>3</sub>-gated devices during stress.

- Fig. 6.10 Comparison of the observed Vth shift between HfO<sub>2</sub> and La<sub>2</sub>O<sub>3</sub>-gated devices during stress.

- Fig. 6.11 Comparison of the observed time to breakdown data between  $HfO_2$  and  $La_2O_3$ -gated devices

- Fig. 6.12 (A) Comparison of the breakdown models for HfO<sub>2</sub> and La<sub>2</sub>O<sub>3</sub> during substrate injection conditions.

(B) Comparison of the breakdown models for HfO<sub>2</sub> and La<sub>2</sub>O<sub>3</sub> during gate injection conditions.

## Abstract

This study discusses charge trapping effects and the dielectric reliability of metal-gated La<sub>2</sub>O<sub>3</sub> stacked dielectrics. It will be shown that the gate stacks suffer from severe charge trapping, which causes adverse effects on the characteristics of La<sub>2</sub>O<sub>3</sub>-gated MOS devices like flat band Vfb and threshold voltages Vth shifts after stress. On the other hand, the lifetime projection of La<sub>2</sub>O<sub>3</sub> after time-dependent dielectric breakdown measurements (TDDB) guarantees a 10 years operation period for La<sub>2</sub>O<sub>3</sub>-gated MIS devices at low gate voltages before breakdown. That latter result encourages us to look for alternative ways to minimize the electrical degradation found in La<sub>2</sub>O<sub>3</sub>-gated MIS devices after stress, whether by modifications in the deposition process of  $La_2O_3$  or by introducing post-deposition processes like thermal treatments before and after the metallization step. Moreover, the problem of IL formation atop the silicon substrate still is a great challenge to be solved since La<sub>2</sub>O<sub>3</sub> tends to develop this lower-k IL when deposited on silicon, thus increasing the final equivalent oxide thickness (EOT) of the whole high-k/IL stacked structure. Because of this La<sub>2</sub>O<sub>3</sub>-IL stack formation, the deterioration of the oxide stack will depend on the nature of these layers as well as the nature of the injected species (electrons or holes) under stress. From carrier separation measurements, substrate electron injection results in a shorter time to oxide breakdown t<sub>bd</sub> as compared to gate electron injection. Nevertheless, longer t<sub>bd</sub> for La<sub>2</sub>O<sub>3</sub>/IL as well as smaller degradation of its electrical characteristics with time were obtained after improving the deposition process and post-deposition process for this oxide. Specifically, an in-situ metallization for La<sub>2</sub>O<sub>3</sub> minimizes the exposition of La<sub>2</sub>O<sub>3</sub> surface to environment and post-metallization annealing (PMA), can help to reduce the damage introduced into La<sub>2</sub>O<sub>3</sub> and its interfaces after the deposition by sputtering of the gate electrode, thus increasing the final reliability of  $La_2O_3$ -gated MOS devices. Further improvements on the physical characteristics of  $La_2O_3$ will increase its reliability so that this dielectric material will have good chances to replace conventional gate oxides well beyond the 45 nm node since the fabrication of  $La_2O_3$ -gated MOS devices with EOT < 1 nm has been already demonstrated.

# Introduction to metal gate/high-k thin film stacked structures

- 1.1 Brief summary of the history of semiconductor devices

- 1.2 Beyond SiO<sub>2</sub>-based CMOS device scaling

- 1.3 Requirements for metal gates and high-k materials

- 1.4 Review of rare-earth metal oxides

- 1.5 Observations regarding the development of La2O3 films

- 1.6 Motivations for using  $La_2O_3$  as high-k material

- 1.7 Objectives and organization of this study

References

### 1.1 Brief summary of the history of semiconductor devices

n 1947, W. Schockley, J. Bardeen and W. H. Brattain invented the bipolar transistor [1] at Bell Laboratories, Murray Hill, New Jersey. The invention of the transistor, a solid state amplifier, resulted in great efforts in the field of semiconductor devices. The integration of semiconductor devices on a single chip was one of the consequences of these combined efforts. J. Kilby at Texas Instruments first demonstrated the concept of Integrated Circuits (IC) in 1959 [2]. This concept together with the fabrication of the first Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) by D. Kahng and M. M. Attala in 1960 [3] provided the basis for the evolution of the microelectronics industry. The principle of a surface field effect transistor was already proposed in the early 30's by Lilienfeld and Heil [4]. The experimental verification of the surface field effect, however, could not be demonstrated for more than 30 years. Since then, the MOSFET became by far the most important electronic device for very large scale integrated (VLSI) circuits such as microprocessors and semiconductor memories. The minimum device dimension has been reduced from ~10 µm in the 1960's to sub µm features in the 1990's. Currently, researches are being conducted towards integration of sub 45 nm CMOS devices by several groups all around the world. The introduction of alternative gate dielectrics with a high dielectric constant ( $\varepsilon$ ), or so called *high-k* dielectrics, is a part of these research efforts.

### 1.2 Beyond SiO<sub>2</sub>-based CMOS device scaling

The fundamental building blocks for all the silicon chips — transistors — have continuously kept on track with Moore's Law for over forty years [5]. This law states that the density of transistors (namely MOSFETs) that can be "crammed" into a single integrated circuit is doubled through advances in technology and design every 18 months or quadrupled every 3 years, but as with any rapidly developing field, a limit will eventually

be reached. In the early 1980's the minimum possible dimension was predicted to be approximately 0.5 µm. Ten years later, the predicted minimum dimension had decreased to about 0.1 µm and now, in the early 21<sup>st</sup> century, a frequently quoted limit is roughly 25 nm. Since its invention, MOSFETs have displaced bipolar transistors to become the most extensively used solid-state devices. MOSFETs have several advantages over bipolar transistors and it is easier to build them in dense arrays. They also typically consume less power than the bipolar integrated circuits do. Because of their simpler fabrication process, higher density, and low power consumption, MOSFETs are widely used in both memory circuits (totally displacing bipolar memories) and in logic circuits. The high-volume production of MOSFET IC has, in turn, financed enormous research programs to improve MOSFET performance; the ongoing research continues to reduce the device size, allowing more devices on a chip, and increasing the operation frequency. Dennard et al. [6] presented an influential systematic study of the impact of technology scaling (process of reducing the sizes of both active devices and passive elements in order to improve both packing density and circuit speed) on circuit performance. They proposed *constant-field* scaling rules, in which dimensions are changed in such a manner that the internal electric fields within the transistor remain (as close as possible) unchanged in the devices. A summary of the constant-field scaling rules is given in table 1.1.

| Physical parameters          | Scaling factor |

|------------------------------|----------------|

| Surface dimensions, L        | 1/K            |

| Vertical dimensions, tox, Xj | 1/K            |

| Impurity concentrations      | K              |

| Currents, voltages           | 1/K            |

| Current density              | K              |

| Capacitance (per unit area)  | K              |

| Transconductance             | 1              |

| Circuit delay time           | 1/K            |

| Power dissipation            | $1/K^2$        |

| Power density                | 1              |

| Power-delay product          | $1/K^{3}$      |

**Table 1.1** Scaling rules for constant-field scaling [6].

Scaling rules of the type formulated by Dennard et al. are inherently of limited direct use because effects that can be neglected in larger devices become first significant, and then dominant as device dimensions continues to shrink. With the sub-micrometer dimension channel lengths that now characterize MOSFETs, device performance is completely dominated by high-electric field effects that are inconsequential in larger-dimension devices. So that instead of being strictly observed, the scaling rules have functioned more as a guide to size reduction in integrated circuits. In fact, the scaling of both passive and active devices has been influenced more by fabrication-technology limitations and device functionality than by the application of algebraic scaling factors. Reducing the gate oxide thickness t<sub>ox</sub>, helps increase the desired coupling of the gate voltage to the channel charge, and every new generation of CMOS technology uses a thinner gate oxide. However, this scaling of oxide thickness is limited. When the oxide thickness becomes extremely thin, direct tunneling (DT) of electrons through it causes significant gate current to flow and reduces input impedance. The acceptable limit for gate oxide scaling appears to be about 2.5 nm without significant increase of the DT leakage current (though  $Intel^{M}$  announced a mere 1.2 nm that corresponds with only five atomic-layer thick for its 90 nm process). In addition to the limitation resulting from DT, the scaling of gate oxide below 2.5 nm cannot effectively increase the gate coupling because of carrier depletion in the poly-silicon gate electrode and the finite thickness of the inversion layer (channel) in the silicon, as illustrated in figure 1.1

**Fig. 1.1** Cross-sectional sketch to show that the MOSFET gate capacitance Cg is made up of three capacitances in series: the oxide capacitance Cox, the capacitance due to the poly-Si depletion effect Cpd and a capacitance due to the finite thickness of the conducting channel Cinv.

The combination of polysilicon depletion and inversion layer capacitance can significantly reduce the MOSFET current drive. The overall capacitance  $C_{tot}$  of capacitors in series is dominated by the layer with the lowest capacitance as shown in equation 1.1, so material interfaces must be tightly controlled in order to control gate stack capacitance.

$$Ctot_{series} = \frac{1}{\left(1/C_1 + 1/C_2 + 1/C_3 + \cdots\right)}$$

(1.1)

To increase gate coupling, some new approaches are being investigated. High dielectric constant (high permittivity or high-k) gate dielectrics are being actively explored, as well as gates made of metals that can eliminate the gate-depletion effect. Although these new materials and technologies have not yet become a part of production processes, their use will be necessary in future CMOS technology generations. The scaling requirements for future CMOS technologies are generally guided by the International Technology Roadmap for Semiconductors (ITRS) [7], where the introduction of alternative gate dielectrics is predicted for 2007 depending on the technology applications. The advantage for using high-k insulators is obvious. The gate oxide capacitance per unit area is given by:

$$\frac{Cg}{A} = \frac{\mathcal{E}_{ox}}{t_{ox}} \tag{1.2}$$

Where  $\varepsilon_{ox}$  and  $t_{ox}$  are the relative permittivity and thickness of the oxide respectively. Increasing  $\varepsilon_{ox}$ , rather than continuing to reduce  $t_{ox}$ , avoids the problem of direct tunneling, since tunneling of leakage current through the dielectric layer exponentially increases as its thickness decreases. Nevertheless, making the dielectric ever thinner is necessary in order to meet increasing performance goals. When the gate dielectric of transistors is made thinner, its insulating quality decreases and current leaks through it. Uncontrolled, this conduction causes the transistor to stray from its purely "on" and "off" state and into an "on" and "leaky off" behavior. A schematic showing the problem of DT current flowing through thinner SiO<sub>2</sub> films is shown in figure 1.2. Difficulties encountered in using high-k dielectrics in the past were mainly poor uniformity of the thicknesses of the deposited films and poor quality at its interfaces. However, recent reports have shown that fairly good interfaces can be achieved [8-10].

**Fig. 1.2** Schematic of direct tunneling through a SiO<sub>2</sub> layer and the more difficult tunneling through a thicker layer of high-k oxide.

### 1.3 Requirements for metal gates and high-k materials

Along with the use of a high-k material to increase the gate capacitance, metallic or metal-silicide gate electrodes can be used to reduce the effect of polysilicon depletion. This additional capacitor lowers the overall capacitance of the gate stack in accordance with equation 1.1. The thickness of the depletion layer,  $L_d$ , varies inversely with the root of the carrier density as shown in equation 1.3:

$$L_d \quad \alpha \quad 1 / \left(N_{carriers}\right)^2 \tag{1.3}$$

As shown in equation 1.3, depletion width decreases with increasing dopant concentrations. This relationship is the driving force for very high doping of the polycrystalline silicon (poly-Si) gate electrode. Doping densities for poly-Si gate electrodes already reached their maximum levels. Since metals have intrinsic carrier concentrations much higher than even the most highly doped poly-Si, metal electrodes are a potential replacement for poly-Si. The solid solubility limit of many dopants in Si is about 1 atomic percent. Assuming a metal with about the same atomic density as silicon, that is, the carrier concentration in metal gates is about two orders of magnitude higher than in the poly-Si gates, Equation 1.1 shows that depletion layer widths could be reduced by a factor of 10 (at

the same bias) by replacing poly-Si with a metal (~one carrier/atom). The ITRS calls for a gate stack EOT of only 8Å by 2009, and depletion layer widths of only a few angstroms could easily limit the overall EOT of the gate stack at that time.

Meanwhile, the optimum work function for metal electrodes is believed to be  $\sim 4$  eV for n-channel and  $\sim 5.1$  eV for p-channel MOSFETs devices, respectively. These values match the conduction- and valance-band energies of the Si substrate. Hence, achieving proper band alignment for CMOS requires using two different metals, significantly increasing process complexity. A compromise is to use a metal having a work function close to the midgap of silicon for both types of MOSFETs at the cost of having somewhat higher threshold voltages, V<sub>t</sub>. Also, because of the possible formation and subsequently grown of low-k IL at the metal/high-k interface after annealing even at low temperatures [11-12], the scaling of metal/high-k structures into sub 1 nm EOT regime is difficult. Therefore, the introduction of inert gate electrodes with suitable work functions for high-k gated MOSFET devices is of the outmost importance. Metals that have been investigated in this thesis include layers of Al, Ta, Ru, Pt and W. Few physical properties for these metals are summarized in table 1.2. In general, metal gate processes are not yet compatible with the conventional poly-Si-gate CMOS processes [13], so replacing poly-Si with metal for the gate electrodes will require extensive process development.

| Metal     | Work function | Bond enthalpy to oxygen |

|-----------|---------------|-------------------------|

|           | [eV]          | $[kJ \cdot mol^{-1}]$   |

| Aluminum  | 4.06~4.20     | 511                     |

| Tantalum  | 4.12~4.25     | 799                     |

| Ruthenium | 4.60~4.71     | 528                     |

| Platinum  | 5.32~5.50     | 391                     |

| Tungsten  | 4.10~5.20     | 672                     |

**Table 1.2** Physical properties of the metals used in this thesis

Historically, the requirements for gate dielectrics are based on the unique properties of thermally grown SiO<sub>2</sub>. Silicon dioxide has been the prototypical gate

dielectric in view of its amorphous structure, a band gap of ~ 9 eV, band-offsets relative to silicon greater than 1 eV and, most importantly, the insolubility of the oxide (SiO<sub>2</sub>) in water. Indeed, the near ideal electrical characteristics of SiO<sub>2</sub> and its compatibility with silicon has been the critical element leading to the superiority of silicon over germanium, especially as the latter oxide was water soluble [14]. For integration of alternative gate dielectrics with a high-k into future CMOS technologies these stringent requirements have to be satisfied. Depending on the application, an EOT of 1 nm or less will be required. The SiO<sub>2</sub>-equivalent oxide thickness EOT can be expressed as:

$$EOT = \left(\frac{\varepsilon_{ox}}{\varepsilon_{IL}}\right) t_{IL} + \left(\frac{\varepsilon_{ox}}{\varepsilon_{hk}}\right) t_{hk}$$

(1.4)

Where the index *hk* refers to the high-k layer and the index *IL* refers to a possible interfacial layer between the Si substrate and the high-k film. The formation of such IL before, during or after the deposition needs to be minimized to obtain EOT less than 1 nm. Therefore, it is of high interest to deposit the high-k material either on a hydrogen terminated Si surface as obtained after an HF clean or on a "thin" intentionally grown SiO<sub>2</sub> layer. The latter leaves less room for the high-k film to be reduced to a lower-k silicate film during or after its deposition. In general, the requirements for high-k dielectric materials are various and they can be revised thoroughly in an excellent report by J. Robertson [15]. These requirements are:

- 1. High enough k (k > 10) value to replace  $SiO_2$  in the long term

- 2. Good thermodynamic stability when in contact with the silicon channel

- 3. Kinetically stable and compatible with CMOS process

- 4. Large enough (Ec, Ev > 1 eV) conduction and valence band offsets to silicon

- 5. Good electrical interface with silicon (low density of D<sub>it</sub>, defects, etc)

- 6. Few bulk electrically active defects

- 7. Electrically, its reliability properties such match or exceed that of  $SiO_2$ .

Actually, one of the most challenging problems found in the use of high-k materials in contact with silicon is the formation of two IL at both the upper and bottom interfaces of the high-k. An interfacial layer of SiO<sub>2</sub> often forms between the Si channel and the high-k oxide layer. There are advantages and disadvantages to this IL, as long as its presence and thickness can be controlled. The overall EOT of a layer (IL) of SiO<sub>2</sub> and a layer (*hk*) of high-k oxide is given by equation 1.4. Thus, an extra  $SiO_2$  layer is undesirable as it adds up directly to the overall EOT, imposing a severe limitation to scaling. The SiO<sub>2</sub> layer does not arise from the direct reaction of high-k with Si. It arises from the diffusion of O through the high-k layer to oxidize the Si underneath [15-17]. The SiO<sub>2</sub> layer usually grows during the post-deposition annealing stage, and not during the deposition itself. On the other hand, a purposely introduced SiO<sub>2</sub>-based IL would improve the overall electrical quality of the Si-oxide interface [15]. In principle, it can be made with a very low defect concentration, by annealing. A SiO<sub>2</sub> layer will also space the Si channel from the high-k oxide, which can lessen carrier mobility due to remote scattering. Nonetheless, a disadvantage of an interfacial oxide is that it may not have the same quality as SiO<sub>2</sub> produced by thermal oxidation of Si [18-19], and it may be defective. Bersuker et al [20] have emphasized that defects in this layer contribute to decrease channel mobilities. Yet, J.A. Ng has demonstrated that by increasing the thickness of a thermally grown oxide IL, the mobilities of n-channel La<sub>2</sub>O<sub>3</sub>-gated MOSFETs can be improved [21]. Therefore, it is an advantage to be able to control the thickness of the interfacial SiO<sub>2</sub> layer and if necessary, remove it entirely.

### 1.4 Review of rare-earth metal oxides

"Rare earth elements" and "rare earth metals" are trivial names sometimes applied to a collection of sixteen chemical elements in the periodic table, namely scandium, yttrium, and fourteen of the fifteen lanthanides (excluding promethium), which naturally occur on the Earth. The former two are included as they tend to occur with the latter in the same ore deposits. Some definitions additionally include the actinides. "Earth" is an obsolete term for oxide. At the time of their discovery, earths of these elements were believed to be scarce in abundance as minerals. However, the term "rare earth" is now deprecated by the International Union of Pure and Applied Chemistry (IUPAC), as these elements are in fact relatively abundant in the Earth's crust; the most abundant, cerium, at 68 parts per million, is the 25th most abundant element in the crust, more common than lead, while even the least abundant "rare" earth element, lutetium, is 200 times more abundant than gold.

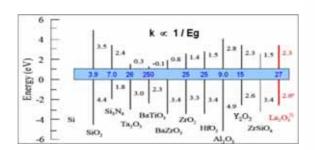

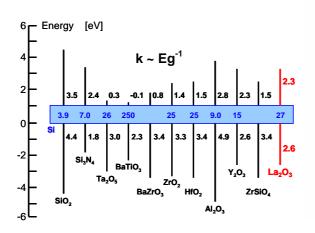

The term rare-earth oxide (REO) then comprises a chemical compound containing a rare earth element and oxygen. There are several of these REO seen as potential candidates for the replacement of conventional  $SiO_2$  at the gate of MOSFETs. Yet, a new gate dielectric can be selected in terms of its band gap and relative dielectric constant, since the product of the two can be a figure of merit to compare different dielectrics. Band gap of several candidate oxides for gate dielectric is shown in fig. 1.3, as a function of the relative dielectric constant.

Fig. 1.3 (A) Static dielectric constant versus band gap for candidate gate oxides [22].(B) Band gap for the REO of the lanthanide series [23-24].

## 1.5 Observations regarding the development of La<sub>2</sub>O<sub>3</sub> films

This section presents some aspects of  $La_2O_3$  thin films processing and characterization in order to assess their development and possible application into future CMOS technologies. Because of the highly intrinsic potential that these high-k films have regarding the replacement of conventional gate oxides, the desired development of  $La_2O_3$ -based dielectrics as gate oxides must then be introduced. To do this, the research problems that have been found during the previous developments of  $La_2O_3$  films are summarized and the main results obtained at Iwai laboratory regarding these high-k films are presented. Finally, a brief but precise discussion regarding the significance that a reliability study has on  $La_2O_3$ -gated MOS devices will be presented.

In fig. 1.4, identification of the research of some of the most important issues regarding the development of La<sub>2</sub>O<sub>3</sub> thin films is shown. The first topic is the obtention of the basic conditions for the deposition and processing of La<sub>2</sub>O<sub>3</sub> thin films, where several processing-related steps are involved. This is followed by the fabrication of MOS devices (whether capacitor or transistor structures) and the consequent verification of the correspondent devices' electrical characteristics in order to test the electrical nature and quality of the deposited La<sub>2</sub>O<sub>3</sub> thin films. Since these first two topics are closely related to each-other (better electrical characteristics of devices will be obtained by improving the deposition and processing conditions of the  $La_2O_3$  thin films), the immediate identification of the main problems related to the dielectric qualities of  $La_2O_3$  must then be identified and some solutions must be implemented as shown in the figure. So far, some of the most important problems to be solved have been identified: 1) highly hygroscopic properties of La<sub>2</sub>O<sub>3</sub> thin films, in which moisture absorption on the surface of the dielectric changes its physical, chemical and electronic properties leading to highly degraded MOS devices' characteristics, 2) low thermal stability problem, which is related to the change in the chemical and electronic structure of the whole La<sub>2</sub>O<sub>3</sub> film after relatively high temperature annealing conditions (whether during the deposition of the film itself, or during PDA or PMA conditions), 3) very low carrier mobility for ultra-thin EOT (< 1 nm) La<sub>2</sub>O<sub>3</sub> films, since thinner films increase the density of leakage current and therefore, the probability of trapping at the bulk and interfaces of La<sub>2</sub>O<sub>3</sub> with silicon and other immediate interfaces.