# Future of NanoCMOS after Scaling Limit

October 28, 2008

@Shenyang University of Technology

Hiroshi Iwai, Tokyo Institute of Technology

Founded in 1881, Promoted to Univ. 1929

## Tokyo Institute of Technology 東京工業大学

Promoted to Univ. 1929

Total 10,000 students: 5,000 under graduate

5,000 graduate

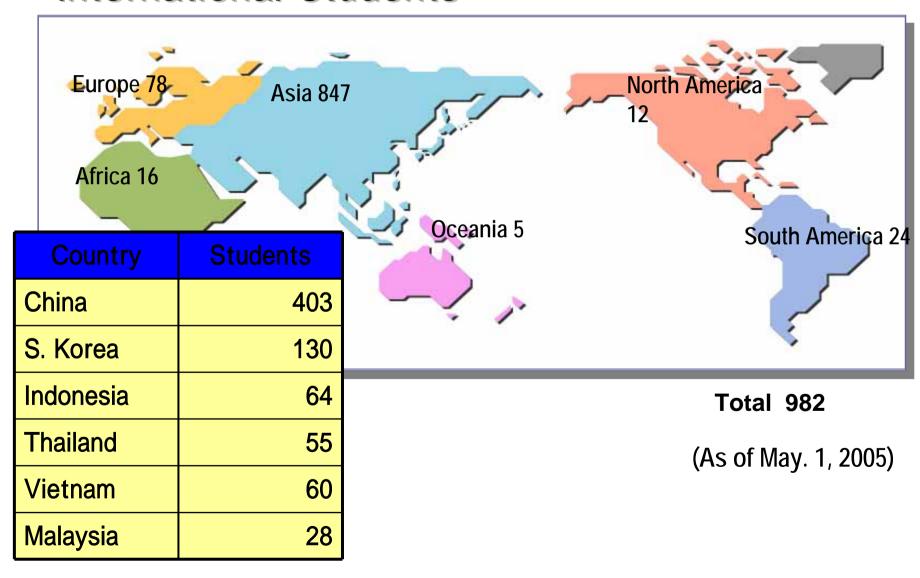

## International Students

There were many inventions in the 20<sup>th</sup> century:

Airplane, Nuclear Power generation, Computer,

Space aircraft, etc

- However, everything has to be controlled by electronics

- Electronics

Most important invention in the 20<sup>th</sup> century

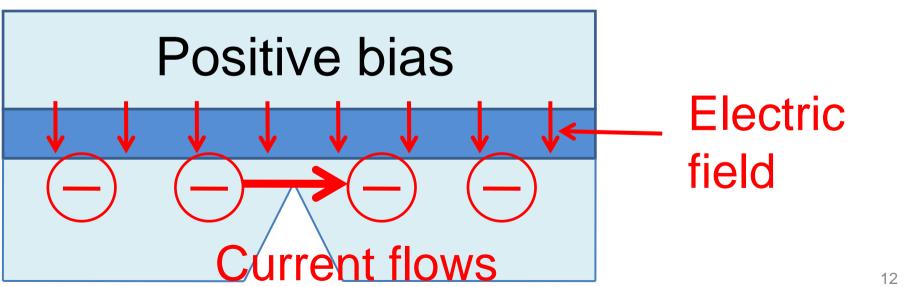

What is Electronics: To use electrons,

Electronic Circuits

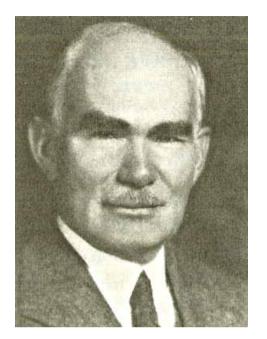

Lee De Forest

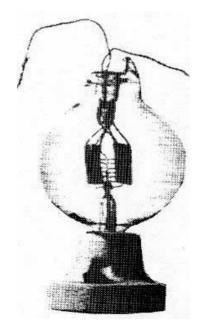

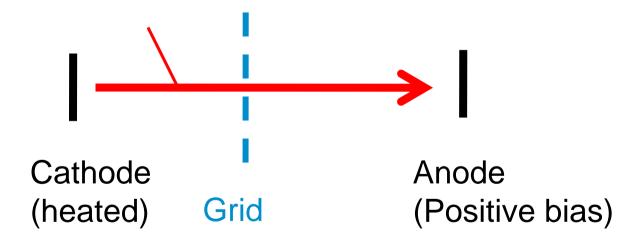

Electronic Circuits started by the invention of vacuum tube (Triode) in 1906

Thermal electrons from cathode controlled by grid bias

Same mechanism as that of transistor

#### 4 wives of Lee De Forest

1906 Lucille Sheardown

1907 Nora Blatch

1912 Mary Mayo, singer

1930 Marie Mosquini, silent film actress

Mary

Marie

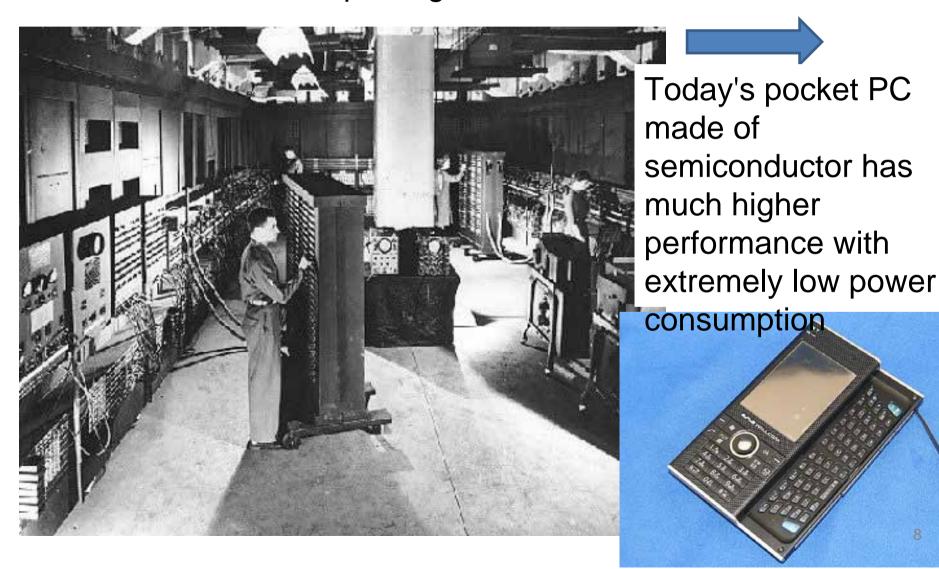

First Computer Eniac: made of huge number of vacuum tubes 19 Big size, huge power, short life time filament

→ dreamed of replacing vacuum tube with solid-state device

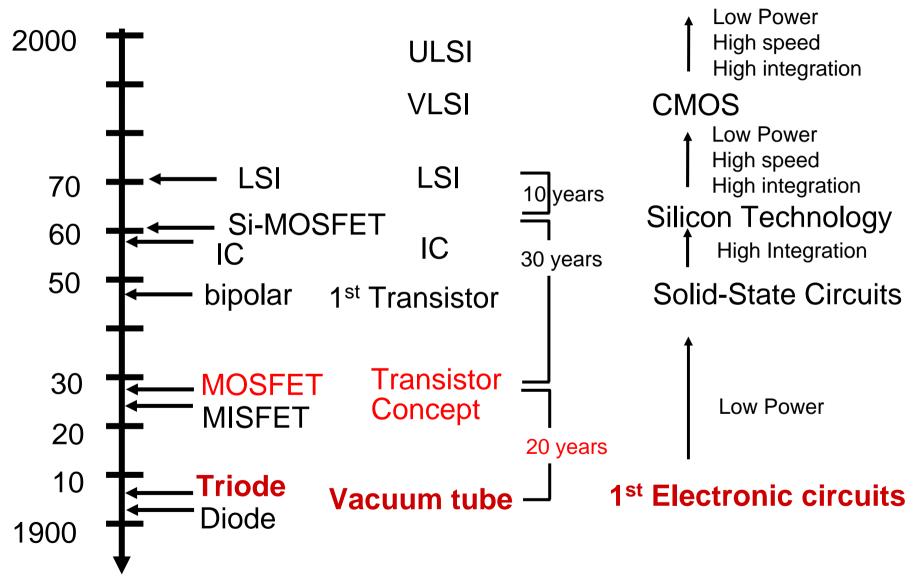

## History of Semiconductor devices

```

1947, 1<sup>st</sup> Point Contact Bipolar Transistor:

Ge Semiconductor, Bardeen, Brattin

→ Nobel Prize

1948, 1<sup>st</sup> Junction Bipolar Transistor,

Ge Semiconductor, Schokley

→ Nobel Prize

1958, 1<sup>st</sup> Integrated Circuits,

Ge Semiconductor, J.Kilby → Nobel Prize

1959, 1<sup>st</sup> Planar Integrated Circuits,

Noice

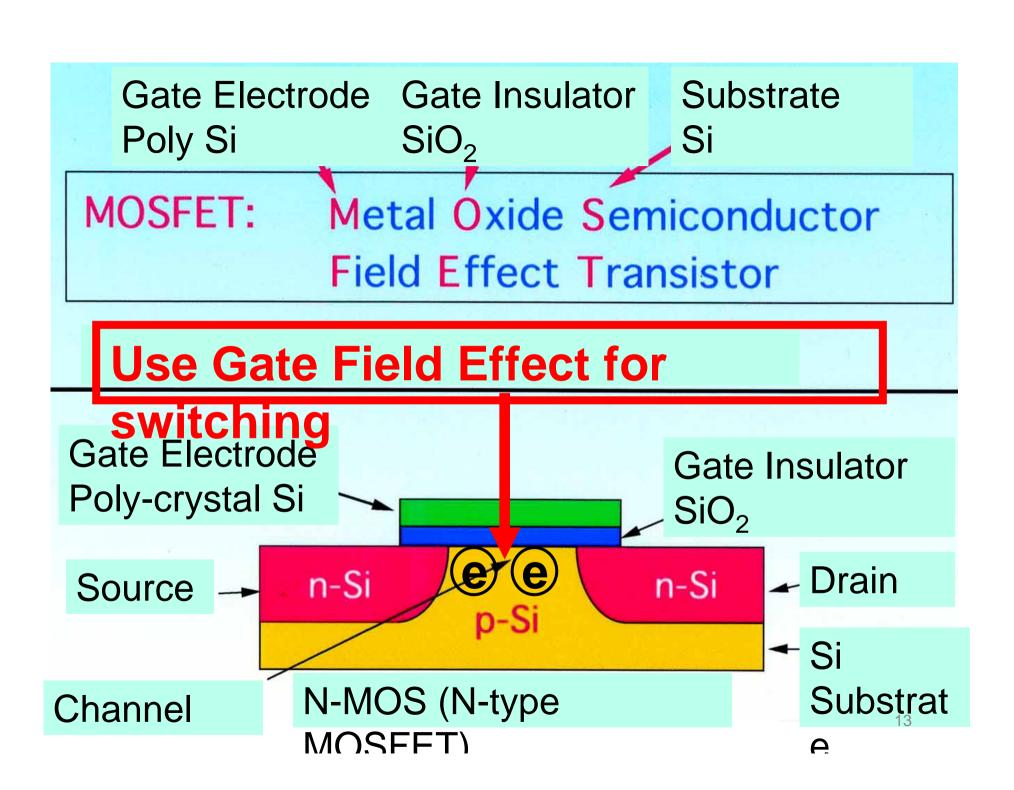

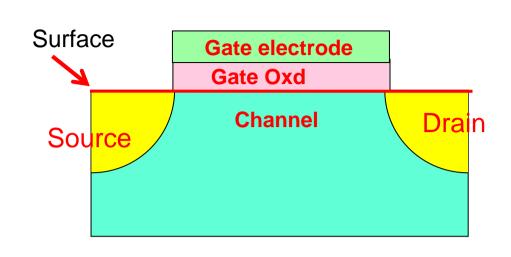

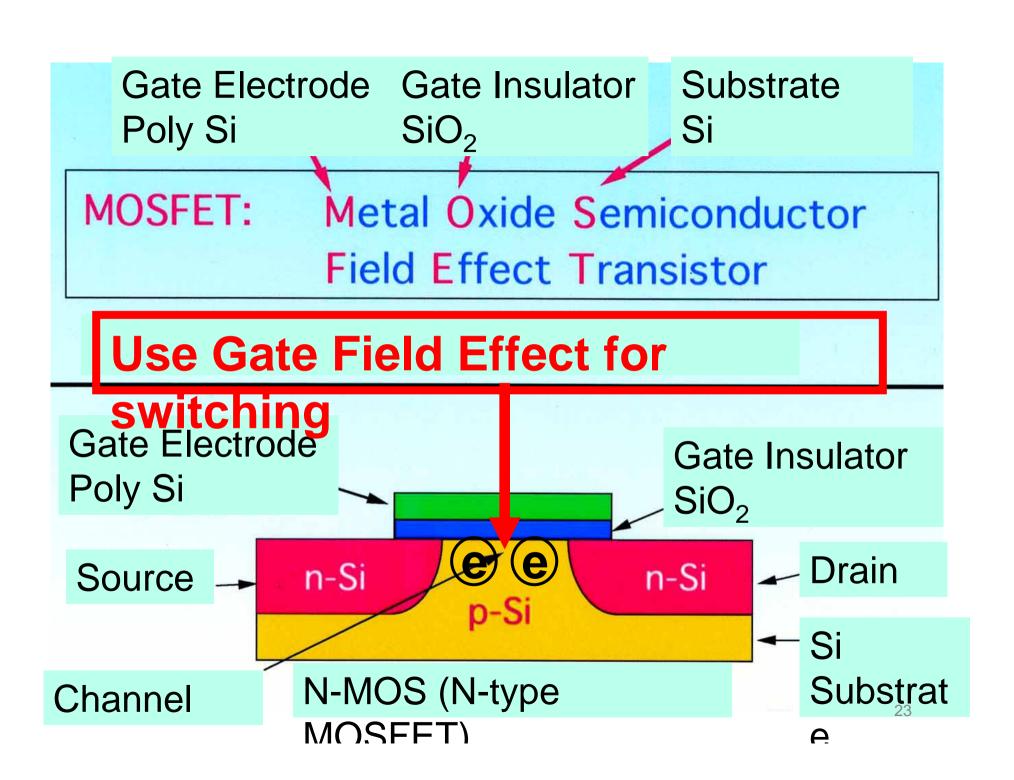

1960, 1<sup>st</sup> MOS Transistor, Kahng,

```

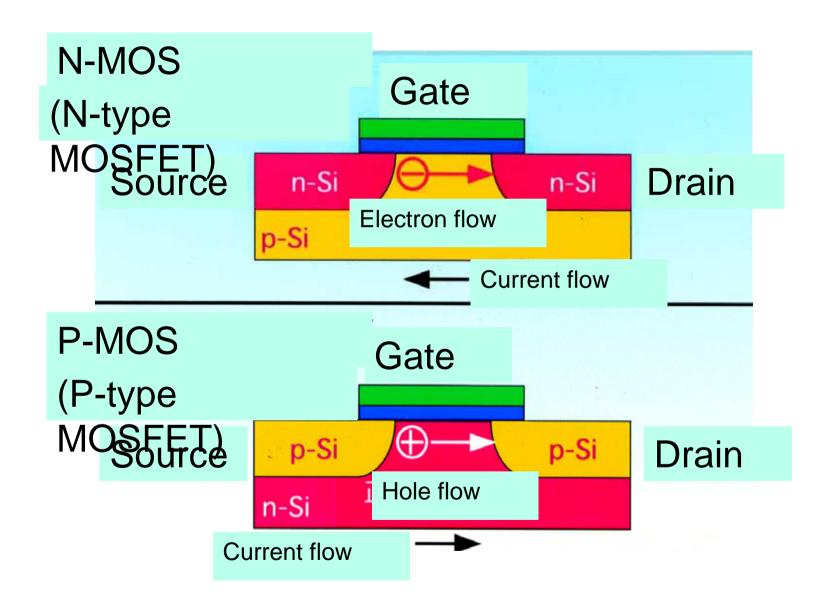

Si Semiconductor 1963, 1<sup>st</sup> CMOS Circuits, C.T. Sah and F. Wanlass

## History of Electronic Devices

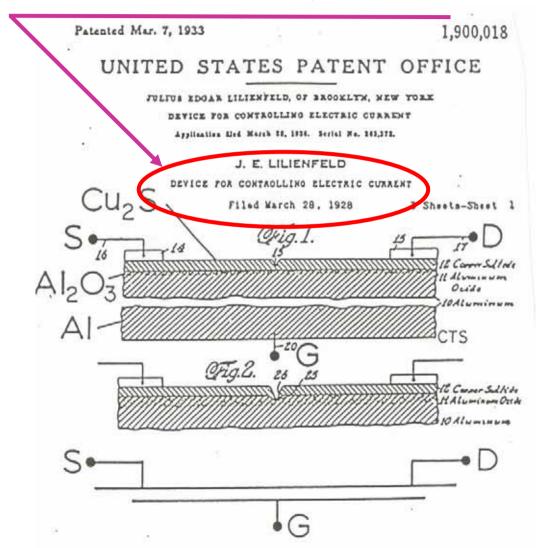

#### J. E. LILIENFELD

#### DEVICES FOR CONTROLLED ELECTRIC CURRENT

#### **Filed March 28, 1928**

#### J.E.LILIENFELD

## Capacitor structure with notch

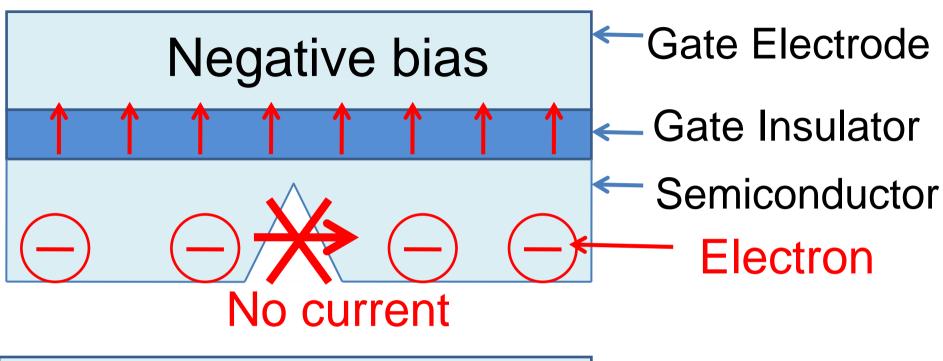

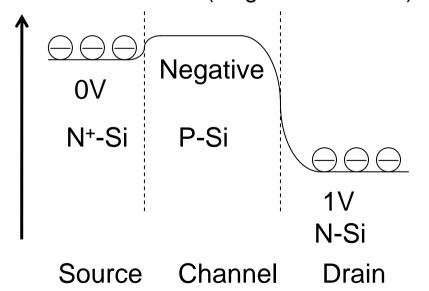

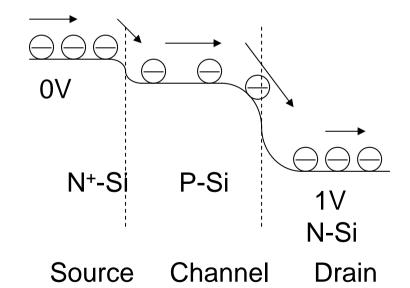

#### 0 bias for gate

#### Surface Potential (Negative direction)

#### Positive bias for gate

However, no one could realize MOSFET operation for more than 30 years. Because of very bad interface property between the semiconductor and gate insulator

**Even Shockley!**

Very bad interface property between the semiconductor and gate insulator

Drain Current was several orders of magnitude sm than expected

**Even Shockley!**

However, they found amplification phenomenon when investigating Ge surface when putting needles.

This is the 1<sup>st</sup> Transistor:

Not Field Effect Transistor, But Bipolar Transistor (another mechanism)

## 1947: 1st transistor

**Bipolar using Ge**

J. Bardeen

W. Bratten,

W. Shockley

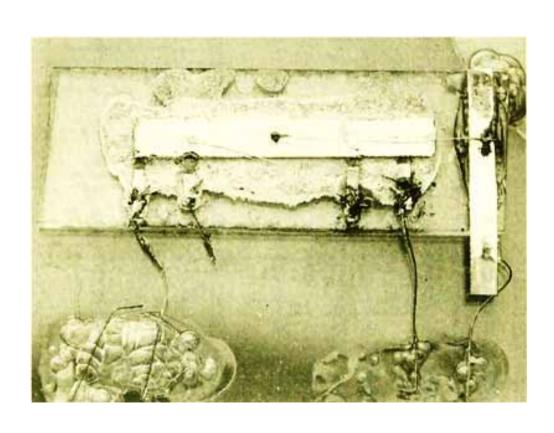

## 1958: 1st Integrated Circuit

Jack S. Kilby

Connect 2 bipolar transistors in the Same substrate by bonding wire.

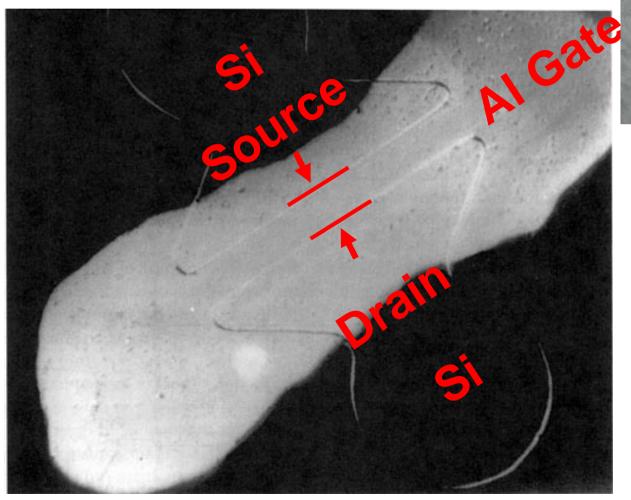

1960: First MOSFET

by D. Kahng and M. Atalla

## **Top View**

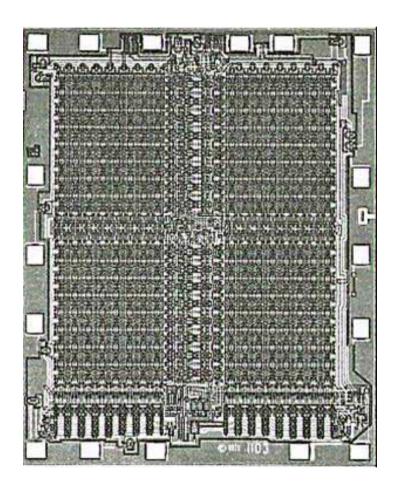

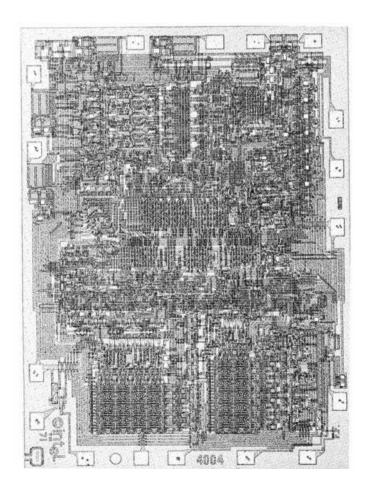

## 1970,71: 1st generation of LSIs

## **DRAM** Intel 1103

## MPU Intel 4004

## MOS LSI experienced continuous progress for many years

| Name of Integrated Circuits |                             | Number of<br>Transistors |

|-----------------------------|-----------------------------|--------------------------|

| 1960s                       | IC (Integrated Circuits)    | ~                        |

| 1970s                       | LSI (Large Scale Integrated | Circuit) ~1,0            |

| 1980s                       | VLSI (Very Large Scale IC)  | ~10,0                    |

| 1990s                       | ULSI (Ultra Large Scale IC) | ~1,000,0                 |

| 2000s                       | ?LSI (? Large Scale IC)     | ~1000;000                |

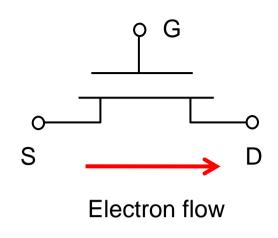

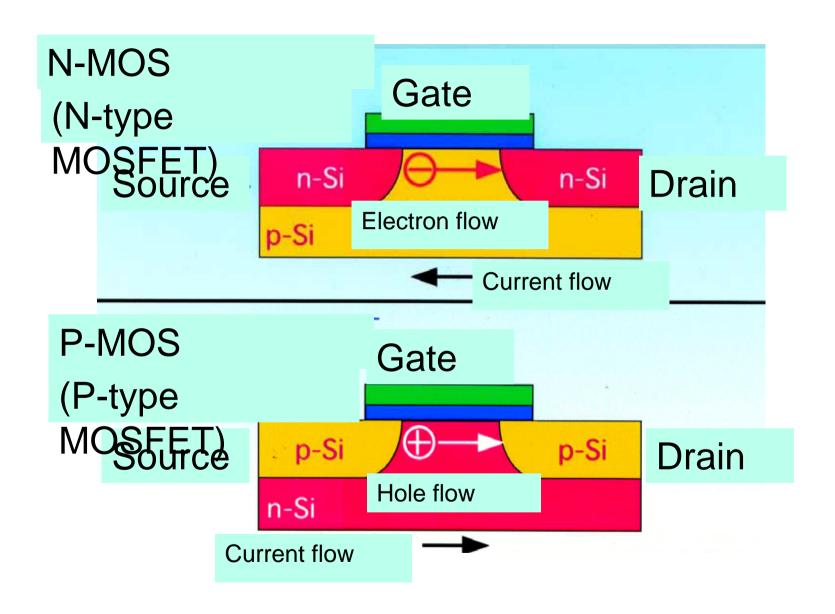

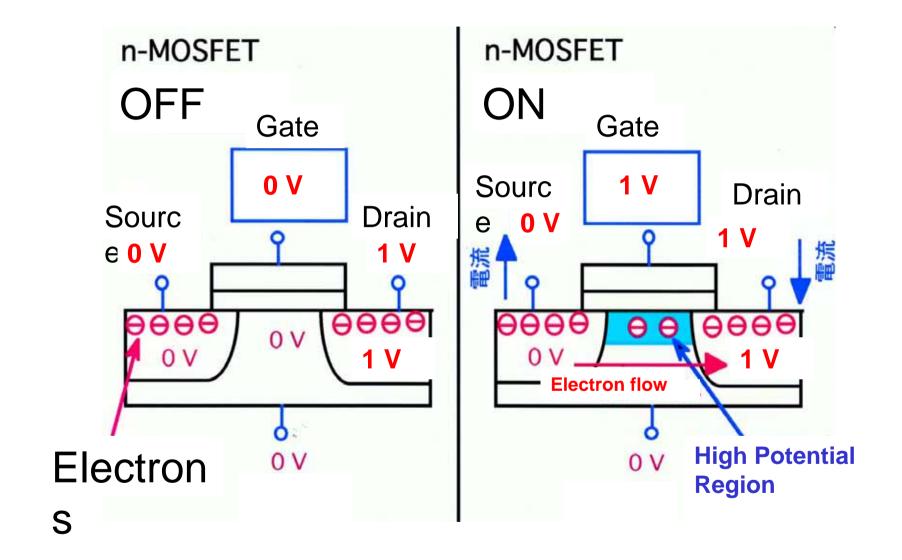

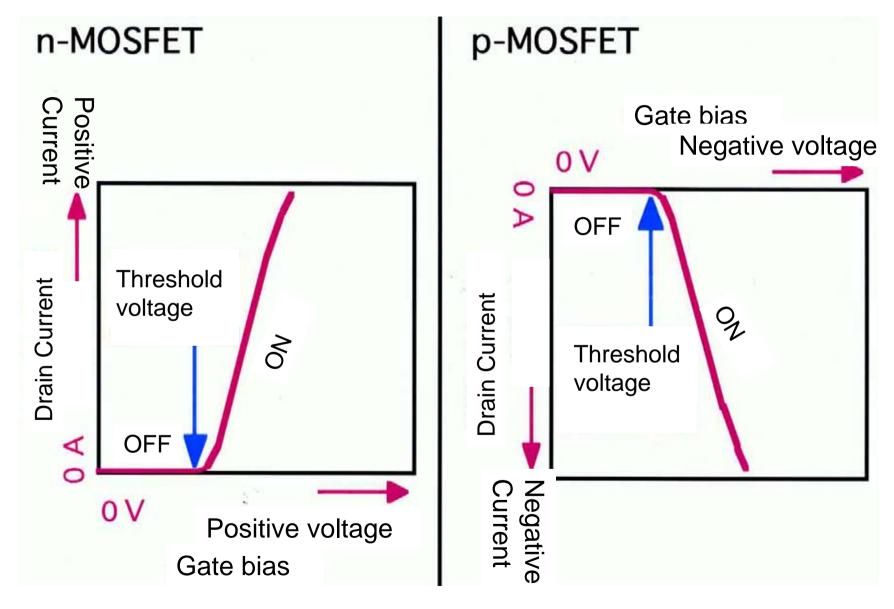

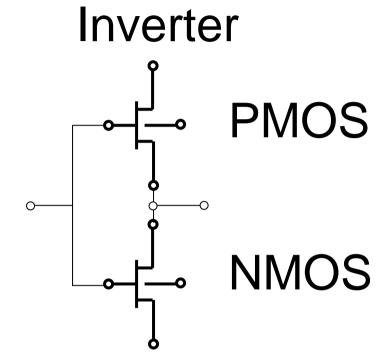

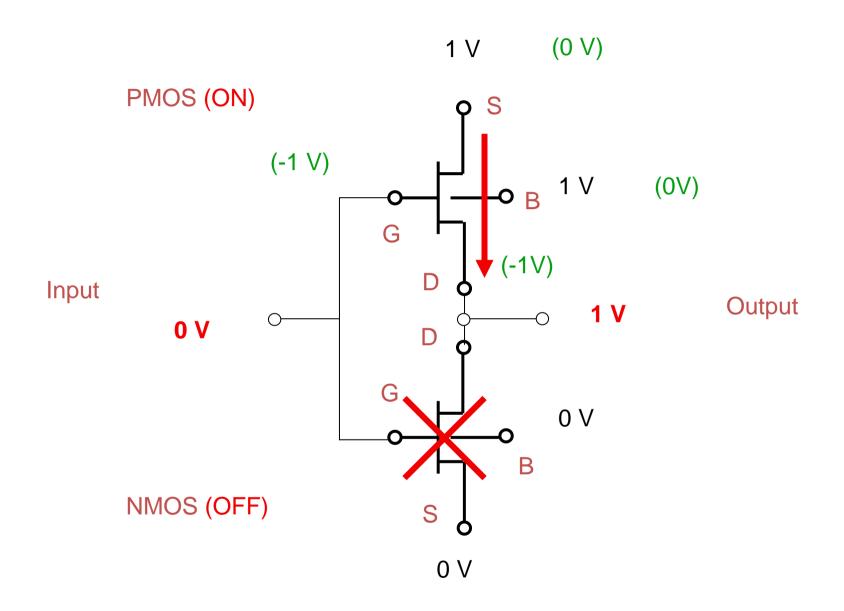

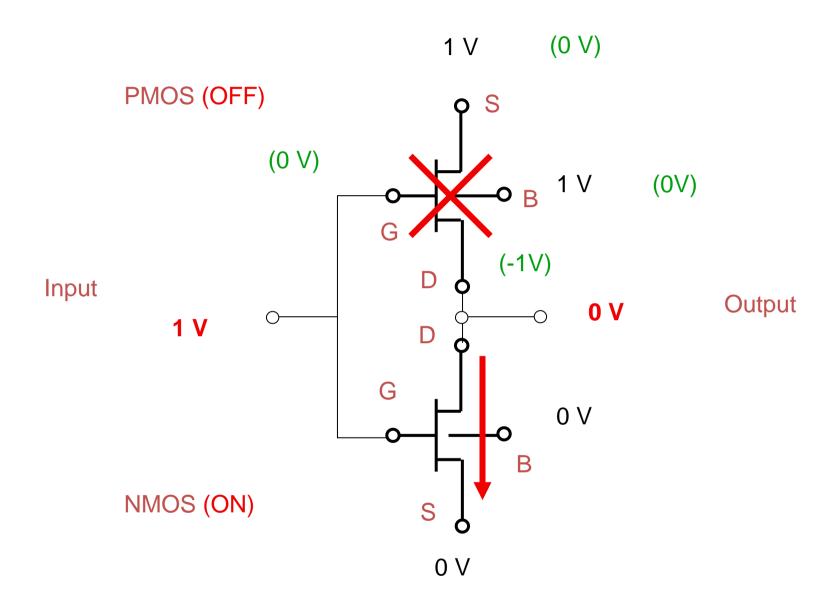

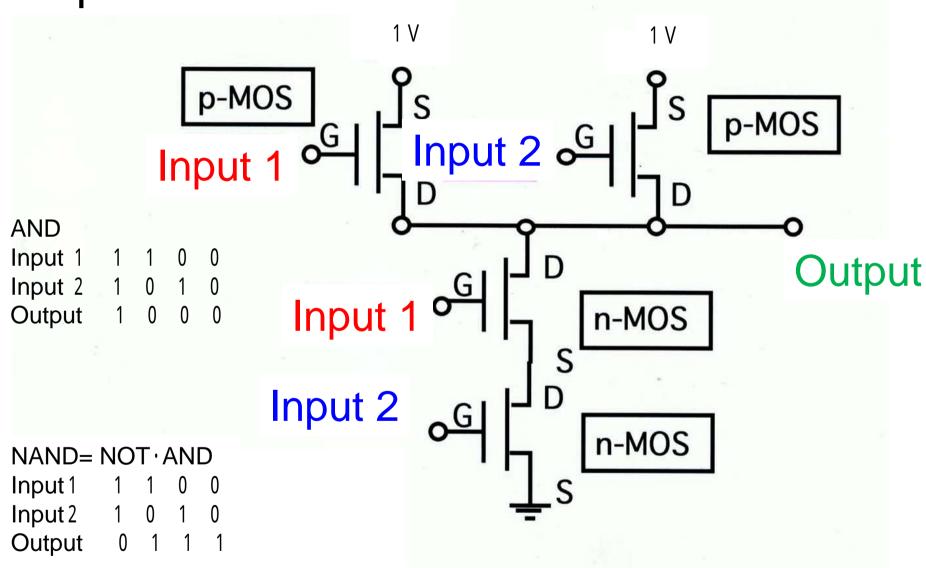

## **Complimentary MOS**

When NMOS is ON, PMOS is OFF When PMOS is ON, NMOS is OFF

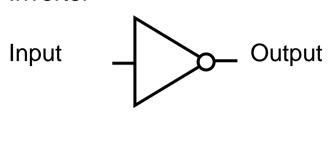

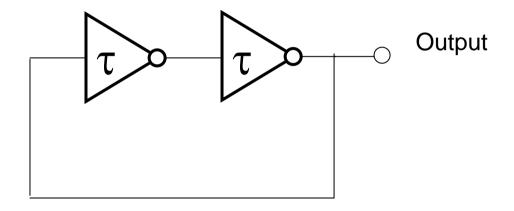

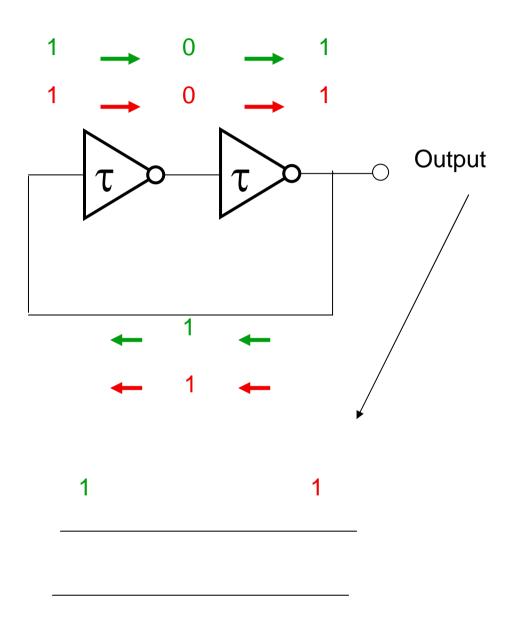

#### Inverter

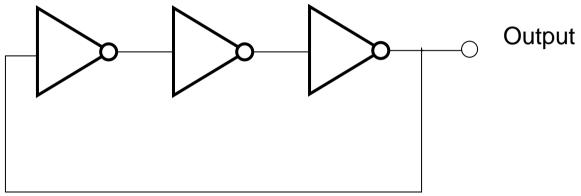

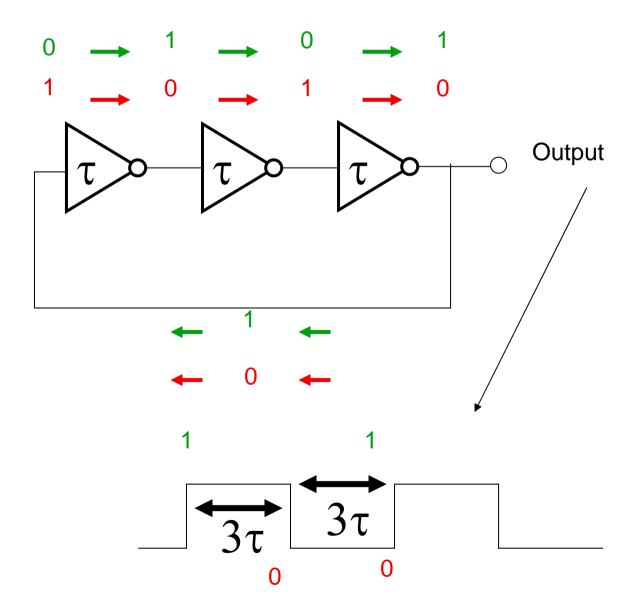

#### **Oscillator**

#### **Latch (Memory)**

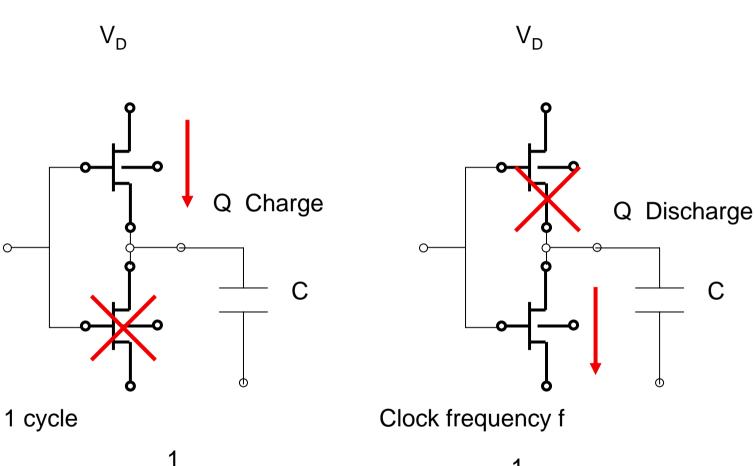

#### CMOS: Low Power: No DC current from Power supply to the ground

$$P = \frac{1}{2} CV_{D}^{2}$$

$$P = \frac{1}{2} fCV_D^2$$

## 2 input NAND Circuit

Needless to say, but....

## **CMOS Technology:**

Indispensible for our human society

## Al the human activities are controlled by CMOS

living, production, financing, telecommunication, transportation, medical care, education, entertainment, etc.

## **Without CMOS:**

There is no computer in banks, and world economical activities immediately stop.

Cellarer phone dose not exists

## Downsizing of the components has been the driving force for circuit

| evolution<br>1900  | າ<br>1950          | 1960               | 1970               | 2000               |

|--------------------|--------------------|--------------------|--------------------|--------------------|

| Vacuum<br>Tube     | Transistor         | IC                 | LSI                | ULSI               |

| 10 cm              | cm                 | mm                 | 10 μm              | 100 nm             |

| 10 <sup>-1</sup> m | 10 <sup>-2</sup> m | 10 <sup>-3</sup> m | 10 <sup>-5</sup> m | 10 <sup>-7</sup> m |

In 100 years, the size reduced by one million times. There have been many devices from stone age. We have never experienced such a tremendous reduction of devices in human history.

## Downsizing

- 1. Reduce Capacitance

- → Reduce switching time of MOSFETs

- → Increase clock frequency

- Increase circuit operation speed

- 2. Increase number of Transistors

- **→** Parallel processing

- Increase circuit operation speed

Downsizing contribute to the performance increase in double ways → 一石二鳥

Thus, downsizing of Si devices is the most important and critical issu

## Many people wanted to say about the limit.

## Past predictions were not correct!!

| Period       | Expected limit(size) | Cause<br>                    |

|--------------|----------------------|------------------------------|

| Late 1970's  | 1μm:                 | SCE                          |

| Early 1980's | 0.5μm:               | S/D resistance               |

| Early 1980's | 0.25μm:              | Direct-tunneling of gate SiC |

| Late 1980's  | $0.1\mu m$ :         | '0.1µm brick wall'(various)  |

| 2000         | 50nm:                | 'Red brick wall' (various)   |

| 2000         | 10nm:                | Fundamental?                 |

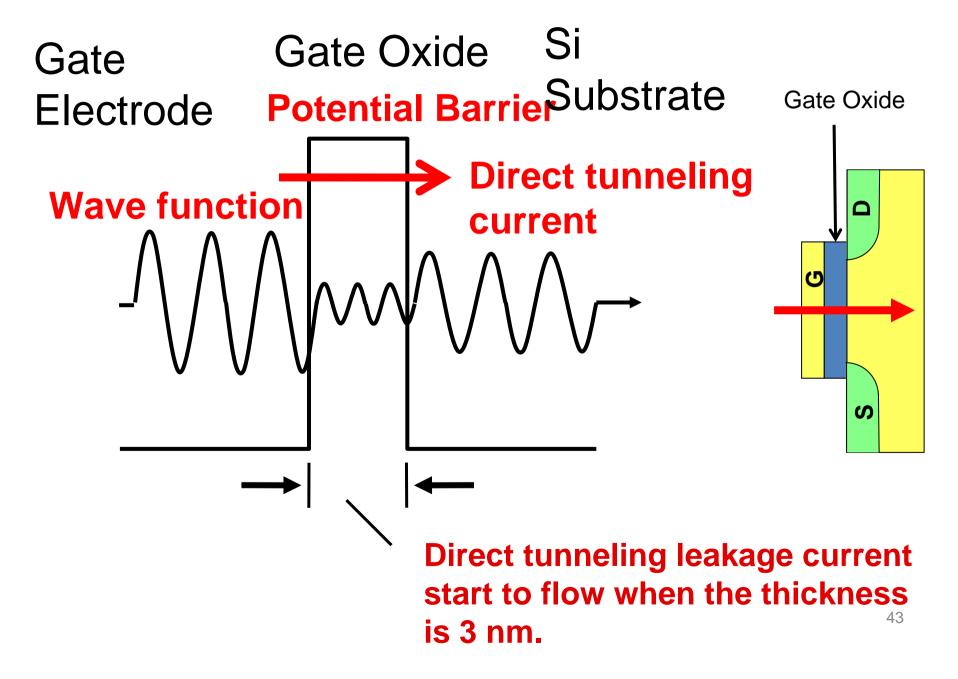

Historically, many predictions of the limit of **VOSING** book written 1979 predict that 0.25 micro-meter would be the limit because of direct-tunneling current through the very thin-gate oxide.

#

C. Mead

L. Conway

## VLSI textbook

Finally, there appears to be a fundamental limit <sup>10</sup> of approximately quarter micron channel length, where certain physical effects such as the tunneling through the gate oxide ..... begin to make the devices of smaller dimension unworkable.

## Direct-tunneling effect

## Direct tunneling leakage w found to be OK! In 1994!

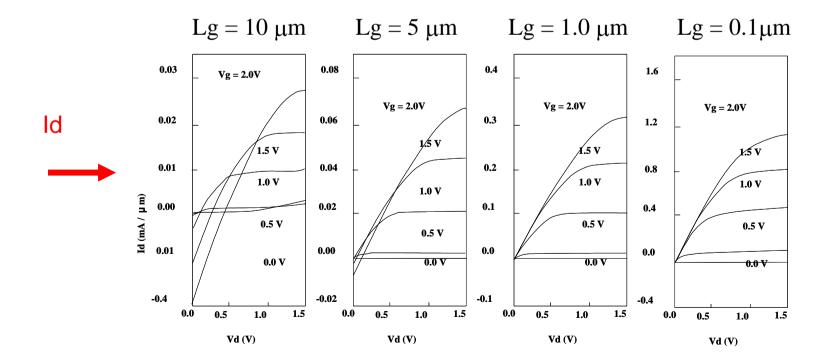

MOSFETs with 1.5 nm gate oxide  $Lg = 10 \mu m$  $Lg = 1.0 \mu m$  $Lg = 0.1 \mu m$  $Lg = 5 \mu m$ 0.03 0.08 0.4 1.6 Vg = 2.0VVg = 2.0VVg = 2.0VVg = 2.0V0.02 0.3 0.06 1.2 1.5 V 1.5 V 1.5 V 1.5 V 0.01 0.2 0.04 8.0 1.0 V 1.0 V 1.0 V 1.0 V Id (mA / µm) 0.00 0.02 0.1 0.4 0.5 V 0.5 V 0.5 V 0.5 V 0.01 0.00 0.0 0.0 0.0 V 0.0 V 0.0 V 0.0 V -0.4 -0.02 -0.1 -0.4 1.5 1.5 0.0 0.5 1.0 0.0 0.5 1.0 0.0 0.5 1.0 1.5 0.0 0.5 1.0 1.5 Vd (V) Vd (V) Vd (V) Vd (V) 44

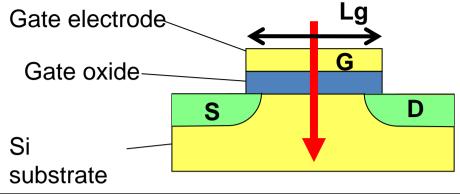

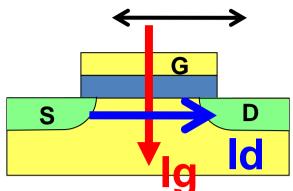

Gate leakage: Ig ∞ Gate Area ∞ Gate length (Lg)

Drain current: Id ∞ 1/Gate length (Lg)

$Lg \rightarrow small$ ,

Then, Ig → small, Id → large, Thus, Ig/Id → very small

## Do not believe a text book statement, blindly!

**Never Give Up!**

No one knows future!

There would be a solution!

Think, Think, and Think!

Or, Wait the time!

Some one will think for you

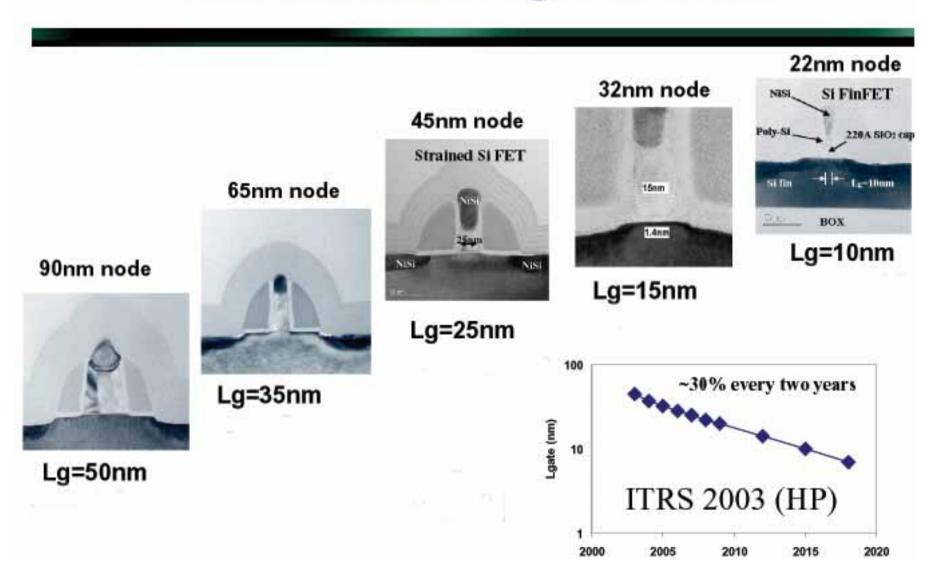

## **Transistor Scaling Continues**

Qi Xinag, ECS 2004,47AM

## **Downsizing limit?**

## Channel length?

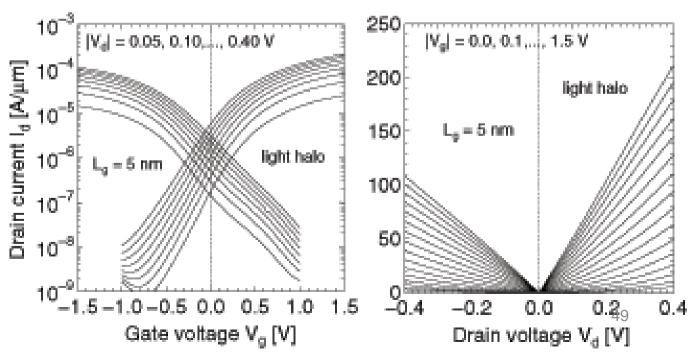

5 nm gate length CMOS

Is a Real Nano Device!!

H. Wakabayashi et.al, NEC

**IEDM, 2003**

75 nm

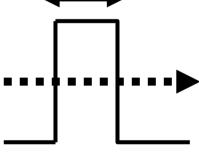

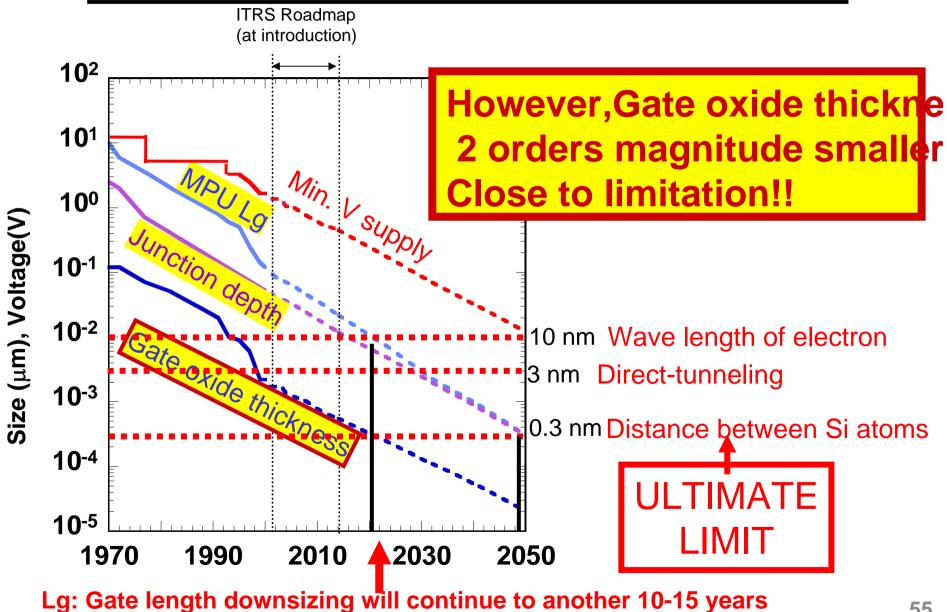

## **Downsizing limit!**

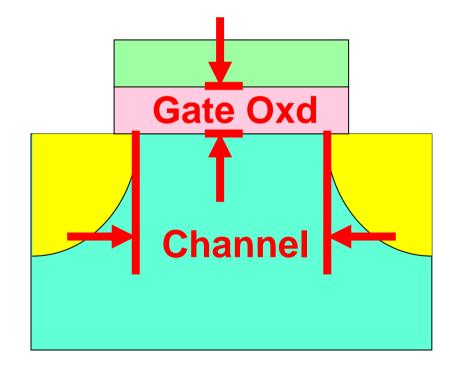

Channel length Gate oxide thickness

**Tunneling** distance

Atom

distance

3 nm

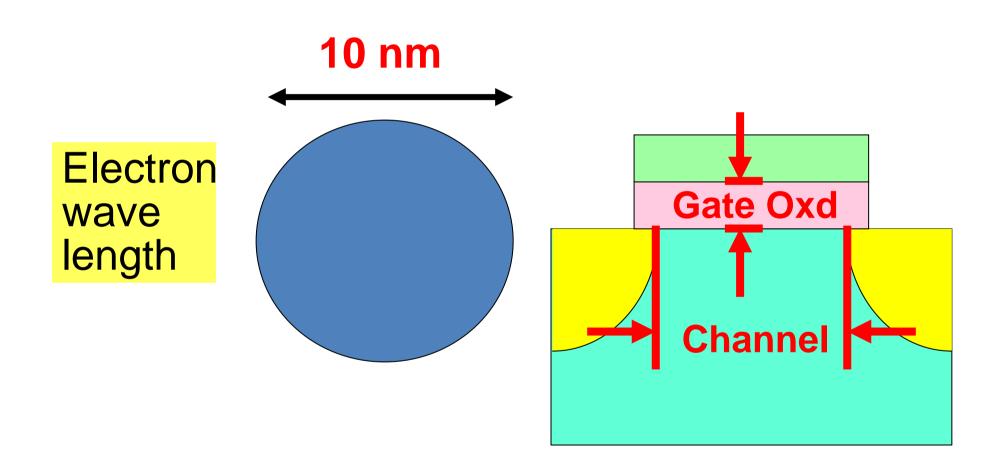

## **Prediction now!**

Electron wave length

10 nm

Tunneling distance

3 nm

Atom distance

0.3 nm

**MOSFET** operation

$$Lg = 2 \sim 1.5 \text{ nm}$$

?

Below this, no one knows future!

## Maybe, practical limit around 5 nm.

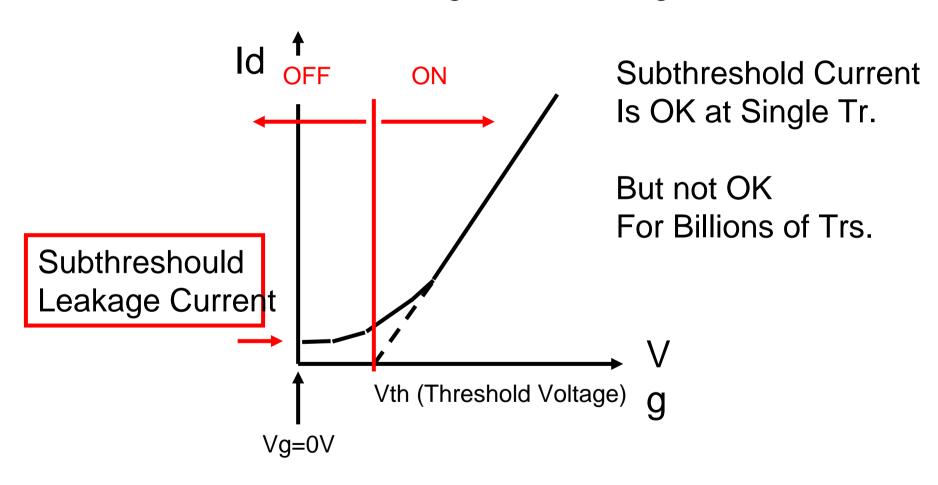

When Gate length Smaller,

→ Subthrehold Leakage Current Larger

We have to reduce the Log Id Supply voltage. Then Vth should be lowered. 10-6A  $10^{-7}A$ Subthreshold 10-8A leakage current *10-9* Vth lowering increase Vth Vg(V)Vg = 0V

## **Prediction now!**

Electron wave length

10 nm

Tunneling distance

3 nm

Atom distance

0.3 nm

Practical limit for integration Lg = 5 nm?

MOSFET operation

$Lg = 2 \sim 1.5 \text{ nm}$ ?

Below this, no one knows future!

## Ultimate limitation

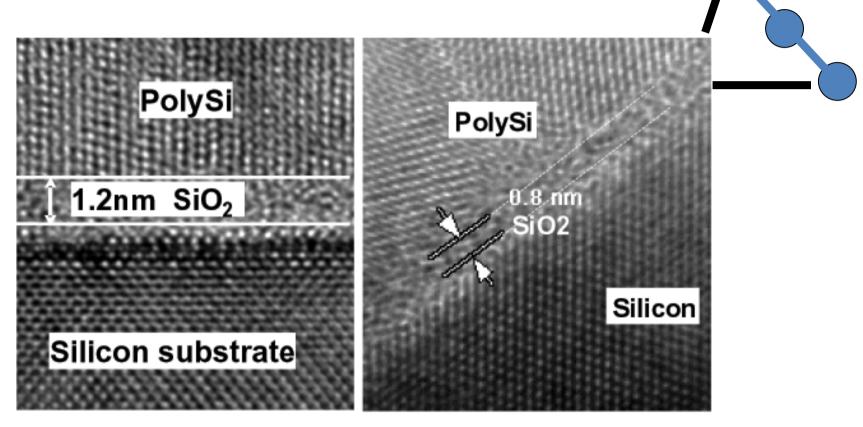

## 0.8 nm Gate Oxide Thickness MOSFETs operat

0.8 nm: Distance of 3 Si atoms!!

- 1.2nm physical SiO2 in production (90nm logic node)

- 0.8nm physical SiO2 in research transistors

By Robert Chau, IWGI 200

So, we are now in the limitation of downsizing?

Do you believe this or do not?

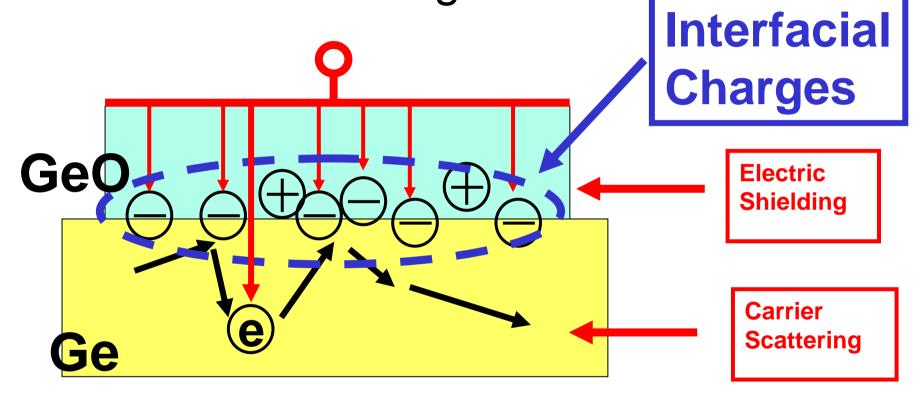

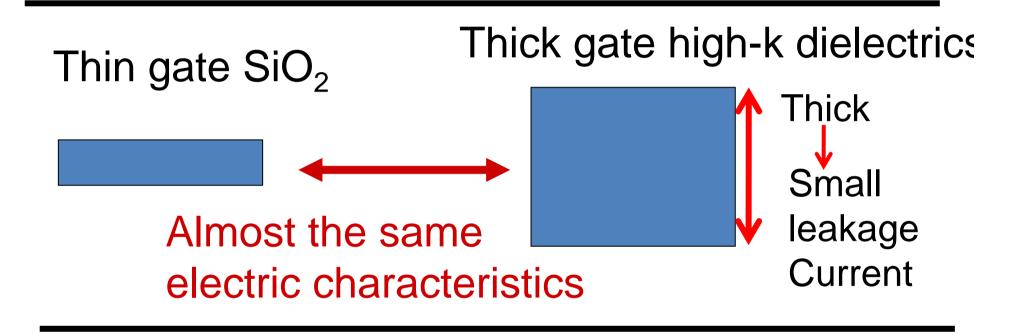

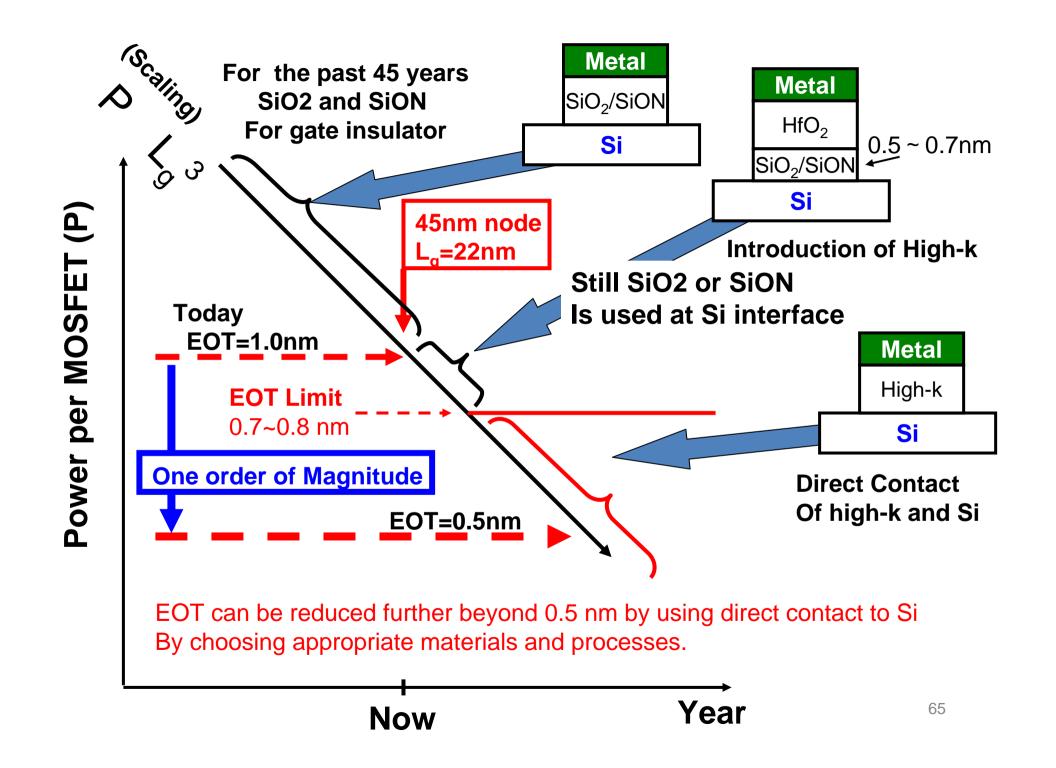

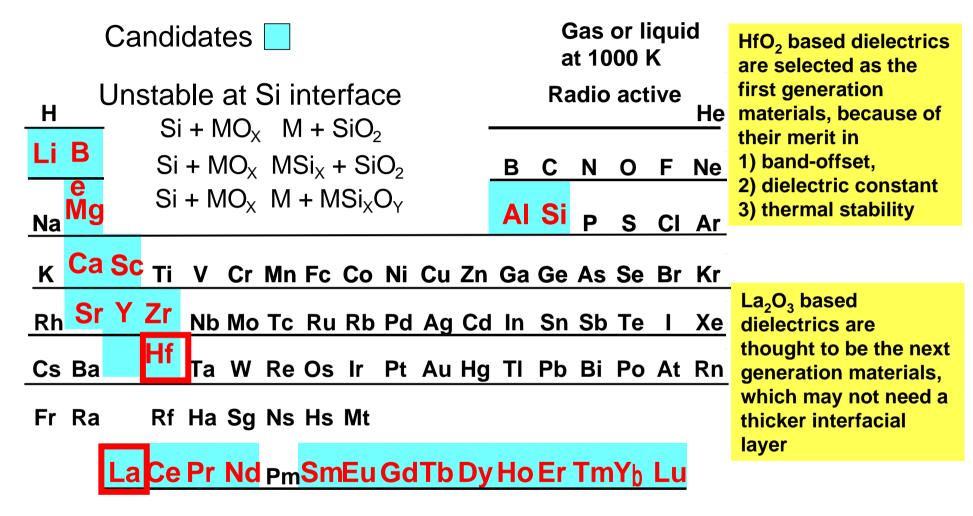

## There is a solution! K: Dielectric Constan To use high-k dielectrics

However, very difficult and big challenge!

Remember MOSFET had not been realized without Si/SiO<sub>2</sub>!

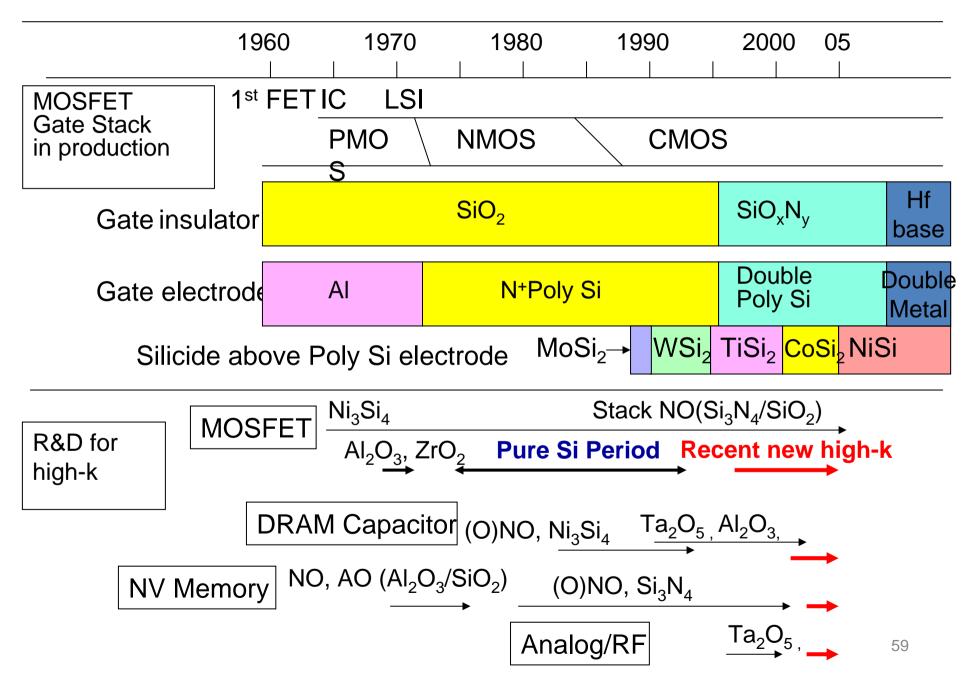

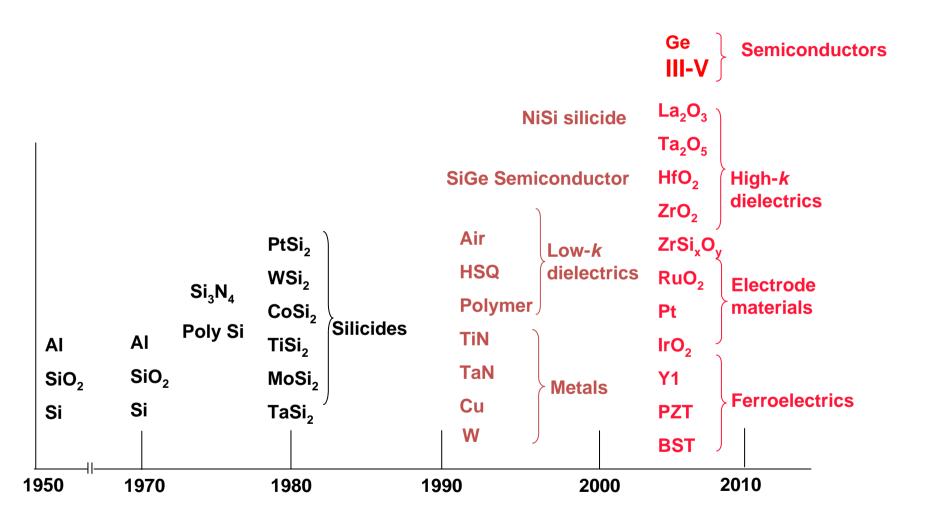

### **Historical Trend of New Material for Gate Stack**

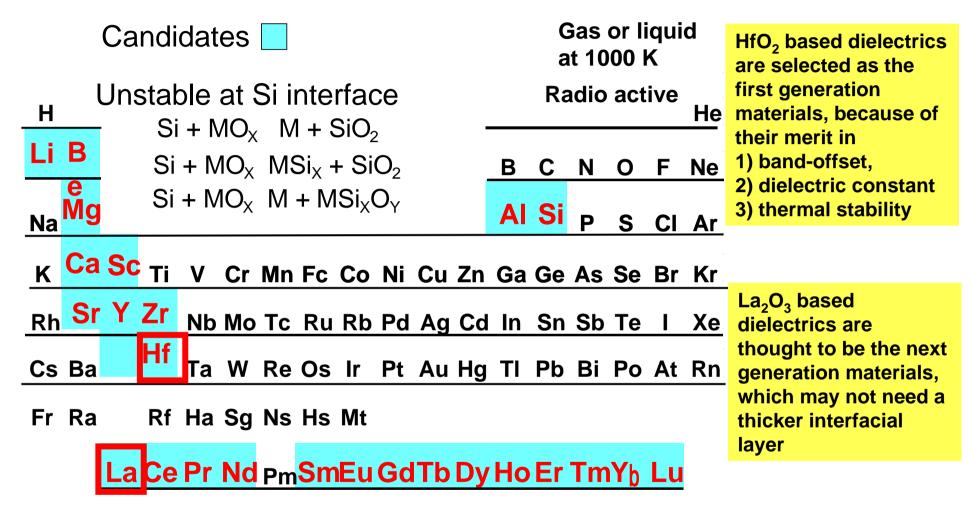

#### **Choice of High-k elements for oxide**

Ac Th Pa U Np Pu AmCm Bk Cf Es Fm Md No Lr

R. Hauser, IEDM Short Course, 1999 Hubbard and Schlom, J Mater Res 11 2757 (1996)

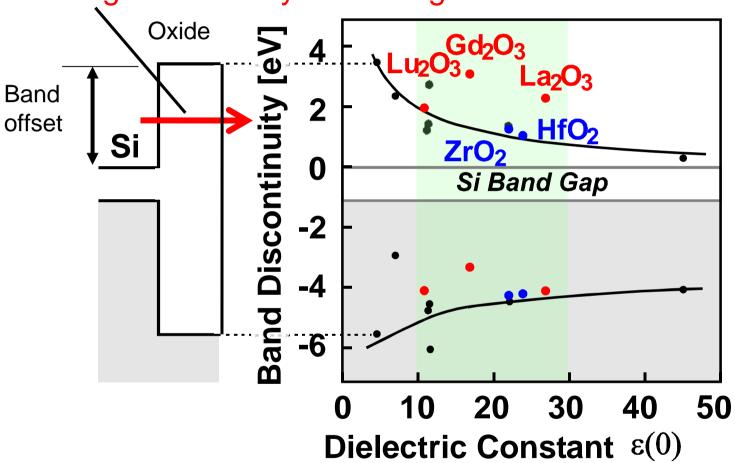

## Conduction band offset vs. Dielectric Constan

### Leakage Current by Tunneling

XPS measurement by Prof. T. Hattori, INFOS 2003

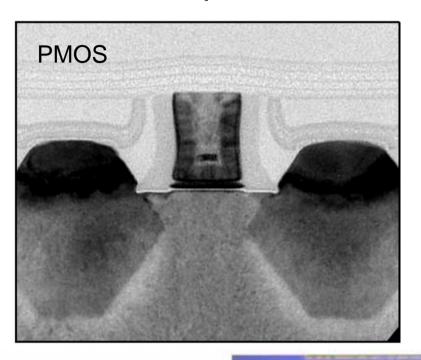

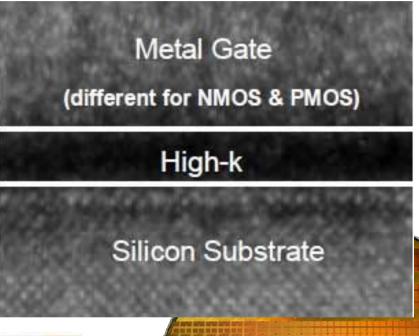

Intel's announcement, January 26, 2007, and IEDM Dec 2007

Hafnium-based high-k material by ALD: EOT= 1nm Specific gate metals (Intel's trade secret)

Different Metals for NMOS and PMOS

Use of 193nm dry lithography

From 65 nm to 45 nm Tech.

Tr density: 2 times increase

Tr switching power: 30% reduction

Tr switching speed: 20% improvement

S-D leakage power: 5 times reduction

Gate oxide leakage: 10 times reduction

45nm processors (Core™2 family processors "Penryn") running Windows\* Vista\*, Linux\* etc.

45nm production in the second half of 2007

## High-k gate insulator MOSFETs for Intel: EOT=1nm

**EOT:** Equivalent Oxide Thickness

History and future of Transistor Shrinking, Shrinking, and Shrinking! and then, Shrinking, Shrinking, and Shrinking!

C, V ∝ L C: Capacitance V: Voltage

Switching speed CV/I → Decrease

Power consumption  $CV^2/2 \rightarrow Decrease$

Integration density: 1/L<sup>2</sup> → Increase

1970 2007

Gate length 10,000 nm 25 nm

Gate Oxd Thickness 100 nm 1 nm

#### **Choice of High-k elements for oxide**

Ac Th Pa U Np Pu AmCm Bk Cf Es Fm Md No Lr

R. Hauser, IEDM Short Course, 1999 Hubbard and Schlom, J Mater Res 11 2757 (1996)

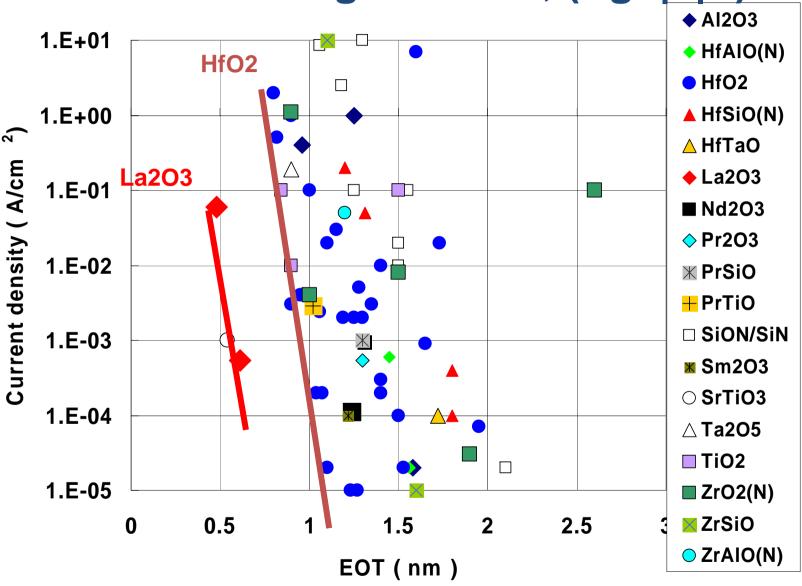

## Gate Leakage vs EOT, (Vg=|1|V)

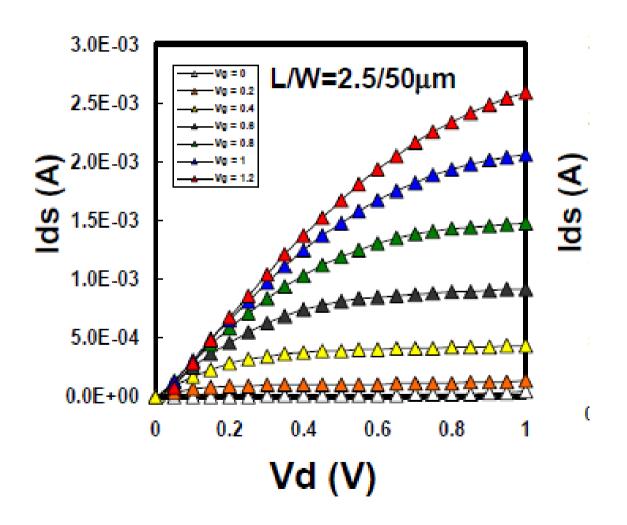

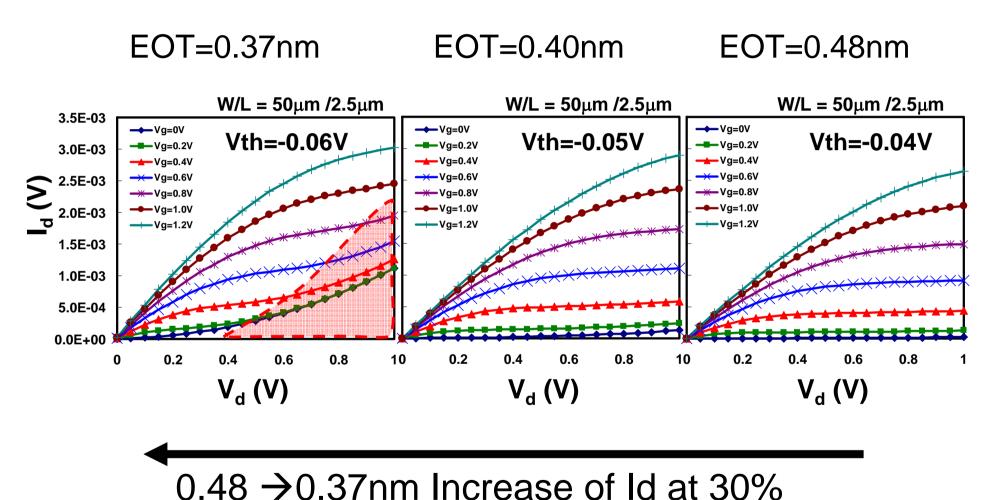

## EOT = 0.48 nm Our results Transistor with La2O3 gate insulator

## **EOT=0.37nm**

La2O3

# New material research will give us many future possibilities and the most important

for Nano-GMORigh-k!

New material for Metal gate electrode

New material for High-k gate dielectric

New channel materia New material For Metal S/D

magnification

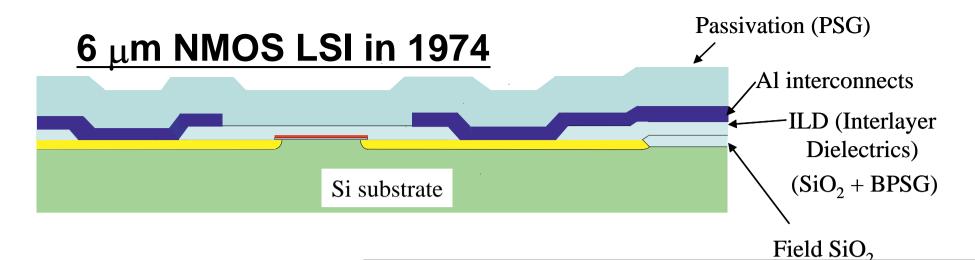

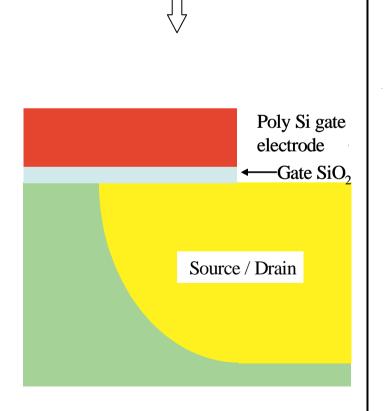

## <u>Layers</u> Ma

1. Si substrate

2. Field oxide

3. Gate oxide

4. Poly Si

5. S/D

6. Interlayer

7. Aluminum

8. Passivation

## **Materials**

1. Si

2. SiO<sub>2</sub>

3. BPSG

4. Al

5. PSG

## **Atoms**

1. Si

2. 0

3. P

4. B

5. AI

(H, N, CI)

## Just examples! Many other candidates

## **New materials**

Y. Nishi, Si Nano Workshop, 2006,

(S. Sze, Based on invited talk at Stanford Univ., Aug. 1999)

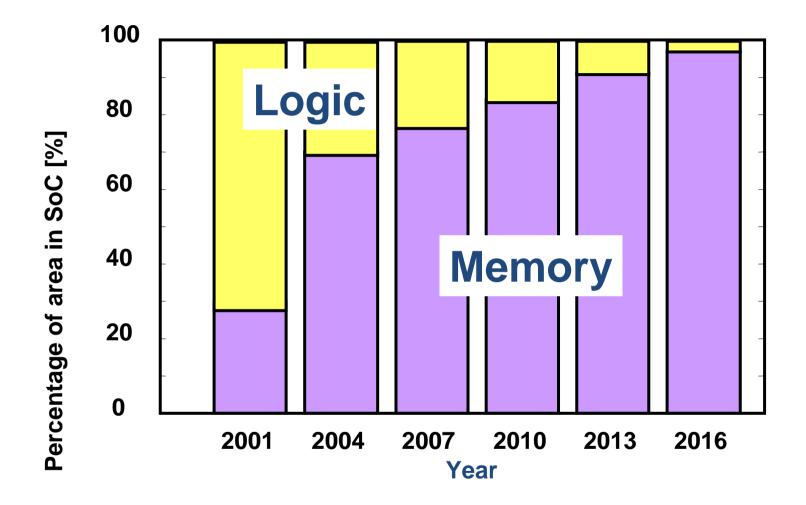

# Memory area will increase

Due to design productivity, yield, and power

# Now: After 45 Years from the 1st single MOSFE

32 Gb and 16Gb NAND, SAMSUNG

#### Samsung's NAND flash trend

| Capacity Production |       | 1 <sup>st</sup> Fabrication |      |

|---------------------|-------|-----------------------------|------|

| 512Mbit             | 120nm | 2000                        | 2001 |

| 1Gbit               | 100nm | 2001                        | 2002 |

| 2Gbit               | 90nm  | 2002                        | 2003 |

| 4Gbit               | 70nm  | 2003                        | 2004 |

| 8Gbit               | 60nm  | 2004                        | 2005 |

| 16Gbit              | 50nm  | 2005                        | 2006 |

| 32Gbit 40nm         |       |                             |      |

| 256Gbit 20nm        |       |                             |      |

Even Tbit would be possible in future!

#### Already 32 Gbit:

larger than that of world population comparable for the numbers of neurons in human brain

Samsung announced 256 Gbit will be produced in 2010. Only 4 years from now.

256Gbit: larger than those of # of stars in galaxies

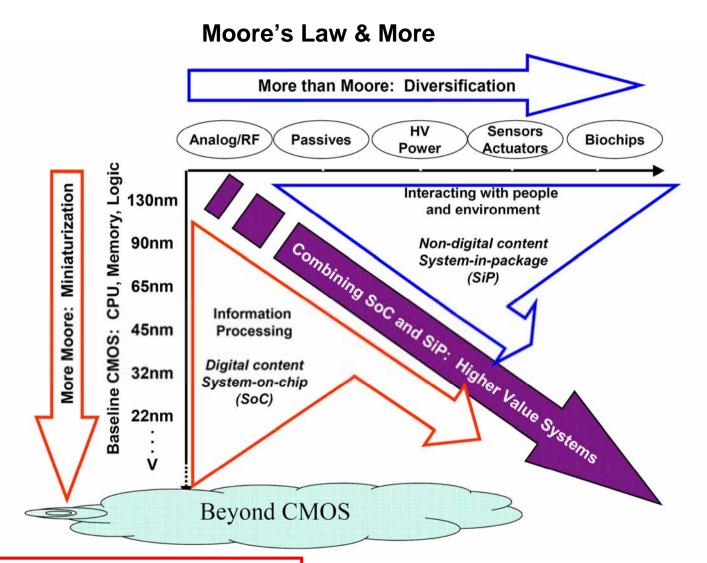

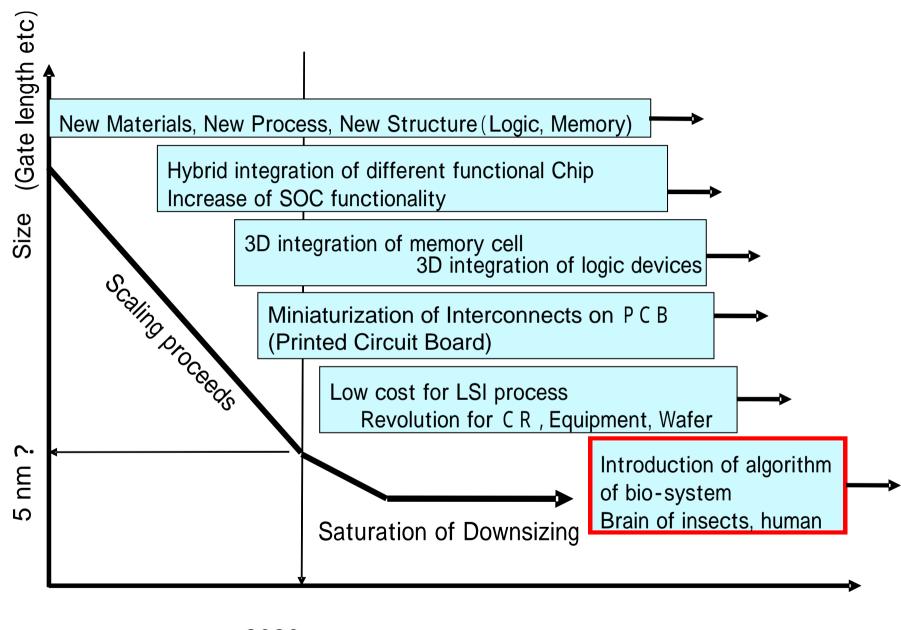

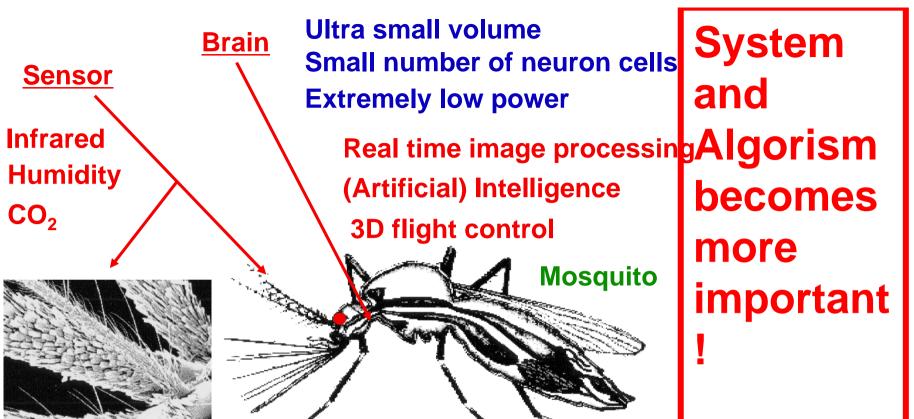

#### More Moore and More than Moore

Question what is the other side of the cloud?

ITRS 2005 Edition

http://strj-jeita.elisasp.net/pdf\_ws\_2005nendo/9A\_WS2005IRC\_Ishiuchi.pdf

We could keep the Moore's law after 2020 Without downswing the gate length

What is Moore's law.

→ to increase the number (#) of Tr. In a chip

Now, # of Tr. in a chip is limited by power.

- → key issue is to reduce the power.

- > to reduce the supply voltage is still effective

To develop devices with sufficiently high drain current under low supply voltage is important.

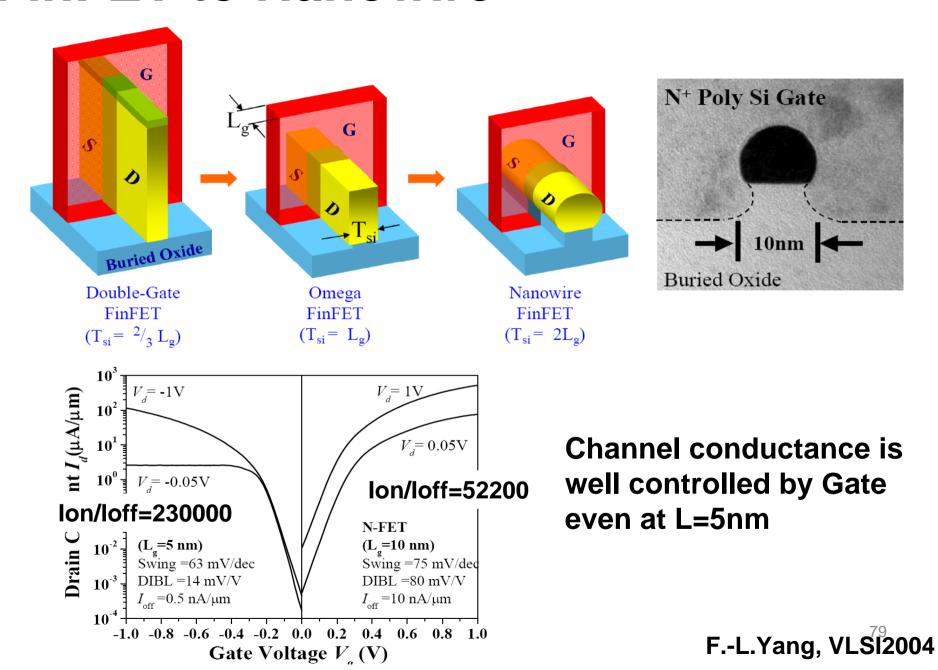

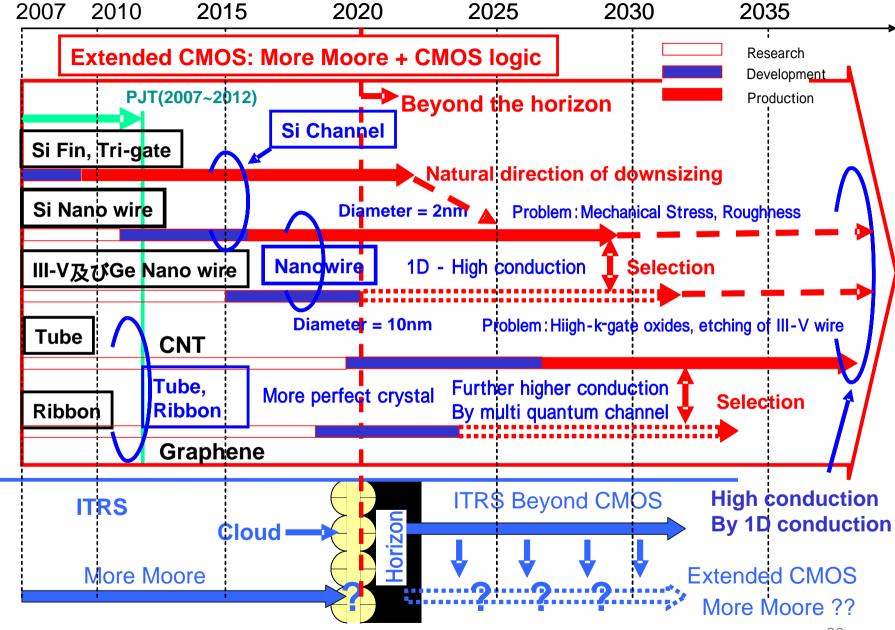

# **FinFET to Nanowire**

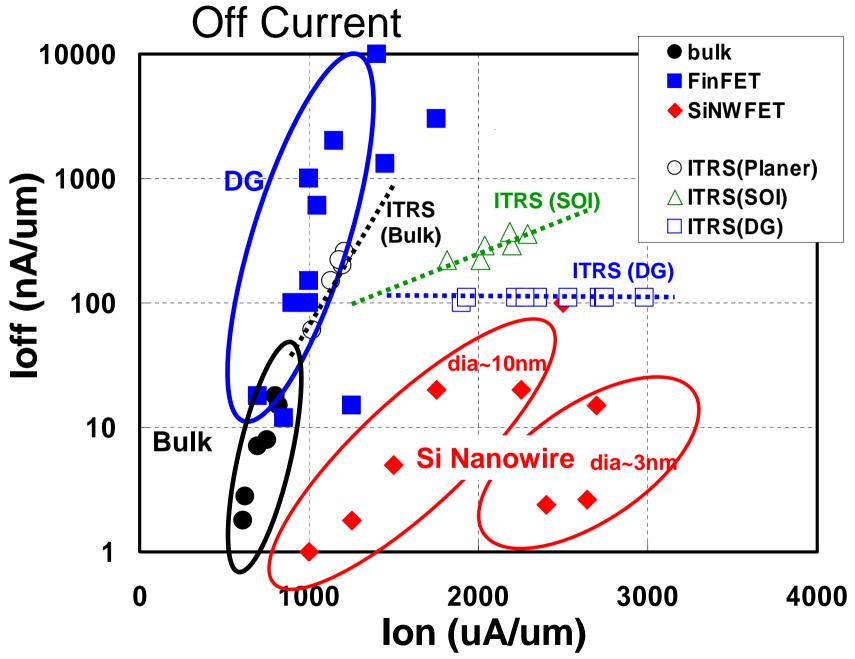

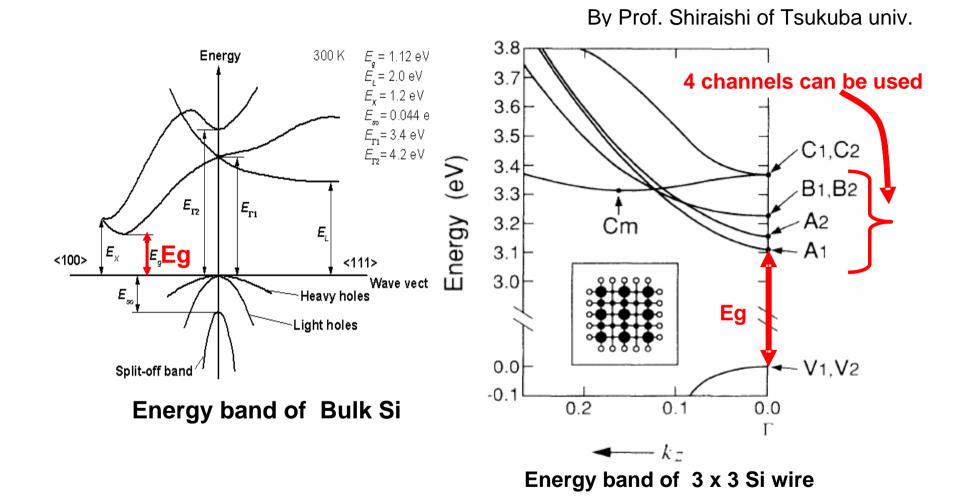

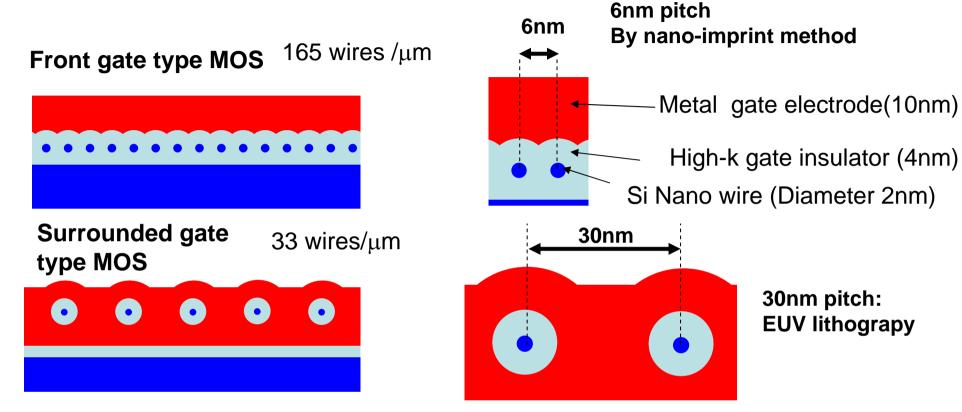

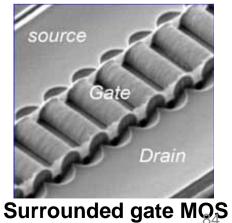

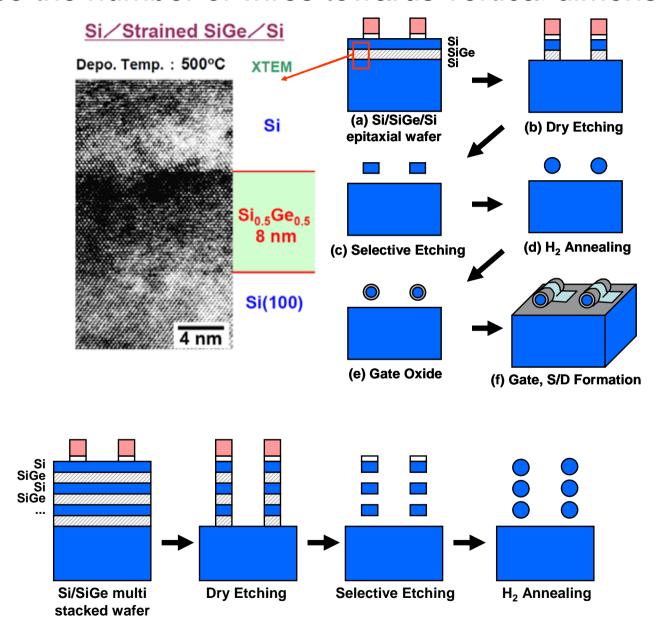

## Selection of MOSFET structure for high conduction: Nano-wire or Nano-tube FETs is promising

3 methods to realize High-conduction at Low voltage M1. Use 1D ballistic conduction

M2. Increase number of quantum channel

M3. Increase the number of wire or tube per area 3D integration of wire and tubes

For suppression of loff, the Nanowire/tube is also good.

1D conduction per one quantum channel:

$G = 2e^2/h = 77.8 \mu S/wire$  or tube regardless of gate length and channel material

That is 77.8 μA/wire at 1V supply

This an extremely high value

However, already 20mA/wire was obtained experimentaly by Samsung

## Increase the Number of quantum channels

### Maximum number of wires per 1 µm

#### Increase the number of wires towards vertical dimension

#### Our new roadmap

Dragonfly is further high performance

# Thank you for your attention!