## Past and future for micro- and nano-electronics, focusing on Si integrated circuits technology

October 24, 2008

Changchun University of Science and Technology

Hiroshi Iwai, Toyo Institute of Technology Needless to say, but....

## <u>CMOS Technology:</u> Indispensible for our human society

## Al the human activities are controlled by CMOS

living, production, financing, telecommunication, transportation, medical care, education, entertainment, etc.

## Without CMOS:

There is no computer in banks, and

world economical activities immediately stop.

Cellarer phone dose not exists

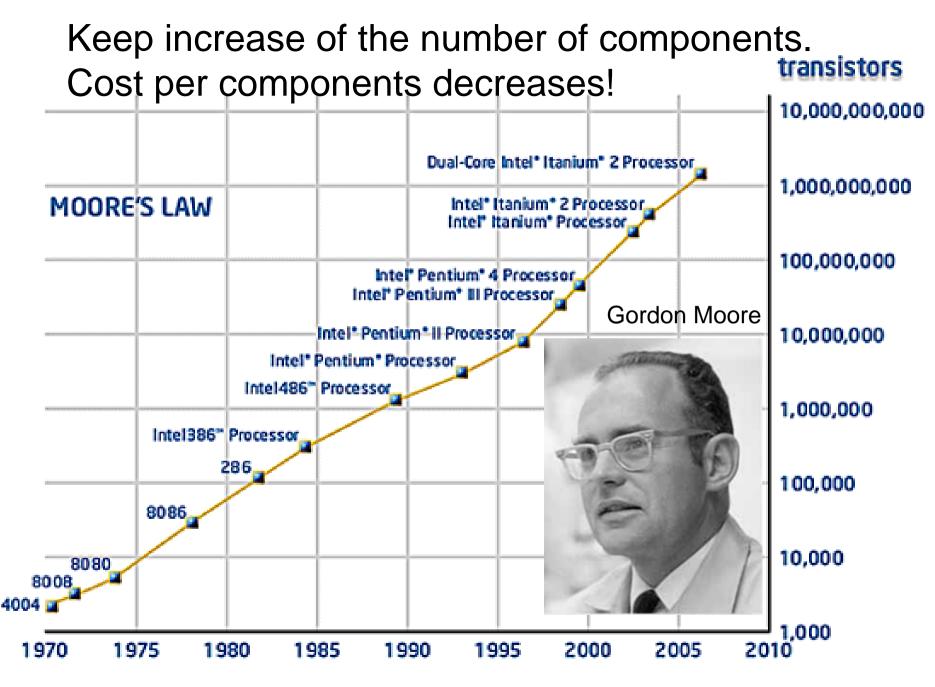

CMOS experienced continuous progress for many years

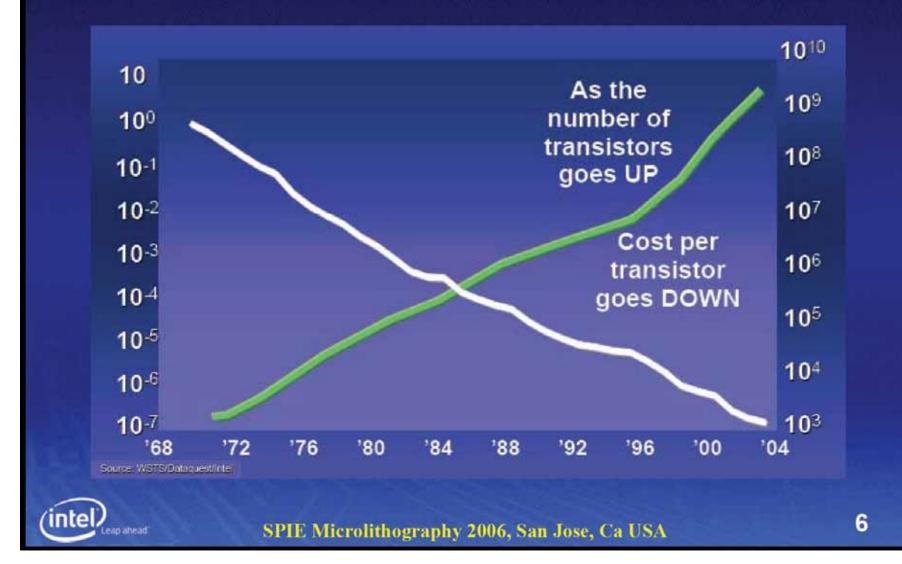

## **Exponential Cost Reduction**

Cost per Transistor

Downsizing of the components has been the driving force for circuit

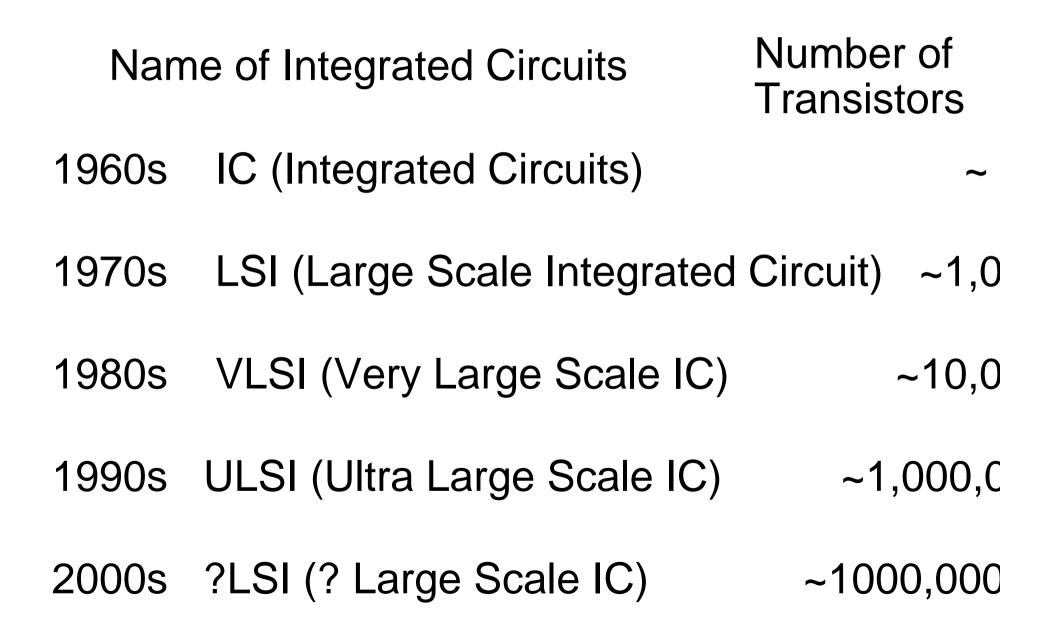

| evolution<br>1900  | ר<br>1950          | 1960               | 1970               | 2000               |

|--------------------|--------------------|--------------------|--------------------|--------------------|

| Vacuum<br>Tube     | Transistor         | IC                 | LSI                | ULSI               |

| 10 cm              | cm                 | mm                 | 10 µm              | 100 nm             |

| 10 <sup>-1</sup> m | 10 <sup>-2</sup> m | 10 <sup>-3</sup> m | 10 <sup>-5</sup> m | 10 <sup>-7</sup> m |

In 100 years, the size reduced by one million times. There have been many devices from stone age. We have never experienced such a tremendous reduction of devices in human history. Downsizing **1. Reduce Capacitance Reduce switching time of MOSFE Reduce power consumption** 2. Increase number of Transistors Increase functionality Parallel processing **Increase circuit operation sp**

Thus, downsizing of Si devices is the most important and critical issue.

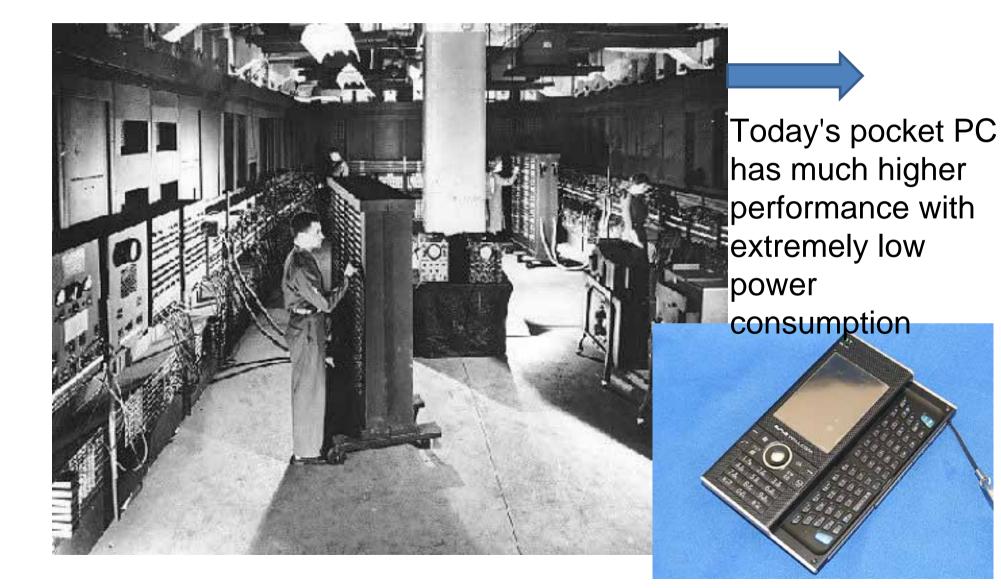

#### First Computer Eniac: made of huge number of vacuum tubes 19<sup>4</sup> Big size, huge power, short life time filament

# Many people wanted to say about the limit.

## Past predictions were not correct!!

| Period       | Expected<br>limit(size) | Cause                        |  |  |  |

|--------------|-------------------------|------------------------------|--|--|--|

| Late 1970's  | 1μm:                    | SCE                          |  |  |  |

| Early 1980's | 0.5µm:                  | S/D resistance               |  |  |  |

| Early 1980's | 0.25µm:                 | Direct-tunneling of gate SiC |  |  |  |

| Late 1980's  | 0.1µm:                  | '0.1µm brick wall'(various)  |  |  |  |

| 2000         | 50nm:                   | 'Red brick wall' (various)   |  |  |  |

| 2000         | 10nm:                   | Fundamental?                 |  |  |  |

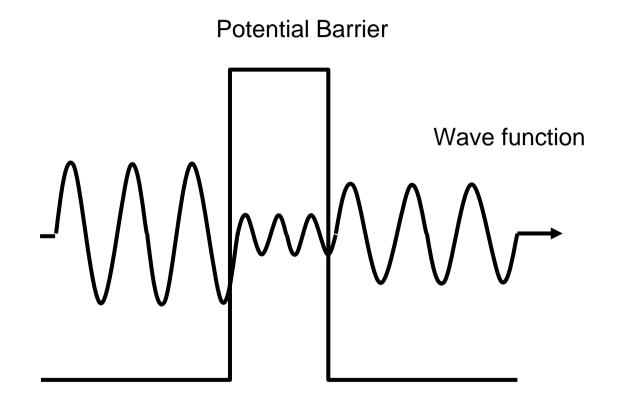

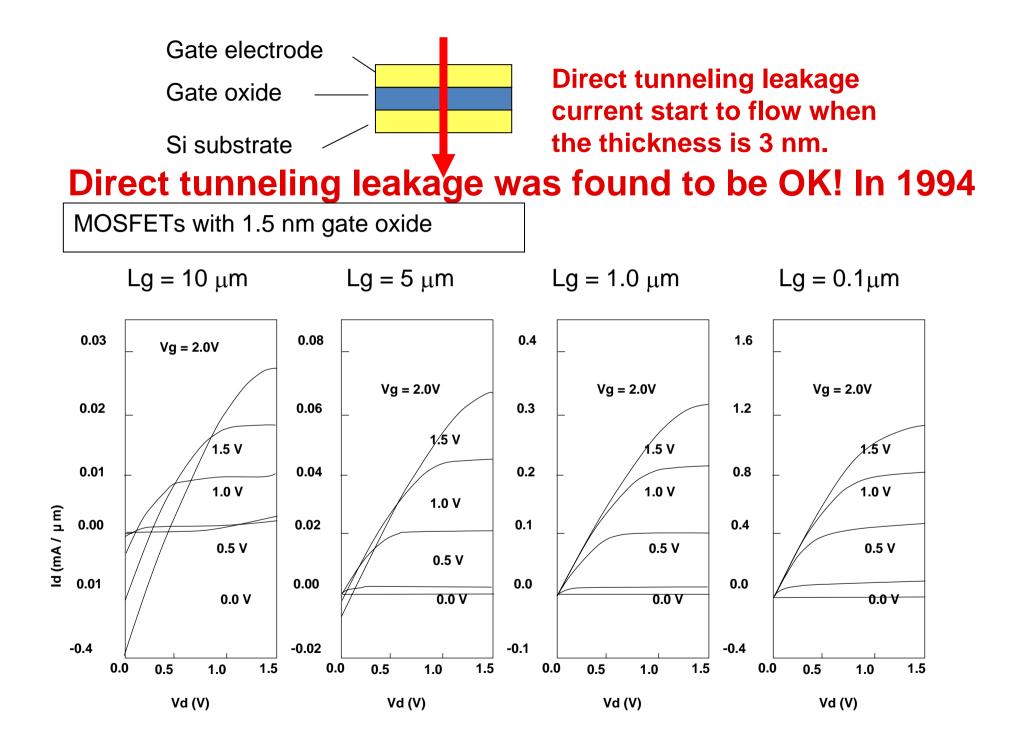

Historically, many predictions of the limit of VSN Soft book written 1979 predict that 0.25 micro-meter would be the limit because of direct-tunneling current through the very thin-gate oxide.

#### **CARVER MEAD · LYNN CONWAY**

| KKKKKKKKKKKKKKKKK                      |  |

|----------------------------------------|--|

| KKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKK |  |

|                                        |  |

| KKKKKKKKKKKKKKKKKKKKKKKK               |  |

| KIKKKKKKK STATES                       |  |

| KKKKKKKKKKKKKKKKKKKKKKKK               |  |

## VLSI textbook

Finally, there appears to be a fundamental limit <sup>10</sup> of approximately quarter micron channel length, where certain physical effects such as the tunneling through the gate oxide and fluctuations in the positions of impurities in the depletion layers begin to make the devices of smaller dimension unworkable.

## Direct-tunneling effect

Do not believe a text book statement, blindly!

**Never Give Up!**

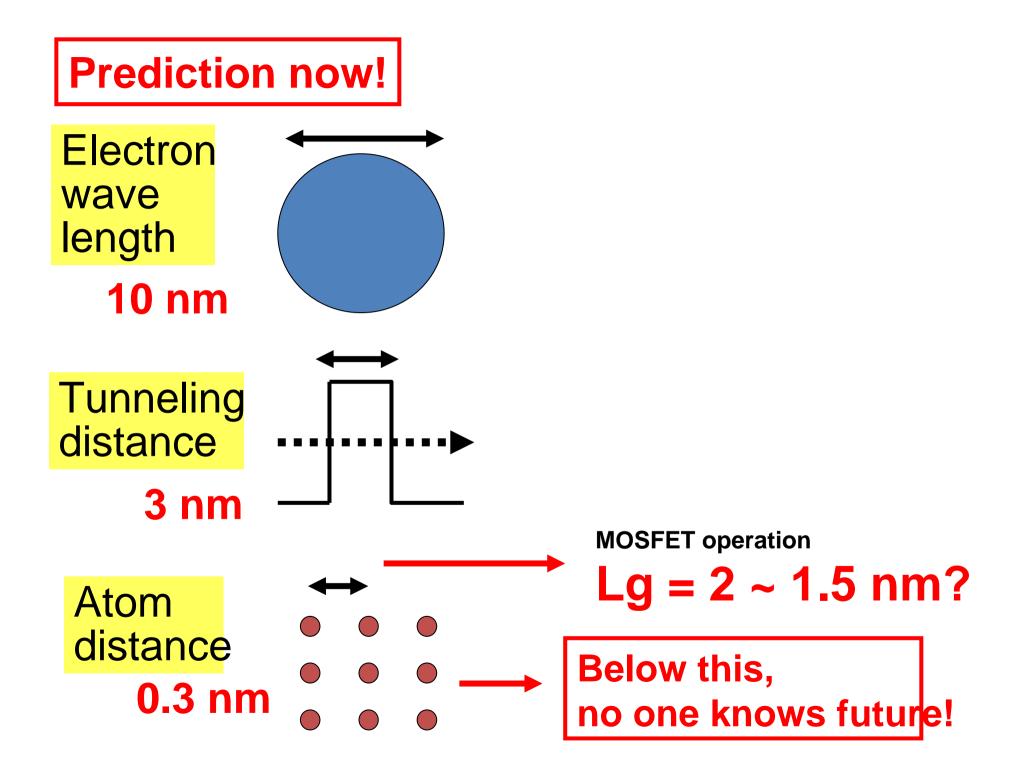

No one knows future!

## There would be a solution!

Think, Think, and Think!

Or, Wait the time! Some one will think for you

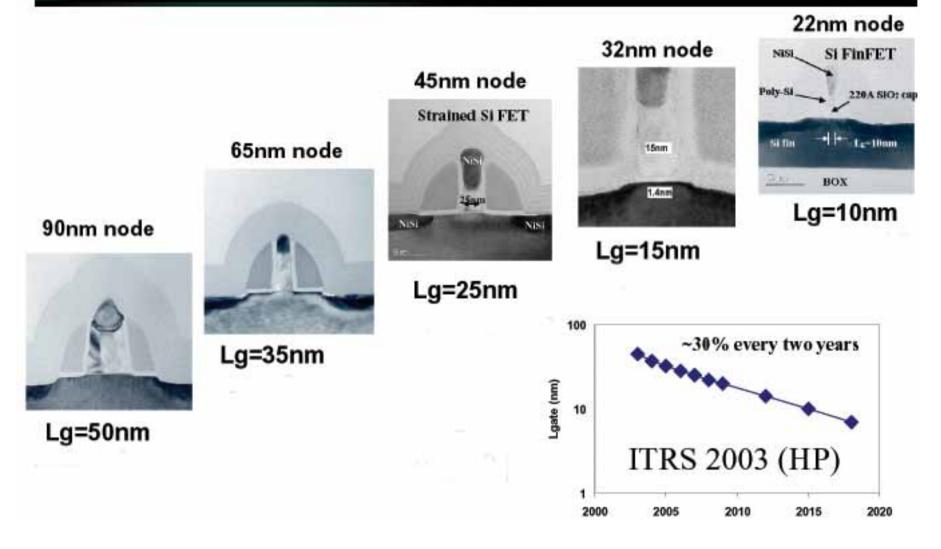

## **Transistor Scaling Continues**

Qi Xinag, ECS 2004, AM

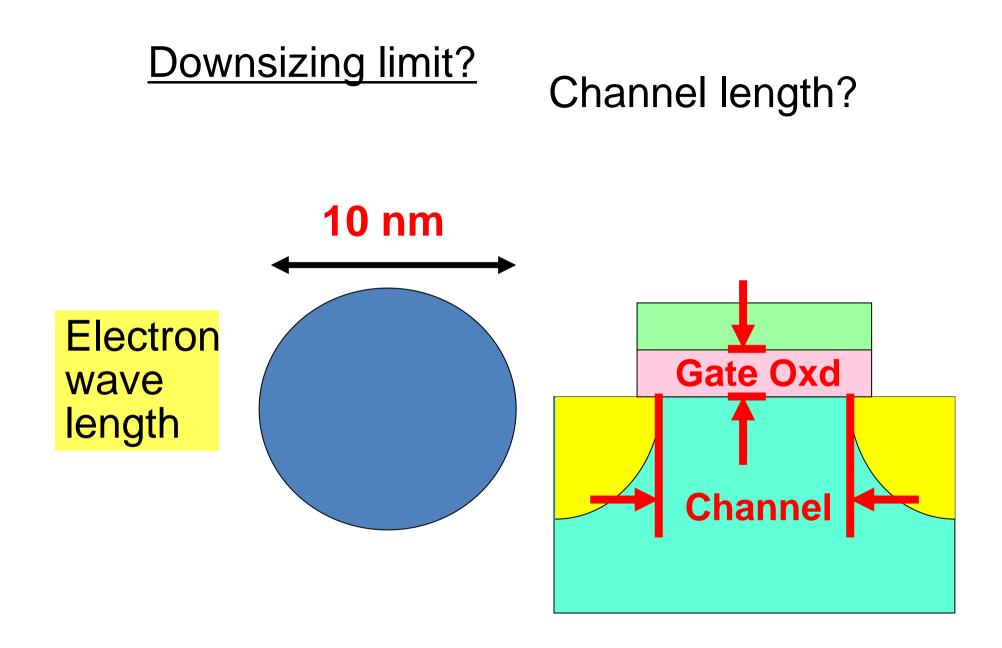

## **Downsizing limit!**

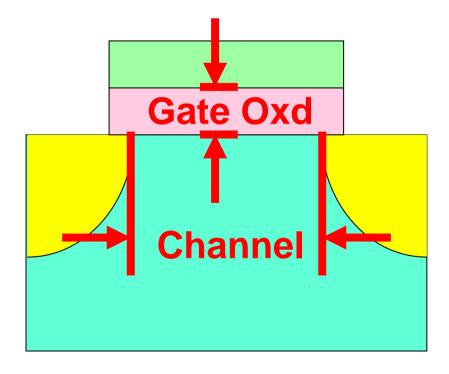

Channel length Gate oxide thickness

History and future of Transistor Shrinking, Shrinking, and Shrinking! and then, Shrinking, Shrinking, and Shrinking

C, V  $\propto$  C: Capacitance/: Voltage

- <sup>L</sup> Switching speed CV/I → Pecrease Power consumption  $CV^2/2$  → Decrease

- Integration density:  $1/L^2 \rightarrow$  Increase

1970 2007

Gate length10,000 nm25 nmGate Oxd Thickness100 nm1 nm

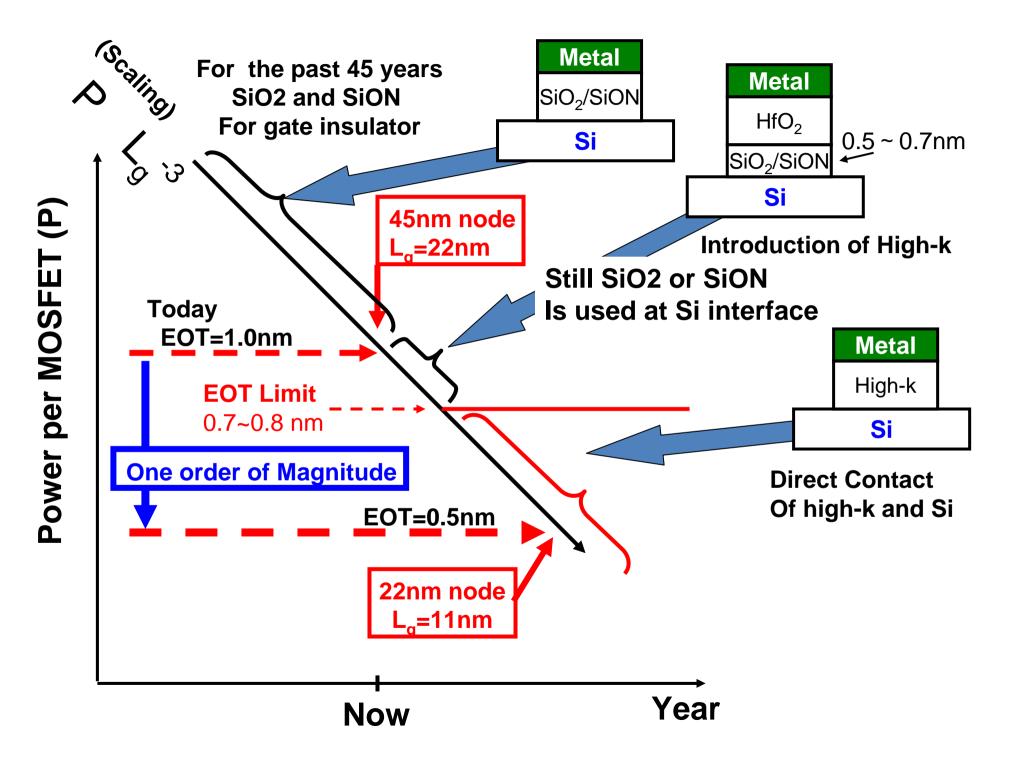

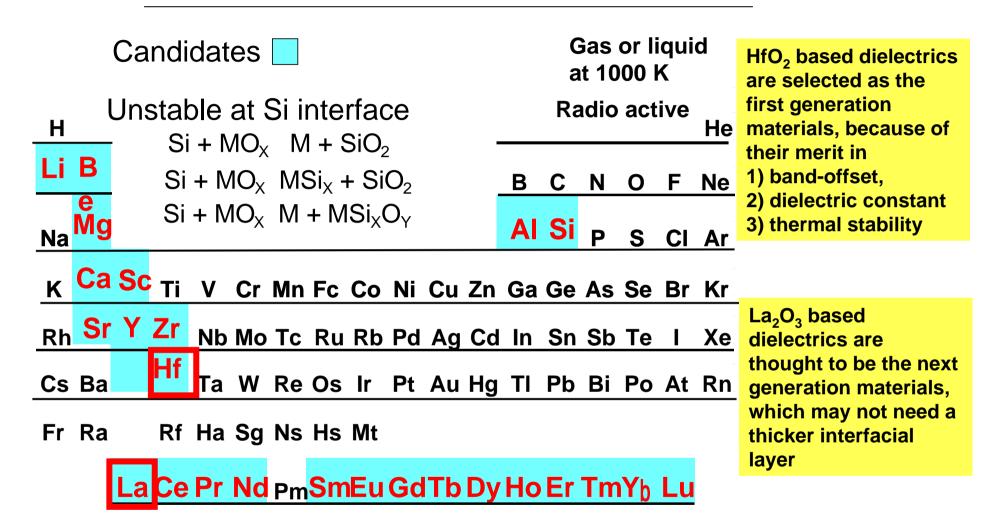

#### Choice of High-k elements for oxide

#### Ac Th Pa U Np Pu AmCm Bk Cf Es Fm Md No Lr

R. Hauser, IEDM Short Course, 1999 Hubbard and Schlom, J Mater Res 11 2757 (1996)

## EOT = 0.48 nm Our results Transistor with La2O3 gate insulator

## <u>CMOS downsizing is critically</u> <u>important</u>

## However now, many people expect that we will reach limit in 2020.

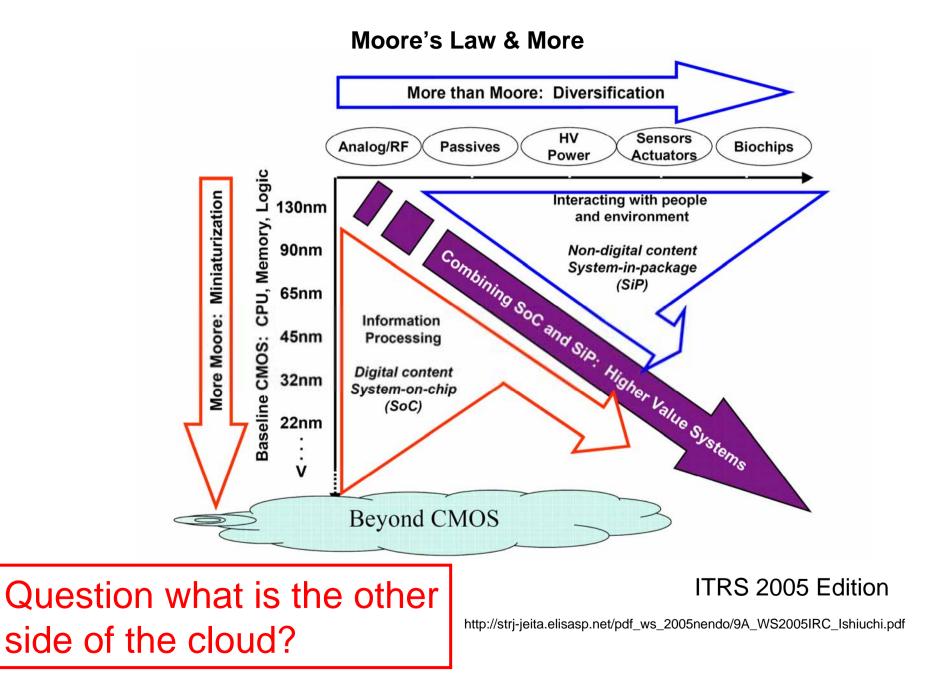

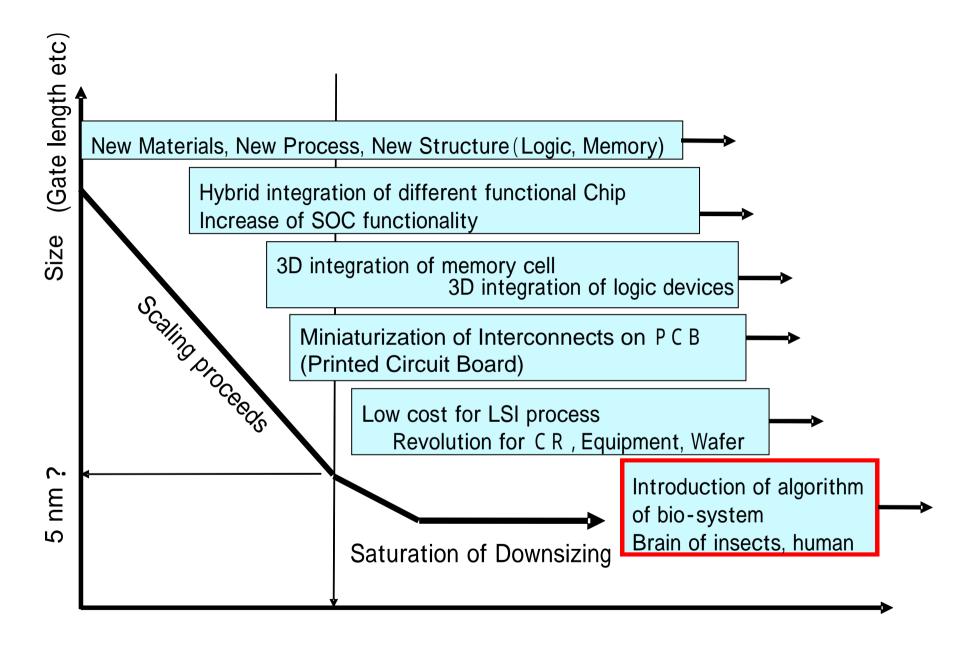

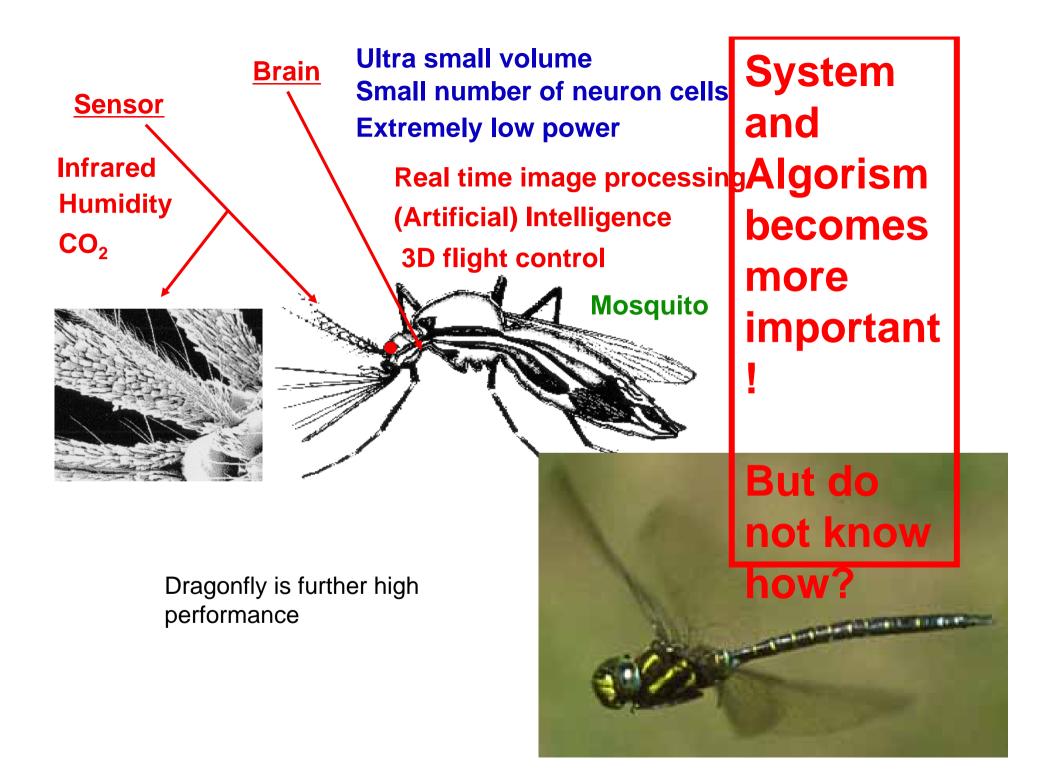

Totally, new paradigm after reaching the downsizing limit.

11/hat will ha?

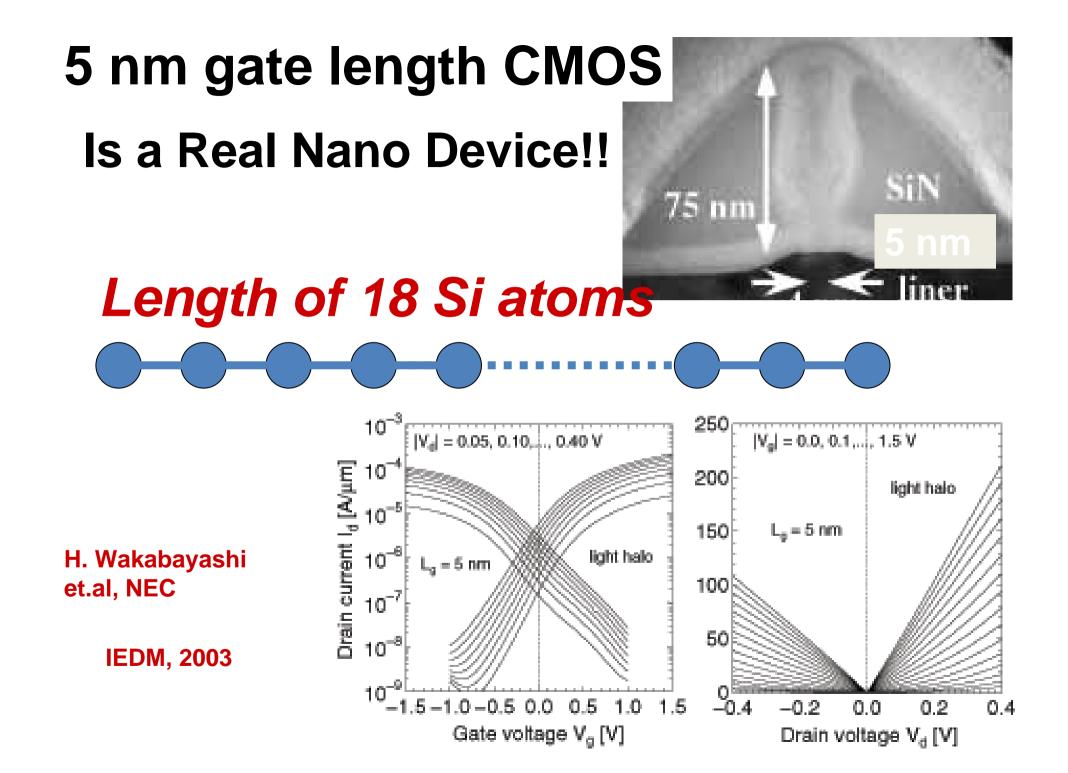

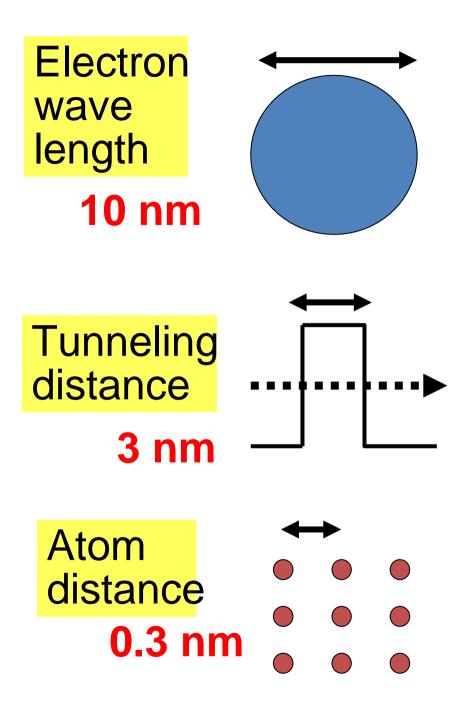

## There is no decrease in gate length around at 10 ~ 5 nm.

4 reasons.

#### After 2020

4 reasons for no downsizing anymore or No decrease in gate length

No increase of On-current (Drain current) because of already semi-ballistic conduction.

Ballistic ← No scattering of carriers in channel Thus, all the carrier from the source reach drain

- 2. Increase of Off-current (Subthreshold current)

- 3. No decrease of Gate capacitance by parasitic components

- 4. Increase in production cost.

## After 2020

What will be the world with no gate length reduction?

#### Victor V. Zhirnov and Ralph K. Cavin III, ECS 207 Washington DC

| Device                                           | FET                 | RSFQ                   | 1D<br>structures    | Resonant<br>Tunneling<br>Devices | SET                    | Molecular             | QCA                  | Spin<br>transistor  |

|--------------------------------------------------|---------------------|------------------------|---------------------|----------------------------------|------------------------|-----------------------|----------------------|---------------------|

| Cell Size                                        | 100 nm              | 0.3 µm                 | 100 nm              | 100 nm                           | 40 nm                  | Not<br>known          | 60 nm                | 100 nm              |

| Density<br>(cm <sup>-2</sup> )                   | 3E9                 | 1E6                    | 3E9                 | 3E9                              | 6E10                   | 1E12                  | 3E10                 | 3E9                 |

| Switch<br>Speed                                  | 700 GH<br>z         | 1.2 THz                | Not<br>known        | 1 THz                            | 1 GHz                  | Not<br>known          | 30 MHz               | 700 GHz             |

| Circuit<br>Speed                                 | 30 GHz              | 250–<br>800 GHz        | 30 GHz              | 30 GHz                           | 1 GHz                  | <1 MHz                | 1 MHz                | 30 GHz              |

| Switching<br>Energy, J                           | 2×10 <sup>-18</sup> | >1.4×10 <sup>-17</sup> | $2 \times 10^{-18}$ | >2×10 <sup>-18</sup>             | >1.5×10 <sup>-17</sup> | $1.3 \times 10^{-16}$ | $>1 \times 10^{-18}$ | $2 \times 10^{-18}$ |

| Binary<br>Throughput,<br>GBit/ns/cm <sup>2</sup> | 86                  | 0.4                    | 86                  | 86                               | 10                     | N/A                   | 0.06                 | 86                  |

We HAVE IDENTIFIED NO VIABLE EMERGING LOGIC TECHNOLOGIES for Information Processing beyond CMOS We could keep the Moore's law after 2020 Without downswing the gate length

What is Moore's law.

http://www.intel.com/technology/mooreslaw/index.htm

We could keep the Moore's law after 2020 Without downswing the gate length

What is Moore's law.

$\rightarrow$  to increase the number (#) of Tr. In a chip

Now, # of Tr. in a chip is limited by power.

- $\rightarrow$  key issue is to reduce the power.

- $\rightarrow$  to reduce the supply voltage is still effective

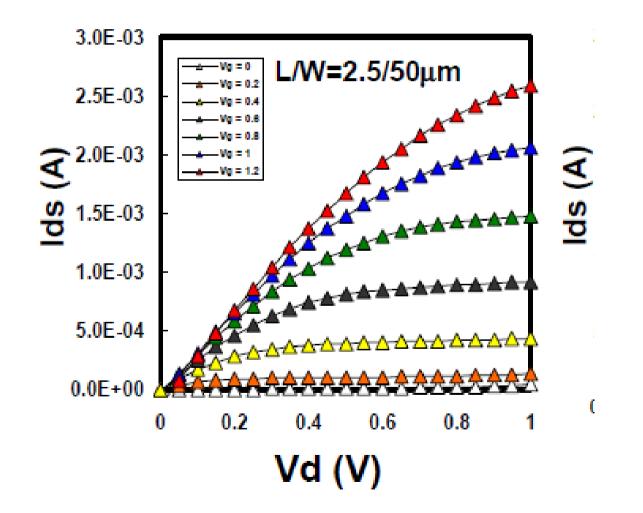

To develop devices with sufficiently high drain current under low supply voltage is important.

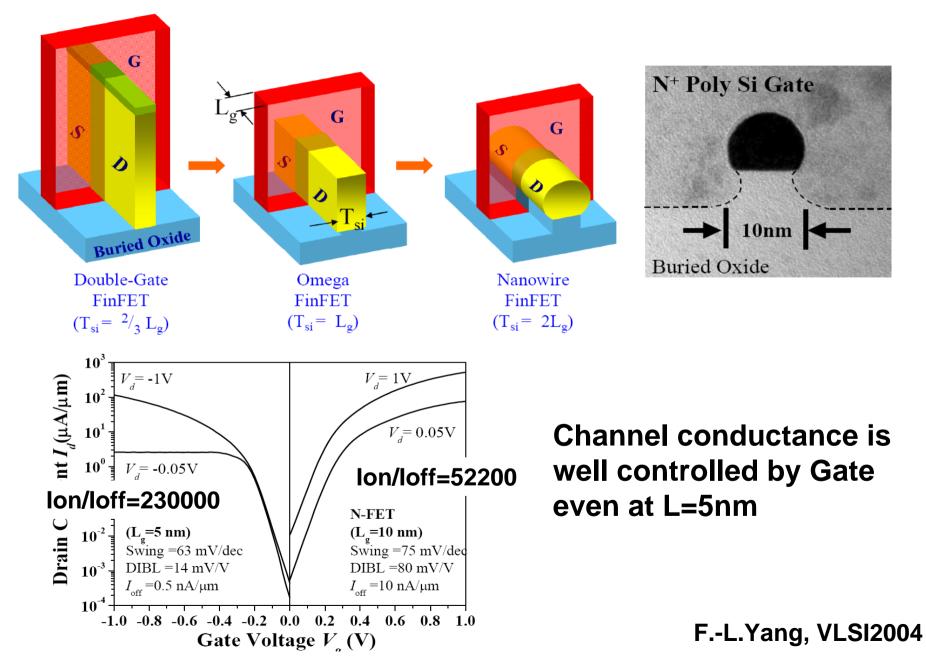

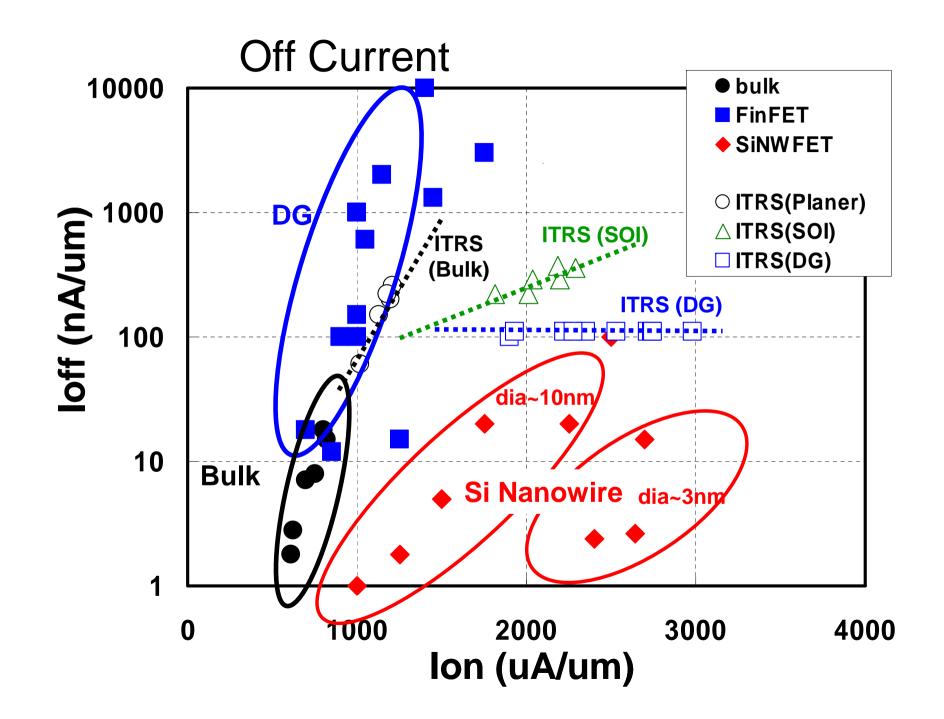

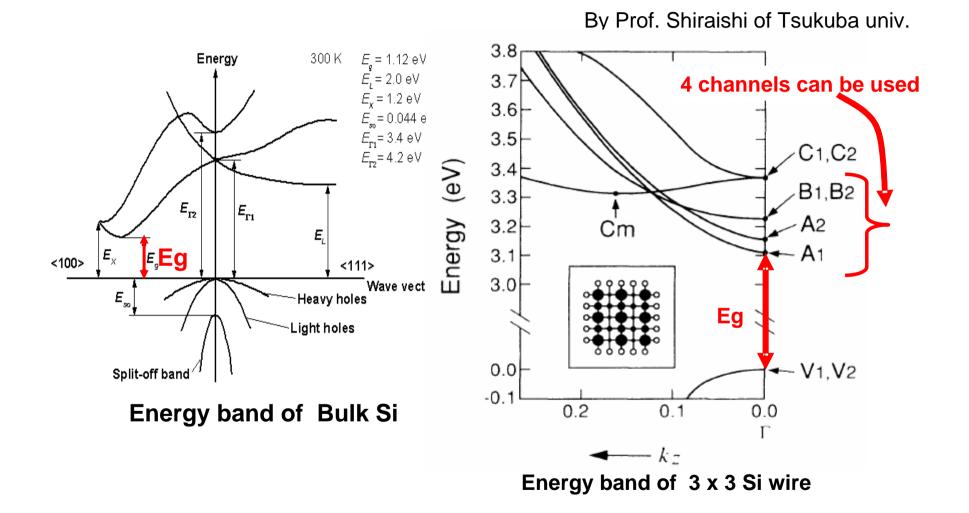

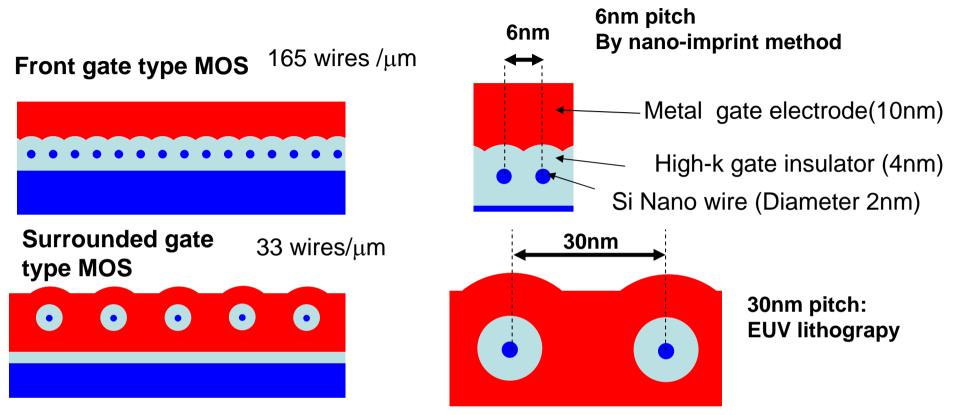

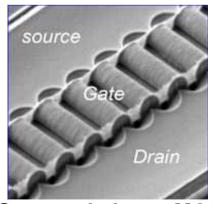

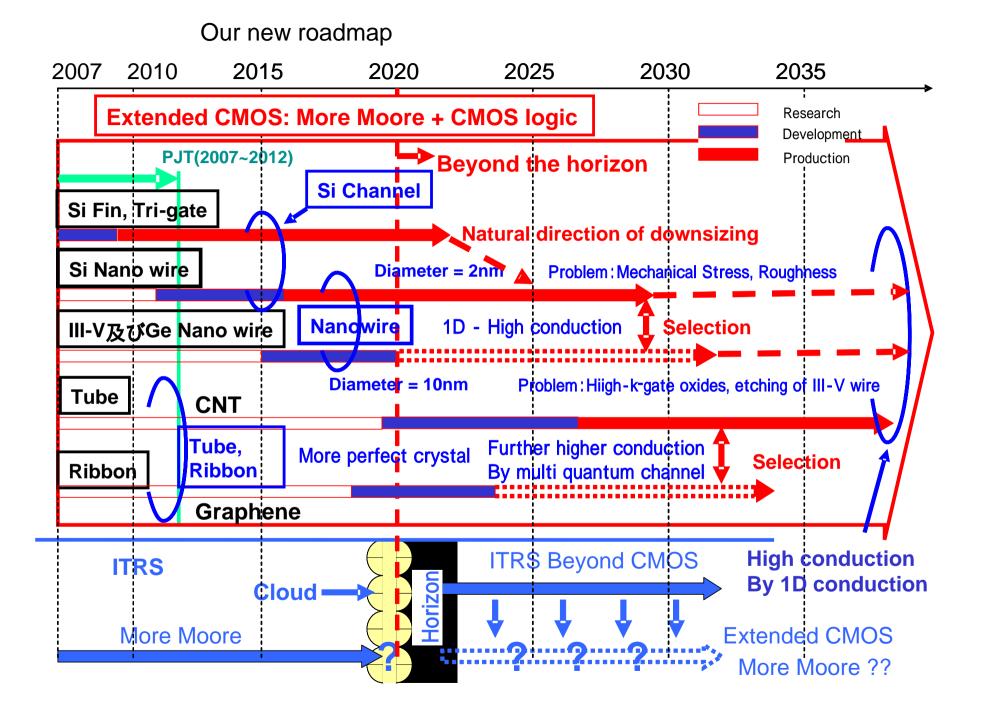

## **FinFET to Nanowire**

Selection of MOSFET structure for high conduction: Nano-wire or Nano-tube FETs is promising

3 methods to realize High-conduction at Low voltage M1. Use 1D ballistic conduction

M2. Increase number of quantum channel

M3. Increase the number of wire or tube per area 3D integration of wire and tubes

For suppression of loff, the Nanowire/tube is also good.

1D conduction per one quantum channel:  $G = 2e^2/h = 77.8 \mu S/wire \text{ or tube}$ regardless of gate length and channel material

That is 77.8 µA/wire at 1V supply

This an extremely high value

However, already 20mA/wire was obtained experimentaly by Samsung

#### **Increase the Number of quantum channels**

### Maximum number of wires per 1 $\mu$ m

Surrounded gate MOS

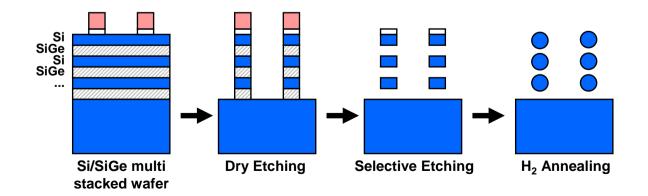

#### Si/Strained SiGe/Si Si SiGe Si Depo. Temp. : 500°C **XTEM** (a) Si/SiGe/Si Si (b) Dry Etching epitaxial wafer Si<sub>0.5</sub>Ge<sub>0.5</sub> 8 nm (d) H<sub>2</sub> Annealing (c) Selective Etching $\bigcirc$ Si(100) 4 nm (e) Gate Oxide (f) Gate, S/D Formation

#### Increase the number of wires towards vertical dimension

2020 ?

# Thank you for your attention!