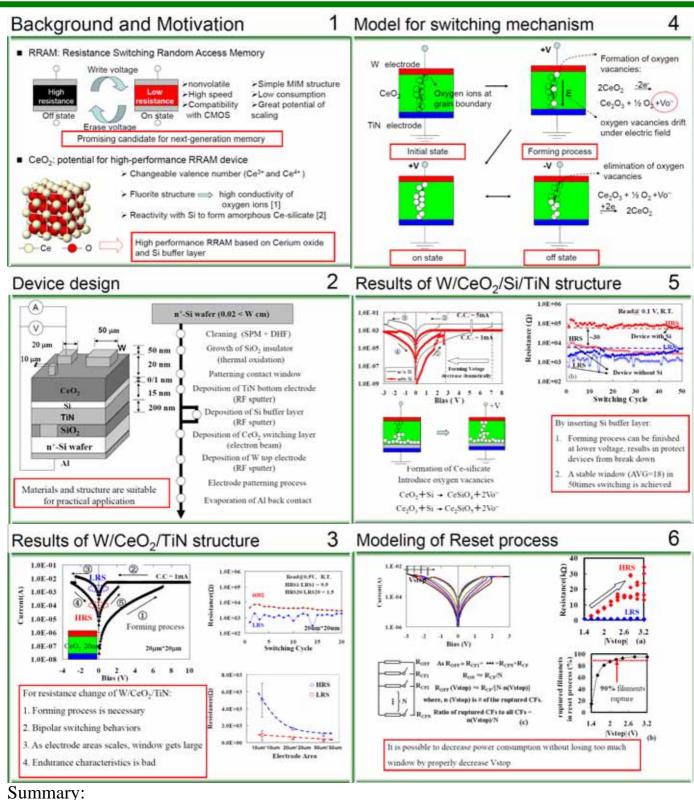

## Feasibility study of Ce oxide for resistive RAM application

C. Dou<sup>1</sup>, K. Mukai<sup>1</sup>, K. Kakushima<sup>2</sup>, P.Ahmet<sup>1</sup>, K.Tsutsui<sup>2</sup>, A. Nishiyama<sup>2</sup>, N. Sugii<sup>2</sup>, K. Natori<sup>1</sup>, T. Hattori<sup>1</sup>, H. Iwai<sup>1</sup> Tokyo Tech. FRC<sup>1</sup>, Tokyo Tech. IGSSE<sup>2</sup>

- 1. The resistive switching behaviors of  $CeO_2$  based ReRAM have been confirmed.

- 2. Si buffer layer is able to improve  $\text{CeO}_2$  based ReRAM device by forming Ce-silicate at interface.

- 3. A guideline for reset process control of the  $W/CeO_2/Si/TiN$  device is provided..