## 超薄い High-k ゲートスタック MOSFET における電子移動度の劣化

Electron mobility degradation in ultrathin high-k gate stacked MOSFETs 東工大フロンティア研<sup>1</sup>,東工大総理工<sup>2</sup> Mamat Mamatrishat<sup>1</sup>,角嶋邦之<sup>2</sup>, Parhat

Ahmet<sup>2</sup>,筒井一生<sup>2</sup>,西山彰<sup>2</sup>,杉井信之<sup>2</sup>,名取研二<sup>1</sup>,岩井洋 <sup>1</sup>

Tokyo Tech.FRC<sup>1</sup>, Tokyo Tech. IGSSE<sup>2</sup>, <sup>o</sup>M. Mamatrishat<sup>1</sup>, K. Kakushima<sup>2</sup>, P. Ahment<sup>1</sup>, K. Tsutsui<sup>2</sup>, A. Nishiyama<sup>2</sup>, N. Sugii<sup>2</sup>, K. Natori<sup>1</sup>, H. Iwai<sup>1</sup>

## E-mail: mamat.m.aa@m.titech.ac.jp

**【Introduction】** The mobility degradation is one of the main concerns in high-k gate stacked MOSFETs. For high-k/Si-substrate direct contacted ultrathin high-k gate stacked MOSFETs, remote scattering mechanisms (remote Coulomb, remote surface roughness, and also remote phonon) may also contribute to mobility degradation. In this report, we studied remote surface roughness (RSR) scattering limited electron mobility in CeO<sub>2</sub> capped La<sub>2</sub>O<sub>3</sub> high-k MOSFETs.

**[Experiment]** Fabrication of nMOSFET started from a source/drain pre-formed p-Si (100) substrate. The high- $\kappa$  dielectric thin films (La<sub>2</sub>O<sub>3</sub> and CeO<sub>2</sub>) were deposited by electron-beam evaporation system in an ultra-high vacuum at a temperature of 300 °C. Then a metal W (thickness of 50 nm) was sputtered in the radio frequency (RF)-sputtering chamber. After defining the gate area, annealing in the forming gas (N<sub>2</sub>:H<sub>2</sub> = 97:3) was performed at a temperature of 500 °C for 30 min. Then after patterning the source/drain by lithography and RI etching, a metal Al was evaporated to the source/drain, and backside electrode contact. The effective mobility of the fabricated nMOSFETs is experimentally measured by I-V, and the split C-V method at 1 MHz.

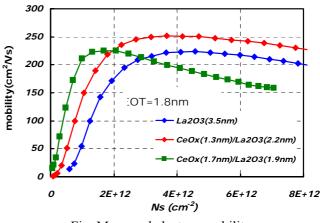

**[ Results and discussion ]** Figure shows measured electron mobility for  $La_2O_3$  single layer and  $CeO_x/La_2O_3$  gate stacked nMOSFETs. The total physical thicknesses of the high-k layers in all samples are

same. The distance from the interface of  $CeO_x/La_2O_3$  to surface of the Si substrate is intentionally decreased. The mobility of the  $CeOx(1.3nm)/La_2O_3(2.2nm)$  gate stacked MOSFET is increased compare to the mobility of the  $La_2O_3(3.5nm)$  gate stacked MOSFETs. This can be understood that the amount of fixed charges in the gate stack is decreased by  $CeO_x$  capping on the  $La_2O_3$  layer. While the thickness

of the La<sub>2</sub>O<sub>3</sub> is decreasing and the thickness of the CeO<sub>x</sub> is increasing, the interface of CeO<sub>x</sub>/La<sub>2</sub>O<sub>3</sub> is more close to the Si substrate. This might strength the effect of remote surface roughness scattering on the mobility of the channel electrons. As a result, the mobility is decreased in the CeOx(1.7nm)/La<sub>2</sub>O<sub>3</sub>(1.9nm) gate stacked MOSFET.

Acknowledgement: This work was supported by NEDO, NEC C&C, and G-COE PICE of TIT.