## **Doctoral Thesis**

# A Study on Carrier Transport Properties of Vertically-Stacked Nanowire Transistors

A DISSERTATION SUBMITTED TO THE

DEPARTMENT OF ELECTRONICS AND APPLIED PHYSICS

INTERDISCIPLINARY GRADUATE SCHOOL OF

SCIENCE AND ENGINEERING

TOKYO INSTITUTE OF TECHNOLOGY

FOR THE DEGREE OF DOCTOR OF ENGINEERING

# Kiichi Tachi

March 2011

Supervisor: Professor Hiroshi Iwai

#### **ABSTRACT**

Vertically-stacked silicon nanowire MOSFETs (SNWTs) were experimentally investigated as one of the possible solutions to achieve both high speed, low power consumption in combination with high integration capabilities for future LSI applications. To evaluate the potentials, analyze and improve the performance of these devices, source/drain series resistance for thick source/drain region were studied. Carrier transport mechanisms and the controllability of threshold voltage for vertically-stacked SNWTs with separated gates were also investigated.

The influence of *in situ* doped SEG source/drain was examined for vertically-stacked channel MOSFETs. A large enhancement, by a factor of 2 in the drive current, was obtained when *in situ* doped SEG process was adopted. Detailed parameter extraction from the electrical measurements showed the  $R_{SD}$  values can be reduced by 90 and 75% for n- and p-FETs, respectively, when in situ doped SEG is reinforced by adding ion implantation. On the other hand, by combining the ion implantation to SEG process,  $V_T$  roll-off characteristics and the effective mobility behavior are slightly degraded. Mobility analysis revealed an increase in the Coulomb scattering with  $L_G$  scaling, indicating the diffusion of dopant atoms from S/D regions. Further improvements in the performance can be sought by optimizing the S/D activation annealing step.

In order to enhance the performance of the vertically-stacked nanowire MOSFETs, the carrier transport limiting components caused by short channel effects were assessed. The optimization of drive currents will have to take into account specific effects to vertically-stacked SNWTs. In particular, the use of SiGe sacrificial layer to make vertically-stacked channels cause large mobility degradation due to the surface roughness, resulted from the damage of plasma etching. This leads to the poor ballisticity in the short channel SNWTs. Hydrogen annealing was shown to be advantageous for improving the surface-roughness limited mobility. Charge pumping measurements, however, revealed that circular-shaped SNWTs, which are formed by annealing, have a higher interface trap density ( $D_{it}$ ) than rectangular ones, leading to low-field mobility degradation. This high  $D_{it}$  could be caused by the

Abstract

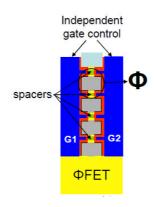

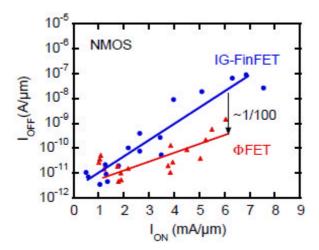

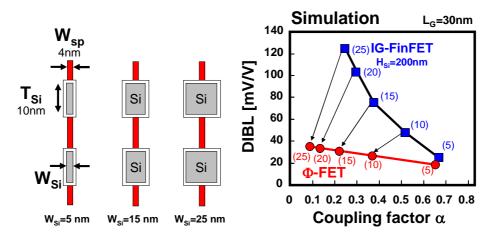

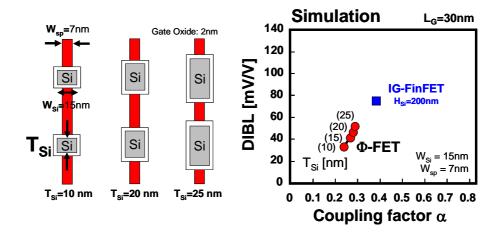

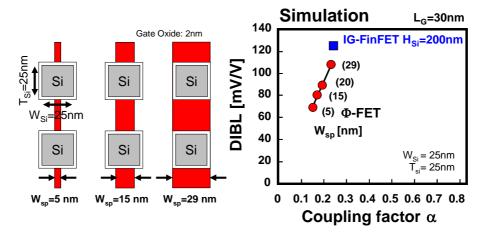

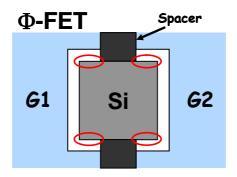

continuously-varying surface orientation. The resulting additional coulomb scattering could partly explain the quite low mobility in 5 nm diameter SNWTs together with the already known transport limitations in NWs. Vertically-stacked SNWTs with independent gates by internal spacers between the nanowires to control threshold voltage (named  $\Phi$ -FETs), were evaluated.  $\Phi$ -FETs demonstrated excellent  $V_T$  controllability due to inter-gate coupling effects. Numerical simulations to optimize  $\Phi$ -FETs structures show that when the spacer width is reduced, the DIBL value can be lowered by a factor of 2 compared to independent-gate FinFETs with the same silicon width. The superior scaling of  $\Phi$ -FETs with narrow spacer results from a better electrostatic control which also attenuates the inter-gate coupling.

Overall it was shown that using vertical stack structure can increase the drive current density while allowing for better threshold voltage controllability. As for the performance benchmark, nanowires with a diameter of 10 nm, showed the most acceptable balance between mobility, short channel effect. However, to further improve the device performance, process induced surface damage of nanowires must be mitigated.

#### **ACKNOWLEDGEMENTS**

I would like to thank, first and foremost, my supervisor, Professor Hiroshi Iwai of Tokyo Institute of Technology for his guidance, encouragement and continuous support throughout my research.

I am also grateful to Professor Kenji Natori, Professor Kazuo Tsutsui, Professor Eisuke Tokumitsu, Professor Masahiro Watanabe and Professor Shun-ichiro Ohmi of Tokyo Institute of Technology for reviewing the thesis and for valuable advice.

All studies referred to in this thesis were performed at CEA-Leti in France during the last three years. I am indebted to everyone with whom I have worked at CEA-Leti over the years.

I am also grateful to Dr. Simon Deleonibus, Dr. Olivier Faynot and Dr. Thomas Ernst of CEA-Leti's Electronics Nanodevices Laboratory, and Professor Sorin Cristoloveanu of Grenoble Institute of Technology for their encouragement, useful advices and great help whenever I met difficult and subtle problem.

I would like to thank Professor Kuniyuki Kakushima, Professor Parhat Ahmet, Professor Nobyuki Sugii, and Professor Akira Nishiyama of Tokyo Institute of Technology for their encouragement support of my studies.

I am also grateful to research colleagues of Iwai's Laboratory for the kind friendship.

I would like to express sincere gratitude to laboratory secretaries, Ms. M. Karakawa, Ms. A. Matsumoto, and Ms. M. Nishizawa for their invaluable assistance regarding administrative issues.

This work was partially performed as part of the IBM-STMicroelectronics-CEA-LETI Development Alliance. To my family for their kind support and encouragement throughout my life.

Merci beaucoup!

# **CONTENTS**

|     |          |          |                                                        | Page  |

|-----|----------|----------|--------------------------------------------------------|-------|

| Lis | st of To | ables    |                                                        | xi    |

| Lis | st of F  | igures   |                                                        | xiii  |

| Sy  | mbols    | and Abb  | previations                                            | xxiii |

| 1   | Intr     | oduction | n – MOSFET Scaling –                                   | 1     |

|     | 1.1      | MOSF     | ET Downsizing                                          | 3     |

|     |          | 1.1.1    | Basic CMOS Operation                                   |       |

|     |          | 1.1.2    | MOSFET Scaling                                         |       |

|     |          | 1.1.3    | CMOS Performance Indexes                               |       |

|     | 1.2      | Short C  | Channel MOSFET                                         | 18    |

|     |          | 1.2.1    | Short Channel Effects                                  |       |

|     |          | 1.2.2    | Source/Drain Series Resistance in Short-Channel MOSFET |       |

|     |          | 1.2.3    | Carrier Transport Mechanisms in Short-Channel MOSFET   |       |

|     | 1.3      | Key Te   | chnologies to Improve MOSFET Performance               | 30    |

|     |          | 1.3.1    | Gate-All-Around Silicon Nanowire MOSFET                |       |

|     |          | 1.3.2    | Vertically-Stacked Channel MOSFET                      |       |

|     | 1.4      | Purpos   | e and Contents of This Study                           | 39    |

|     | 1.5      | Referen  | nces                                                   | 43    |

| 2 | Ver | tically-Stacked Channel MOSFET Fabrication                   | 49 |

|---|-----|--------------------------------------------------------------|----|

|   | 2.1 | Silicon-On-Nothing Technology                                | 51 |

|   | 2.2 | Process Step Overview for Multi-Channel MOSFET               | 52 |

|   | 2.3 | Process Step Overview for Vertically-Stacked Nanowire MOSFET | 54 |

|   | 2.4 | Key Steps                                                    | 59 |

|   |     | 2.4.1 High-k/Metal Gate Stacks                               |    |

|   |     | 2.4.2 SiGe Epitaxy and Etching                               |    |

|   | 2.5 | Conclusions                                                  | 60 |

|   | 2.6 | References                                                   | 61 |

|   |     |                                                              |    |

| 3 | Ele | ctrical Characterization Methods                             | 63 |

|   | 3.1 | Introduction                                                 | 65 |

|   | 3.2 | <i>Y</i> -function Method                                    | 65 |

|   | 3.3 | Split <i>C–V</i> Method                                      | 69 |

|   | 3.4 | Conclusions                                                  | 72 |

|   | 3.5 | References                                                   | 72 |

| 4 | Sou | rce/Drain Doping Techniques for Vertically-Stacked Channel   |    |

|   | Str | icture                                                       | 73 |

|   | 4.1 | Introduction                                                 | 75 |

|   | 4.2 | Experimental Conditions                                      | 76 |

|   | 4.3 | Electrical Characteristics                                   | 76 |

|   |     | 4.3.1 <i>I–V</i> Characteristics                             |    |

|   |     | 4.3.2 Source/Drain Series Resistance Evaluation              |    |

|   |     | 4.3.3 Carrier Mobility Evaluation                            |    |

|   |     | 4.3.4 Gate Length Scaling                                    |    |

|   | 4.4 | Conclusions                                                  | 85 |

|   | 4.5 | References                                                   | 86 |

| 5 |     | rier Transport Properties of Vertically-Stacked Nanowire<br>SFETs   | 87  |

|---|-----|---------------------------------------------------------------------|-----|

|   | 5.1 | Introduction                                                        | 90  |

|   | 5.2 | Electrical Characteristics                                          | 90  |

|   |     | 5.2.1 <i>I–V</i> Characteristics                                    |     |

|   |     | 5.2.2 Transport Limiting Velocity                                   |     |

|   |     | 5.2.3 Carrier Mobility Evaluation                                   |     |

|   |     | 5.2.4 Mobility Limiting Factors                                     |     |

|   | 5.3 | Impact on Plasma Etching of SiGe Sacrificial layers                 | 102 |

|   |     | 5.3.1 One-Leveled Nanowire MOSFET Fabrication                       |     |

|   |     | 5.3.2 Carrier Mobility Evaluation                                   |     |

|   | 5.4 | Effect of Hydrogen Annealing                                        | 106 |

|   |     | 5.4.1 Cross-Sectional Shape                                         |     |

|   |     | 5.4.2 Carrier Mobility Evaluation                                   |     |

|   |     | 5.4.3 Interface Trap density                                        |     |

|   | 5.5 | SiGe Nanowire MOSFET                                                | 110 |

|   |     | 5.5.1 Device Fabrication Process                                    |     |

|   |     | 5.5.2 <i>I–V</i> Characteristics                                    |     |

|   |     | 5.5.3 Carrier Mobility Evaluation                                   |     |

|   |     | 5.5.4 Noise Measurement                                             |     |

|   | 5.6 | Conclusions                                                         | 113 |

|   | 5.7 | References                                                          | 114 |

| 6 | Thi | reshold Voltage Control of Vertically-Stacked Nanowire MOSFETs      | 117 |

|   | 6.1 | Introduction                                                        | 119 |

|   |     | 6.1.1 Threshold Voltage Control by Independent-Gate FinFET          |     |

|   |     | 6.1.2 Vertically-Stacked Nanowire Transistor with Independent Gates |     |

|   | 6.2 | Optimization of Device Dimensions                                   | 122 |

|   | 6.3 | Conclusions                                                         | 128 |

|   | 6.4 | References                                                          | 128 |

|    |        |                              | <u>Contents</u> |

|----|--------|------------------------------|-----------------|

|    |        |                              |                 |

| 7  | Con    | ıclusions                    | 130             |

|    | 7.1    | Summary                      | 132             |

|    | 7.2    | Conclusions and Perspectives | 134             |

| Pu | blicat | tions and Presentations      | 135             |

|    | vards  |                              | 143             |

|    |        |                              |                 |

# LIST OF TABLES

| Introduction – MOSFET scaling –                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Constant-field scaling and generalized scaling of MOSFET device                                                                                                                                                                                                                                                                                                          | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| •                                                                                                                                                                                                                                                                                                                                                                        | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Natural length in devices with different geometries [1.32].                                                                                                                                                                                                                                                                                                              | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Vertically-Stacked Channel MOSFET Fabrication                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Nanowire width with various definitions and surface gain factor $W_{eff}/W_{Top}$ .                                                                                                                                                                                                                                                                                      | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Process description of anisotropic etching of SiGe/Si superlattice                                                                                                                                                                                                                                                                                                       | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Source/Drain Doping Techniques for Vertically-Stacked Channel                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Doping scheme                                                                                                                                                                                                                                                                                                                                                            | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5 Carrier Transport Properties of Vertically-Stacked Nanowire                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Device parameters for vertically-stacked silicon nanowire $n$ - and $p$ -MOSFET with sub-50-nm- $L_{eff}$ and 15-nm- $W_{Top}$ . The on-currents $I_{ON}$ are extracted at $V_G$ - $V_T = 0.7$ and -0.7 V for $n$ - and $p$ -MOSFETs, respectively. The off-currents $I_{OFF}$ are extracted at $V_G$ - $V_T = -0.3$ and 0.3 V for $n$ - and $p$ -MOSFETs, respectively. | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                          | Constant-field scaling and generalized scaling of MOSFET device and circuit parameters.  Key device features of Intel 32 nm logic technology [1.28].  Natural length in devices with different geometries [1.32].  Vertically-Stacked Channel MOSFET Fabrication  Nanowire width with various definitions and surface gain factor $W_{eff}/W_{Top}$ .  Process description of anisotropic etching of SiGe/Si superlattice  Source/Drain Doping Techniques for Vertically-Stacked Channel  Doping scheme  Carrier Transport Properties of Vertically-Stacked Nanowire  Device parameters for vertically-stacked silicon nanowire n- and p-MOSFET with sub-50-nm- $L_{eff}$ and 15-nm- $W_{Top}$ . The on-currents $I_{ON}$ are extracted at $V_{G}$ - $V_{T}$ = 0.7 and -0.7 $V_{Top}$ for n- and p-MOSFETs, respectively. The off-currents $I_{OFF}$ are extracted at $V_{G}$ - $V_{T}$ = -0.3 |

# LIST OF FIGURES

| Chapter 1   | <u>Introduction – MOSFET scaling –</u>                                                                                                                                                                                                    |    |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

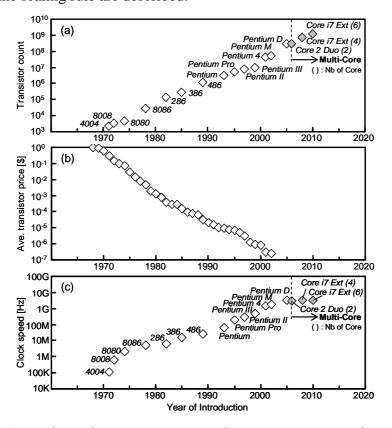

| Figure 1.1  | (a) Number of transistors in Intel's microprocessor chips, (b) Average transistor price by year, (c) Clock speed of Intel's microprocessor [1.2, 1.3].                                                                                    | 3  |

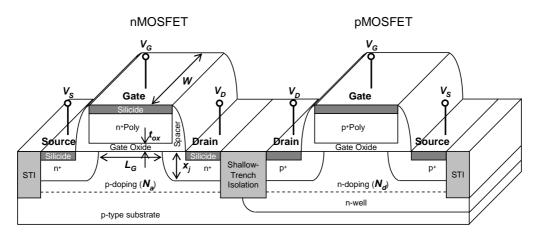

| Figure 1.2  | Three-dimensional view of basic CMOS structure. $V_G$ is gate voltage, $V_S$ is source voltage, $V_D$ is drain voltage, $L_G$ is gate length, $t_{ox}$ is gate oxide thickness, $N_a$ is accepter impurity density,                       |    |

| E: 1.2      | $N_d$ is donor impurity density, $x_j$ is junction depth                                                                                                                                                                                  | 4  |

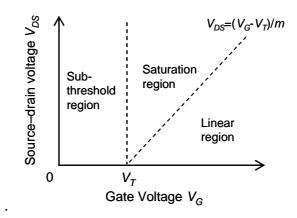

| Figure 1.3  | Three regions of a MOSFET operation in the $V_{DS}$ – $V_G$ plane [1.4].                                                                                                                                                                  | 5  |

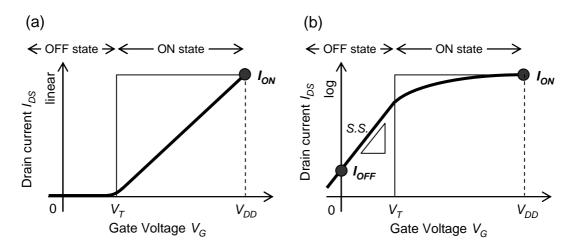

| Figure 1.4  | Typical $I_{DS}$ – $V_G$ characteristics of an nMOSFET at high drain voltages. The same current is plotted on both linear scale (a) and logarithmic scale (b).                                                                            | 6  |

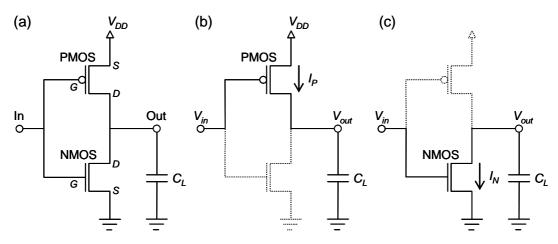

| Figure 1.5  | (a) Circuit diagram of CMOS inverter. (b) Charge and (c) discharge equivalent circuits.                                                                                                                                                   | 8  |

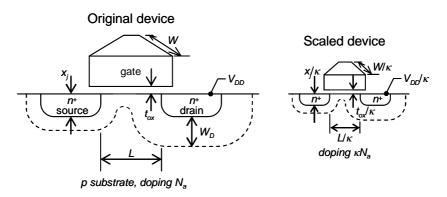

| Figure 1.6  | Principles of MOSFET constant-electric-field scaling.                                                                                                                                                                                     | 9  |

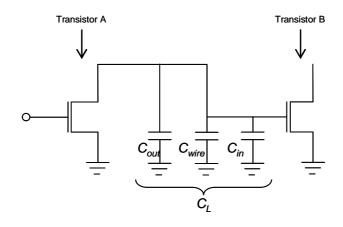

| Figure 1.7  | CV/I performance metric [1.6].                                                                                                                                                                                                            | 12 |

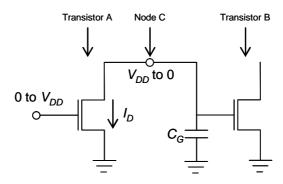

| Figure 1.8  | Equivalent circuit with wiring capacitance.                                                                                                                                                                                               | 13 |

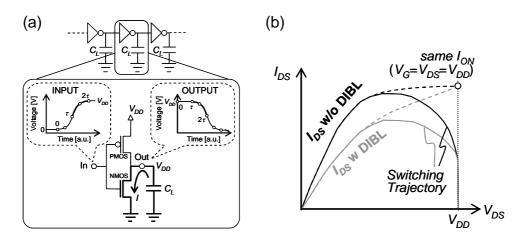

| Figure 1.9  | (a) Operation of a CMOS inverter in inverter chain. (b) $I_{DS}$ - $V_{DS}$ curve and trajectories with and without a degraded DIBL for nMOSFET [1.11].                                                                                   | 14 |

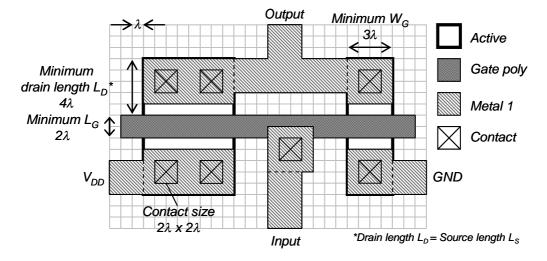

| Figure 1.10 | Layout of a CMOS inverter based on lambda-based design rules [1.15]                                                                                                                                                                       | 15 |

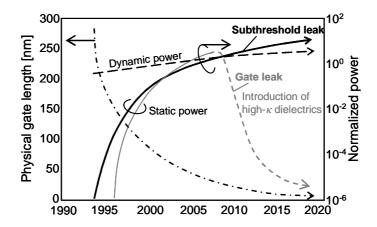

| Figure 1.11 | Sources of leakage current increase as the technology causes gate lengths to shrink. Data from ITRS [1.6]                                                                                                                                 | 17 |

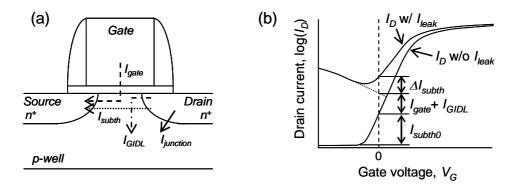

| Figure 1.12 | (a) Leakage current components in a nMOSFET, (b) $I_D$ – $V_G$ curves with and without leakage currents. $I_{subth0}$ is the initial subthreshold current, while $\Delta I_{subth}$ is the added current due to the short-channel effects | 17 |

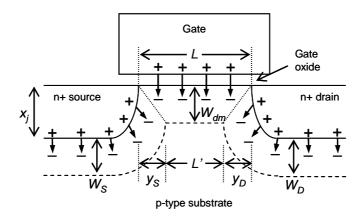

| Figure 1.13        | Schematic diagram of the chare-sharing model. The dashed lines                                                                                 |          |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                    | indicate the boundary of the gate and source–drain depletion regions. The arrows represent electric field lines that originate                 |          |

|                    | from a positive charge and terminate on a negative charge. The                                                                                 |          |

|                    | dotted lines partition the depletion charge and form the two sides                                                                             |          |

|                    | of the trapezoid.                                                                                                                              | 19       |

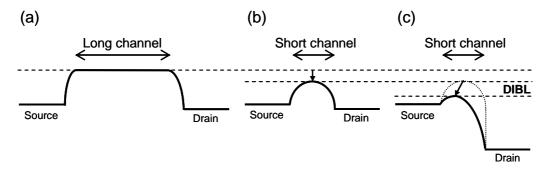

| Figure 1.14        | Surface potential lowering due to the short-channel effects: (a) a                                                                             |          |

| O                  | long-channel MOSFET, (b) a short-channel MOSFET at low                                                                                         |          |

|                    | drain bias, (c) a short-channel MOSFET at high drain bias.                                                                                     | 21       |

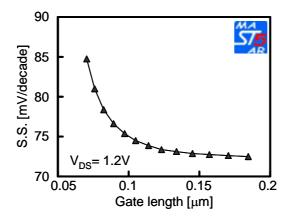

| Figure 1.15        | Subthreshold swing calculated by using MASTAR MOSFET                                                                                           |          |

| C                  | modeling software [1.19]: $N_a=10^{18} \text{cm}^{-3}$ , $x_j=30 \text{ nm}$ , $t_{ox}=1.3 \text{ nm}$ ,                                       |          |

|                    | $V_{DD} = 1.2 \text{ V}, W = 1 \mu m.$                                                                                                         | 21       |

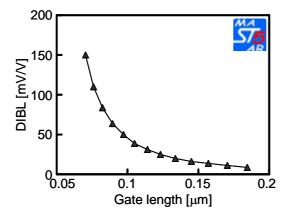

| Figure 1.16        | DIBL calculated by using MASTAR MOSFET modeling software                                                                                       |          |

|                    | [1.19]: $N_a = 10^{18} \text{cm}^{-3}$ , $x_j = 30 \text{ nm}$ , $t_{ox} = 1.3 \text{ nm}$ , $V_{DD} = 1.2 \text{ V}$ , $W = 1 \mu \text{m}$ . | 22       |

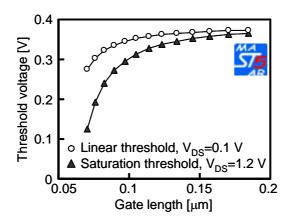

| Figure 1.17        | $V_T$ roll-off calculated by using MASTAR MOSFET modeling                                                                                      |          |

|                    | software [1.19]: $N_a=10^{18} \text{cm}^{-3}$ , $x_j=30 \text{ nm}$ , $t_{ox}=1.3 \text{ nm}$ , $V_{DD}=1.2 \text{ V}$ ,                       |          |

|                    | $W=1\mu m$ .                                                                                                                                   | 23       |

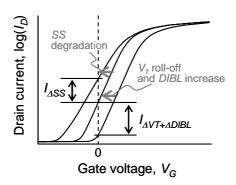

| <i>Figure 1.18</i> | Off-current increase due to the short-channel effects.                                                                                         | 24       |

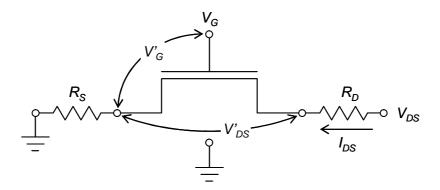

| Figure 1.19        | Equivalent circuit of MOSFET with source and drain resistance                                                                                  |          |

|                    | [1.4].                                                                                                                                         | 24       |

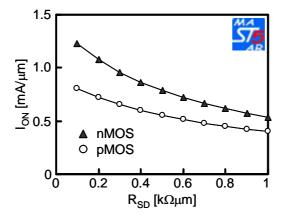

| Figure 1.20        | On-currents as a function of source/drain series resistance. All                                                                               |          |

|                    | plots are calculated by using MASTAR MOSFET modeling                                                                                           |          |

|                    | software [1.19]: $N_a=10^{18} cm^{-3}$ , $t_{ox}=1.3$ nm, $V_{DD}=1.2$ V, $L_G=50$ nm,                                                         |          |

|                    | $W=1\mu m$ .                                                                                                                                   | 25       |

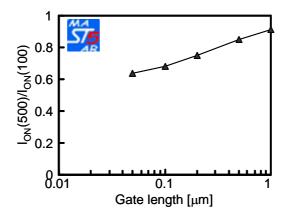

| Figure 1.21        | On-current lowering ratio of $R_{SD}$ = 500 $\Omega$ . $\mu$ m to 100 $\Omega$ . $\mu$ m as a                                                  |          |

|                    | function of gate length. All plots are calculated by using MASTAR                                                                              |          |

|                    | MOSFET modeling software [1.19]: $N_a=10^{18}$ cm <sup>-3</sup> , $t_{ox}=1.3$ nm,                                                             |          |

|                    | $V_{DD}=1.2 \text{ V}, W=1 \mu m.$                                                                                                             | 26       |

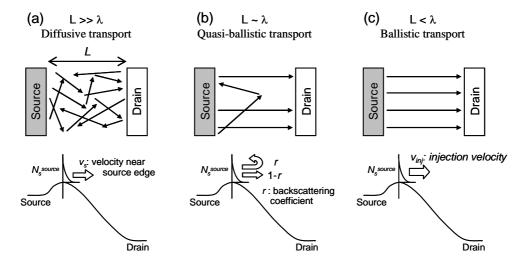

| Figure 1.22        | Schematic diagrams of carrier transport models to determine $I_{ON}$ .                                                                         |          |

|                    | (a) Conventional transport model. (b) Quasi-ballistic transport                                                                                | 27       |

| E: 100             | model. (c) Full-ballistic transport model [1.24, 1.25].                                                                                        | 27       |

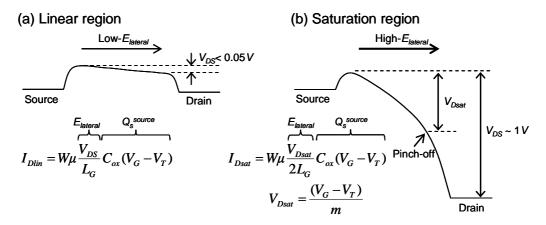

| Figure 1.23        | Channel potential profiles under conditions of carrier mobility $\mu$                                                                          | 27       |

| E: 1 24            | and velocity v. (a) Linear region. (b) Saturation region.                                                                                      | 27       |

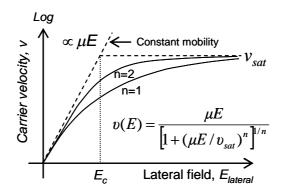

| Figure 1.24        | Velocity–field relationship for electrons $(n=2)$ and holes $(n=1)$ by                                                                         | 20       |

| Figure 1 25        | the empirical form inserted [1.22]. The critical field $E_c = v_{sat}/\mu$ .                                                                   | 28<br>30 |

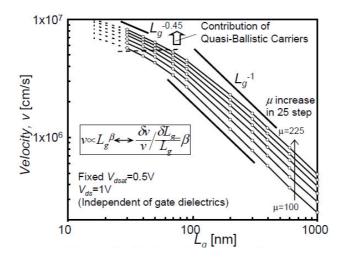

| C                  | $L_G$ dependence of velocity with $\mu$ as parameter [1.27].                                                                                   | 30       |

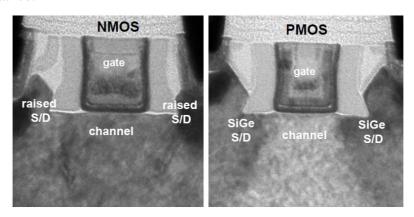

| rigure 1.20        | Cross section of Intel's NMOS and PMOS with 4th generation strained silicon, 2nd generation high-k/metal gate, and raised                      |          |

|                    | S/D regions for 32 nm technology [1.28].                                                                                                       | 31       |

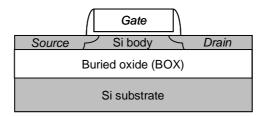

| Figure 1 27        | Cross-section of a planar FDSOI MOSFET.                                                                                                        | 33       |

| 1 15001 0 1.2/     | Cross section of a pianal i Door most Di.                                                                                                      | 55       |

List of figures

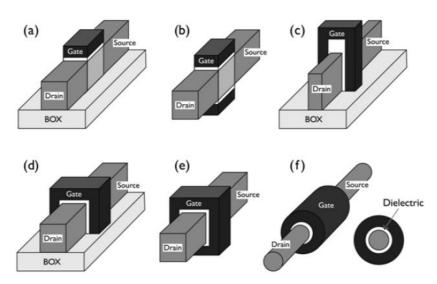

| Figure 1.28      | Various SOI device: (a) Single gate SOI FET, (b) double gate planar SOI FET, (c) double gate non-planar FinFET, (d) tri-gate |    |

|------------------|------------------------------------------------------------------------------------------------------------------------------|----|

|                  | FET, (e) quadruple-gate (or gate-all-around) FET, and                                                                        |    |

|                  | gate-all-around (or surrounding gate) FET (nanowire FET).                                                                    | 33 |

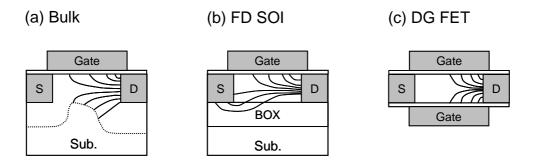

| Figure 1.29      | Illustration of electric field liens from drain of different device types: (a) bulk, (b) FD SOI, and (c) double gate (DG).   | 34 |

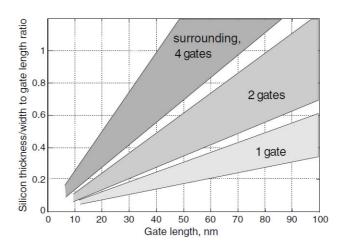

| Figure 130       | Maximum allowed Si thickness and device width vs. gate length to                                                             | 31 |

| 1 igure 1.50     | avoid short-channel effects in single-, double- and                                                                          |    |

|                  | quadruple-gate SOI MOSFETs [1.35].                                                                                           | 35 |

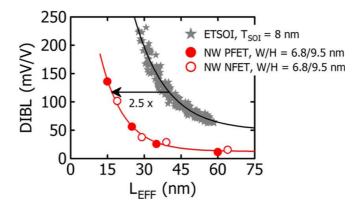

| Figure 1.31      | Comparison of DIBL of elliptical GAA SNWTs (width $W = 6.8 \text{ nm}$                                                       |    |

|                  | and height $H = 9.5$ nm) and single-gate ETSOI FETs (SOI                                                                     |    |

|                  | thickness $t_{si} = 8$ nm) with similar body dimensions. [1.36].                                                             | 35 |

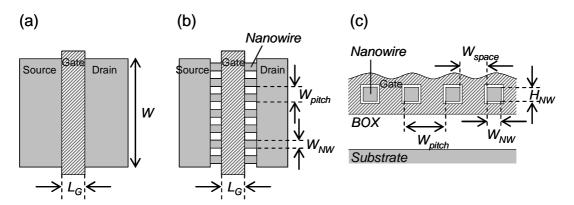

| Figure 1.32      | MOSFET layout; (a) planar MOSFET, (b) GAA SNWT with                                                                          |    |

| O                | multi-finger, and (c) cross-section of GAA SNWT.                                                                             | 36 |

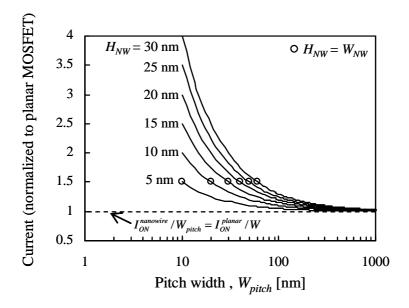

| Figure 1.33      | Normalized current of a rectangular GAA SNWT as a function of                                                                |    |

| - 18             | multi-finger pitch width. $W_{NW}=W_{pitch}/2$ . The top interface mobility                                                  |    |

|                  | is $300 \text{ cm}^2/\text{V}$ s and sidewall mobility is $150 \text{ cm}^2/\text{V}$ s.                                     | 37 |

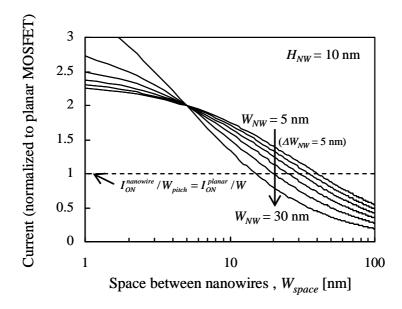

| Figure 1 34      | Normalized current of a rectangular GAA SNWT as a function of                                                                | 57 |

| 1 1841 € 1.51    | space between nanowires. $H_{NW}=10$ nm. The top interface mobility                                                          |    |

|                  | is $300 \text{ cm}^2/\text{V}s$ and sidewall mobility is $150 \text{ cm}^2/\text{V}s$ .                                      | 38 |

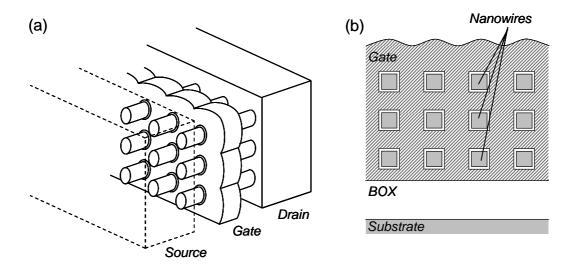

| Figure 1 35      | ·                                                                                                                            | 30 |

| rigure 1.55      | Structure of vertically-stacked GAA SNWT(a) and its cross-section (b)                                                        | 39 |

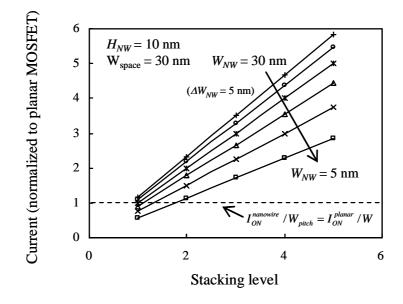

| Figure 1.36      | Normalized current of a rectangular GAA SNWT as a function of                                                                |    |

|                  | staking level of nanowires. $H_{NW}=10$ nm. $W_{space}=30$ nm. The top                                                       |    |

|                  | interface mobility is $300 \text{ cm}^2/\text{Vs}$ and sidewall mobility is $150 \text{ cm}^2/\text{Vs}$ .                   | 39 |

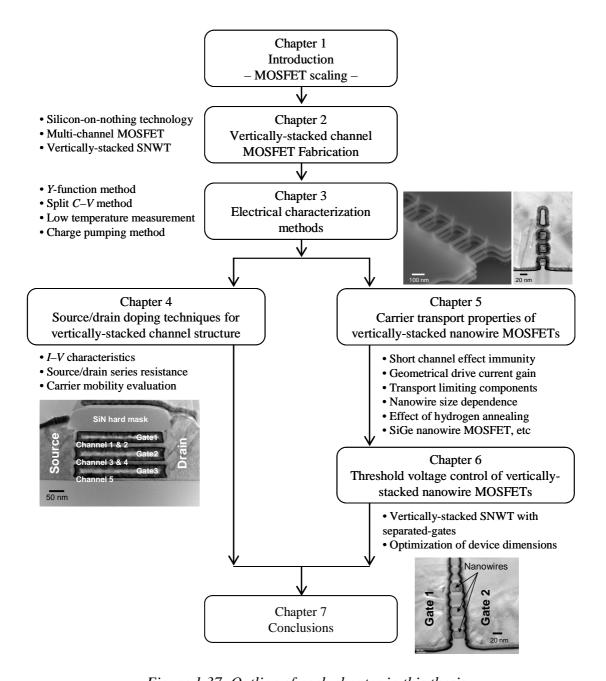

| Figure 1.37      | Outline of each chapter in this thesis.                                                                                      | 40 |

|                  |                                                                                                                              |    |

| <u>Chapter 2</u> | Vertically-Stacked Channel MOSFET Fabrication                                                                                |    |

| Figure 2.1       | Fabrication process of the SON MOSFET: (a) epitaxy of SiGe                                                                   |    |

|                  | and Si layers on isolated bulk wafer; (b) conventional CMOS                                                                  |    |

|                  | process steps until formation of the nitride spacers; (c) formation                                                          |    |

|                  | of the shallow trenches in the S/D regions and formation of the                                                              |    |

|                  | tunnel under the Si film; (d) filling the tunnel with oxide (optional                                                        |    |

|                  | step); (e) selective epitaxy of S/D regions, implantation and RTA.                                                           | 51 |

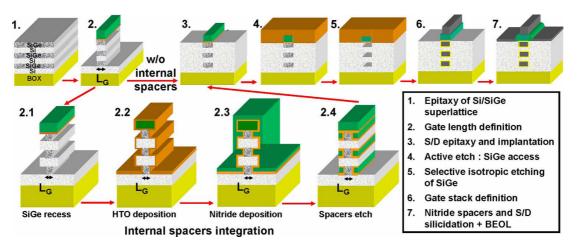

| Figure 2.2       | MCFET fabrication process overview [2.2].                                                                                    | 53 |

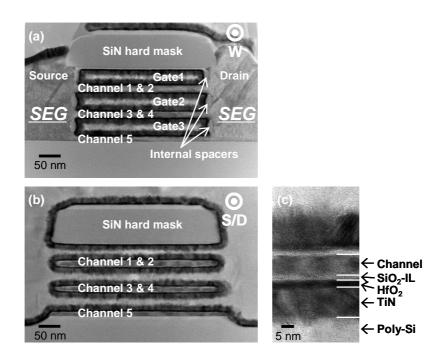

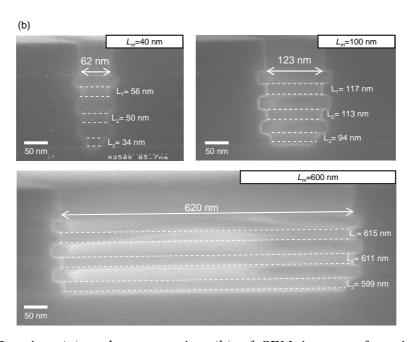

| Figure 2.3       | Fabricated multi channel FET (MCFET) along (a) channel length                                                                |    |

| - 101110 210     | and (b) width direction. (c) is the enlarged image of the gate                                                               |    |

|                  | stack.                                                                                                                       | 54 |

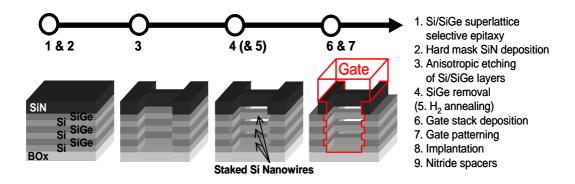

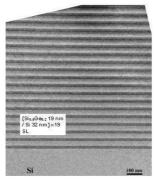

| Figure 2.4       | Vertically-stacked nanowire MOSFET fabrication process                                                                       |    |

|                  | overview [2.5].                                                                                                              | 55 |

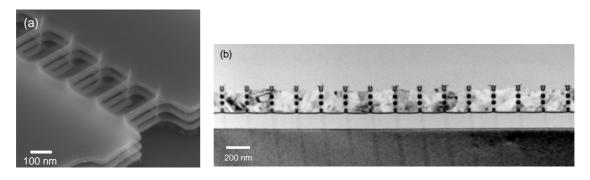

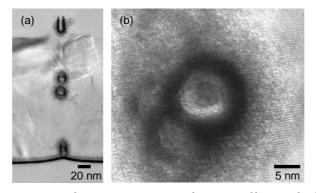

| Figure 2.5          | Fabricated vertically-stacked silicon nanowires: (a) a top-view SEM image, (b) a cross-section TEM image.                                                                                                                                                                                                                   | 55         |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

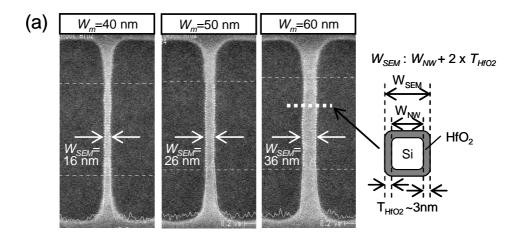

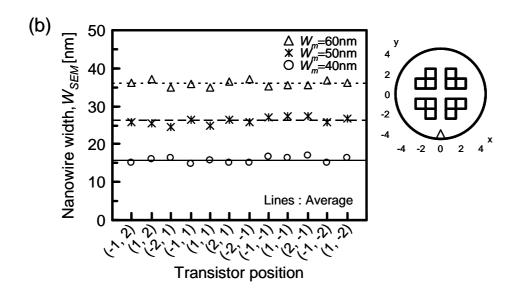

| Figure 2.6          | (a) Top-view SEM images of silicon nanowires after $HfO_2$ deposition with width $W_{SEM}$ = 16, 26, and 36 nm. (b) Variation of nanowire width in a 200-nm-wafer. The variations are less than +/- 1.5 nm. The thickness of $HfO_2$ on side walls (3nm x 2) is included in the values of $W_{SEM}$ . Wm is the mask width. | 56         |

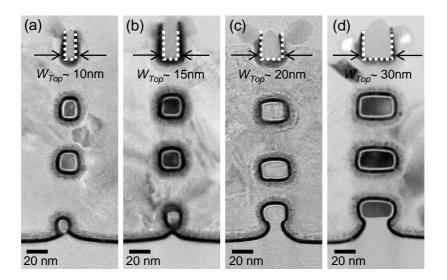

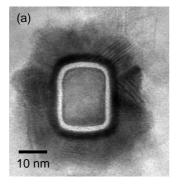

| Figure 2.7          | Cross-sectional TEM images of vertically-stacked silicon nanowire MOSFET with top-view width $W_{Top}$ = 10, 15, 20 and 30 nm.                                                                                                                                                                                              | 57         |

| Figure 2.8          | (a) Cross-sectional TEM image of vertically-stacked silicon nanowire MOSFET with top-view width $W_{Top}$ = 5 nm. (b) Enlarged image of 5-nm-diameter nanowire.                                                                                                                                                             | 57         |

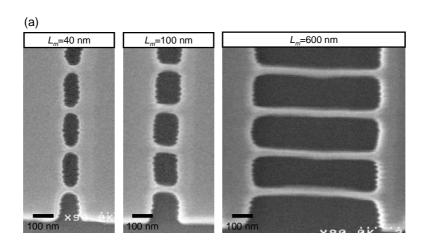

| Figure 2.9          | Top-view (a) and cross-section (b) of SEM images of vertically-stacked silicon nanowire MOSFET with mask length $L_m = 40, 100, \text{ and } 600 \text{ nm}.$                                                                                                                                                               | 58         |

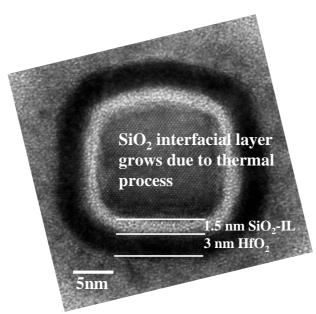

| Figure 2.10         | Cross-sectional TEM image of vertically-stacked silicon nanowire with high-κ/metal gate.                                                                                                                                                                                                                                    | 60         |

| Chapter 3           | Electrical Charactarization Methods                                                                                                                                                                                                                                                                                         |            |

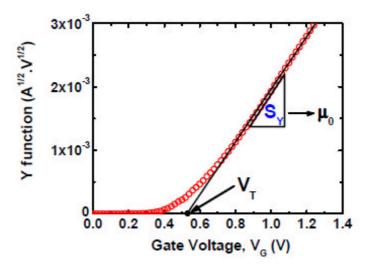

| Figure 3.1          | <i>Y- function as a function of the gate voltage.</i>                                                                                                                                                                                                                                                                       | 67         |

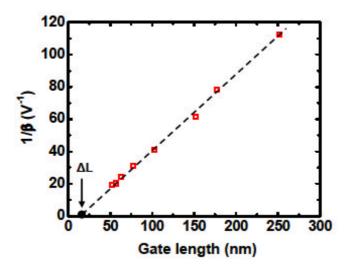

| Figure 3.2          | Extraction of the effective gate length.                                                                                                                                                                                                                                                                                    | 67         |

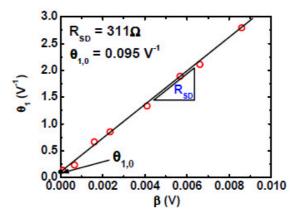

| Figure 3.3          | Extraction of the series resistances for 40nm to 600nm gate lengths MCFET devices ( $W = 500$ nm).                                                                                                                                                                                                                          | 68         |

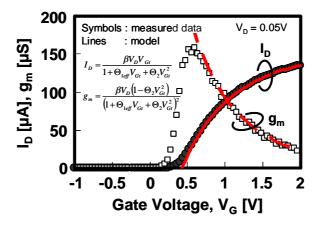

| Figure 3.4          | Measured and modeled $I_{Dlin}$ - $V_G$ and $g_{mlin}$ - $V_G$ characteristics of $TiN/HfO_2$ n-MCFETs. Gate length and width are 70 nm and 350 nm, respectively.                                                                                                                                                           | 69         |

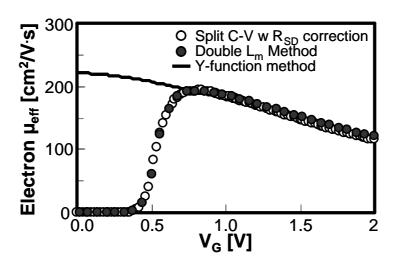

| Figure 3.5          | Comparison of effective mobility extracted by split C-V, double $L_m$ method, and from parameters extracted by Y-function method. The measured device is the stacked SNWTs with $W_{NW}$ =15 nm and $L_{eff}$ =242 nm. The device with $L_{eff}$ =592 nm was also used for                                                  |            |

|                     | double $L_m$ method.                                                                                                                                                                                                                                                                                                        | 71         |

| Chapter 4 Structure | Source/Drain Doping Techniques for Vertically-Stacked Channel                                                                                                                                                                                                                                                               |            |

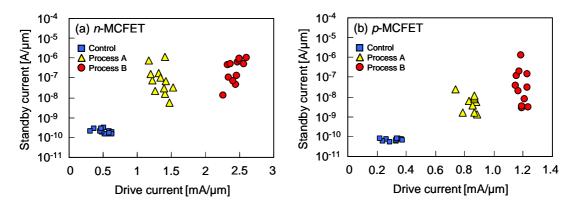

| Figure 4.1          | On-off relations of (a) n- and (b) p-MCFETs.                                                                                                                                                                                                                                                                                | 77         |

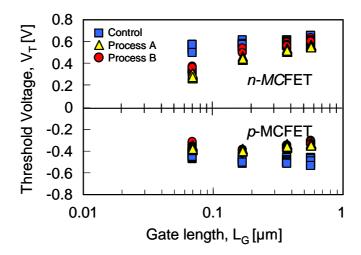

| Figure 4.2          | $V_T$ roll-off characteristics of MCFETs with $L_G$ scaling.                                                                                                                                                                                                                                                                | <i>7</i> 8 |

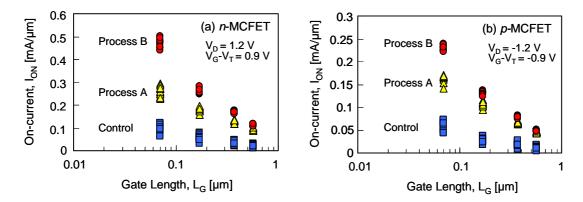

| Figure 4.3     | On-current dependency on the gate length for (a) n- and (b) p-MCFETs.                                                                                                                                                                                                                         | 7 |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

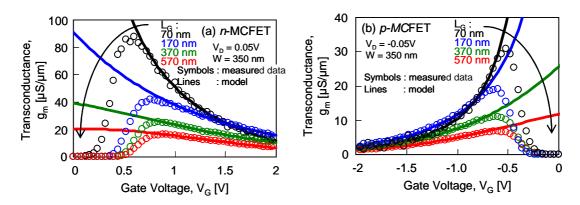

| Figure 4.4     | Transconductance of the (a) n- and (b) p-MCFETs. Solid lines represent the fitted model.                                                                                                                                                                                                      | 7 |

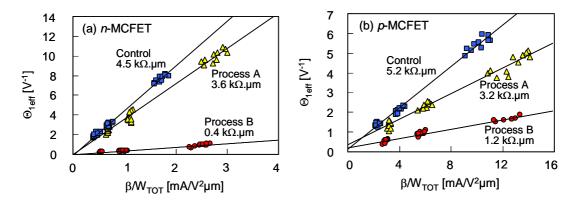

| Figure 4.5     | $\Theta_{leff}$ vs. $\beta$ curves of the fabricated (a) n- and (b) p-MCFETs.                                                                                                                                                                                                                 | 7 |

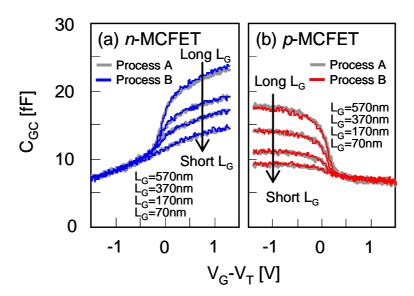

| Figure 4.6     | $C_{GC}$ characteristics with various $L_G$ for (a) $n$ - and (b) $p$ -MCFETs.                                                                                                                                                                                                                | 8 |

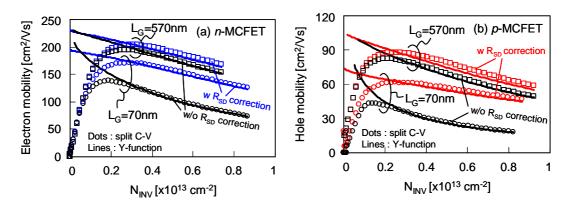

| Figure 4.7     | $\mu_{\rm eff}$ of the MCFETS with different $L_G$ of 570 and 70 nm.                                                                                                                                                                                                                          | 8 |

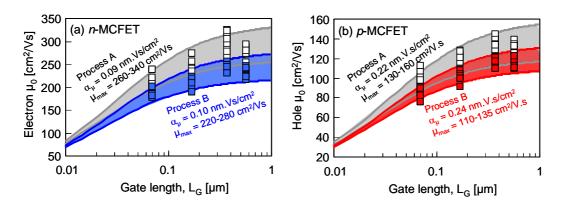

| Figure 4.8     | Estimated $\mu_0$ on $L_G$ scaling.                                                                                                                                                                                                                                                           | 8 |

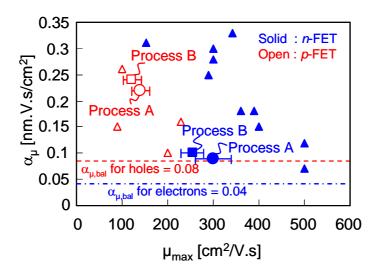

| Figure 4.9     | Summary of the extracted $\alpha_{\mu}$ and $\mu_{max}$ .                                                                                                                                                                                                                                     | 8 |

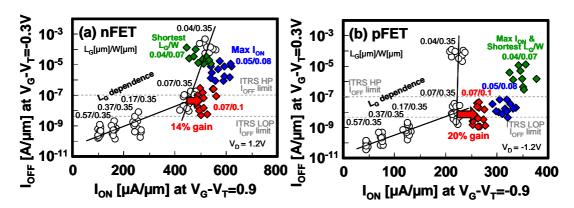

| Figure 4.10    | $I_{ON}$ - $I_{OFF}$ characteristics with several channel sizes for nMCFET (a) and pFET (b).                                                                                                                                                                                                  | 8 |

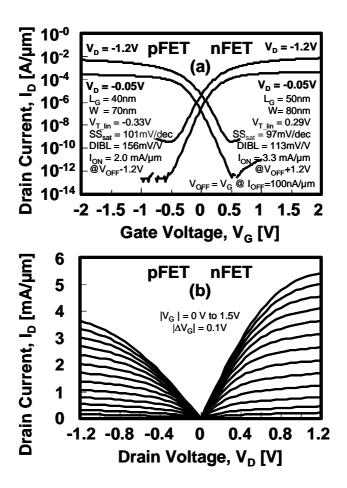

| Figure 4.11    | $I_D$ - $V_G$ (a) and $I_D$ - $V_D$ (b) characteristics for the scaled MCFETs.                                                                                                                                                                                                                | 8 |

| Chapter 5      | Carrier Transport Properties of Vertically-Stacked Nanowire                                                                                                                                                                                                                                   |   |

| <u>MOSFETs</u> | Current 1. unaport 1. toporties of fortient, statement 1. unioniste                                                                                                                                                                                                                           |   |

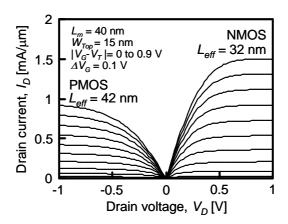

| Figure 5.1     | $I_D$ - $V_D$ characteristics of vertically-stacked silicon nanowire $n$ - and $p$ - $MOSFET$ with sub-50- $nm$ - $L_{eff}$ and 15- $nm$ - $W_{Top}$ .                                                                                                                                        | ç |

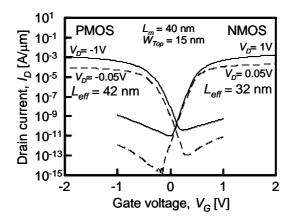

| Figure 5.2     | $I_D$ - $V_G$ characteristics of vertically-stacked silicon nanowire $n$ - and $p$ - $MOSFET$ with sub-50-nm- $L_{eff}$ and 15-nm- $W_{Top}$ .                                                                                                                                                | g |

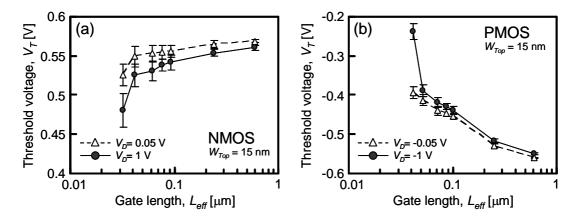

| Figure 5.3     | Threshold voltage as a function of effective gate length for vertically- stacked silicon nanowire $n$ - and $p$ -MOSFET with $15$ -nm- $W_{Top}$ .                                                                                                                                            | ç |

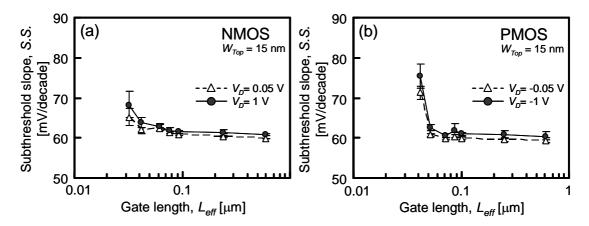

| Figure 5.4     | Subthreshold slope as a function of effective gate length for vertically- stacked silicon nanowire n- and p-MOSFET with 15-nm-W <sub>Top</sub> .                                                                                                                                              | g |

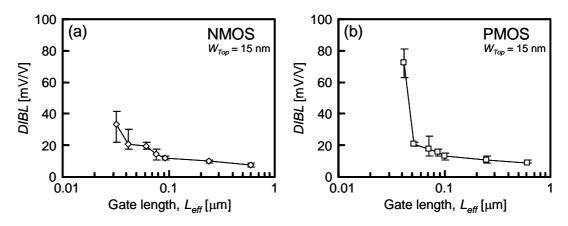

| Figure 5.5     | Drain-induced barrier lowering (DIBL) as a function of effective gate length for vertically-stacked silicon nanowire n- and p-MOSFET with 15-nm-W <sub>Top</sub> .                                                                                                                            | Ģ |

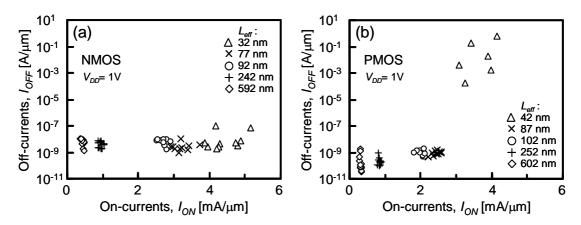

| Figure 5.6     | $I_{ON}$ - $I_{OFF}$ characteristics of vertically-stacked silicon nanowire $n$ - and $p$ - $MOSFET$ with 15- $nm$ - $W_{Top}$ .                                                                                                                                                              | g |

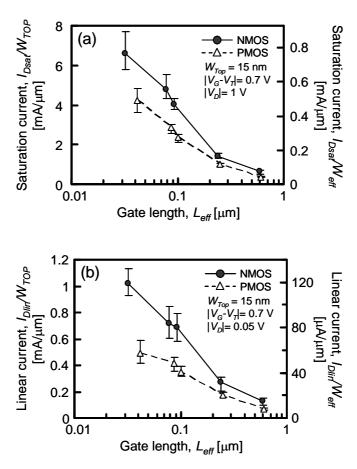

| Figure 5.7     | Saturation current density (a) and linear current density (b) as a function of effective gate length for vertically-stacked silicon nanowire n- and p-MOSFET with 15-nm-WTop. The currents are normalized by top-view width WTop (left y-axis) and effective total width Weff (right y-axis). | 9 |

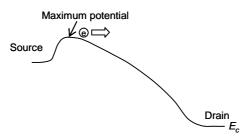

| Figure 5.8     | Schematic image of conduction band                                                                                                                                                                                                                                                            | 9 |

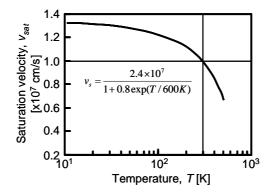

| Figure 5.9     | Temperature dependence of saturated electron drift velocity [5.2].                                                                                                                                                                                                                            | 9 |

| Figure 5.10    | Injection velocity of a NMOSFET on (100) plane as a function of                                                                                                                                                                                                                               | , |

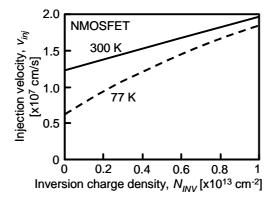

| 1 181110 3.10  | inversion charge density at 300 and 77 K. [5.3].                                                                                                                                                                                                                                              | Ç |

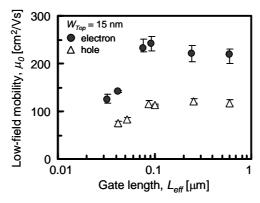

| Figure 5.11 | Low-field mobility $\mu_0$ as a function of effective gate length for vertically-stacked silicon nanowire $n$ - and $p$ -MOSFET with 15- $nm$ - $W_{Top}$ .                                                                                                                         | 96  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

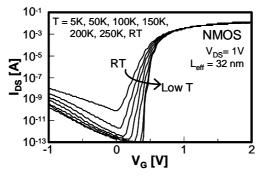

| Figure 5.12 | Temperature dependence of $I_D$ - $V_G$ characteristics for vertically-stacked SNWTs.                                                                                                                                                                                               | 96  |

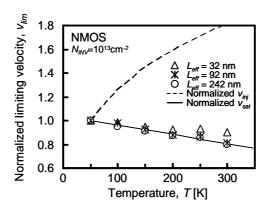

| Figure 5.13 | Temperature dependence of extracted limiting velocity $v_{lim}$ . Theoretical dependence of saturation velocity $v_{sat}$ from [5.5] and injection velocity $v_{ini}$ from [5.6] are given.                                                                                         | 97  |

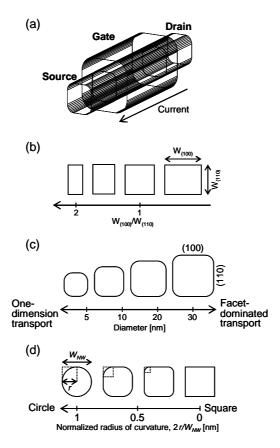

| Figure 5.14 | Schematic image of nanowire MOSFET (a) and its cross-section: (b) varying ratio of (100) width to (110) width, (c) varying size, (d) varying radius of curvature at the corners.                                                                                                    | 98  |

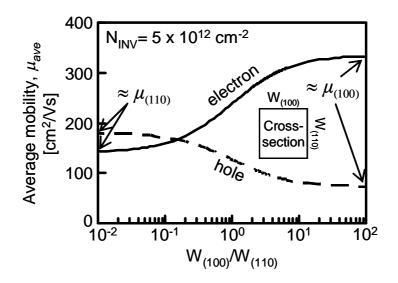

| Figure 5.15 | Nanowire mobility as a function of $W_{(100)}$ -to- $W_{(110)}$ ratio. The average mobility is mave= $(\mu_{(100)}W_{(100)} + \mu_{(100)})$ $W_{(100)}/(W_{(100)}+W_{(110)})$ , where $\mu_{(100)}$ and $\mu_{(110)}$ are the mobilities on (100) and (110) surfaces, respectively. | 98  |

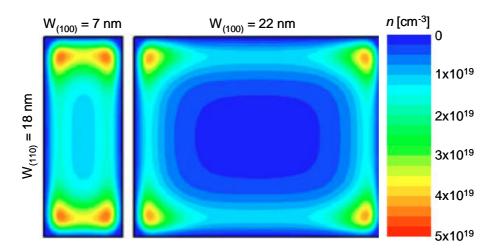

| Figure 5.16 | Calculated profiles of electron density across the cross section of silicon nanowires with $W_{(110)}=18$ nm, and $W_{(100)}=7$ and 22 nm [5.7].                                                                                                                                    | 99  |

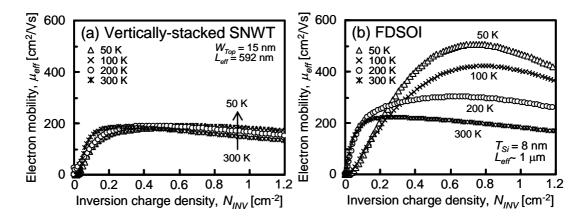

| Figure 5.17 | Temperature dependence of effective electron mobility in vertically-stacked silicon nanowire FET (a) and in fully-depleted SOI-FET (b).                                                                                                                                             | 100 |

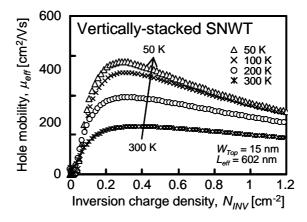

| Figure 5.18 | Temperature dependence of effective hole mobility in vertically-stacked silicon nanowire FET.                                                                                                                                                                                       | 100 |

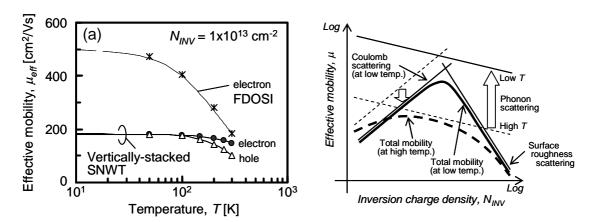

| Figure 5.19 | (a) Temperature dependence of effective mobility at high inversion charge density ( $N_{INV}=10^{13} cm^{-2}$ ). (b) Schematic diagram of mobility limiting components at low temperature.                                                                                          | 101 |

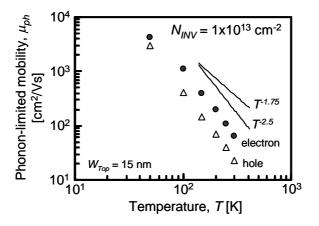

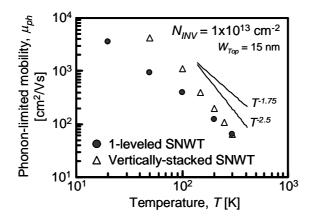

| Figure 5.20 | Temperature dependence of phonon-limited mobility at high inversion charge density ( $N_{INV}=10^{13}$ cm <sup>-2</sup> ) for vertically-stacked silicon nanowire MOSFETs.                                                                                                          | 101 |

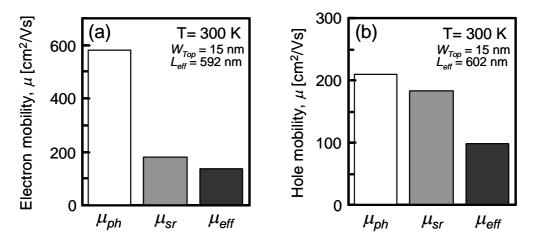

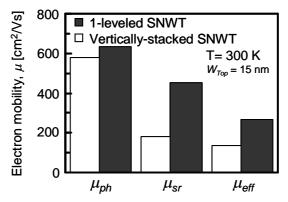

| Figure 5.21 | Mobility limiting components for electron (a) and hole for vertically- stacked silicon nanowire MOSFETs at 300 K.                                                                                                                                                                   | 101 |

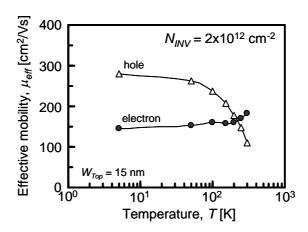

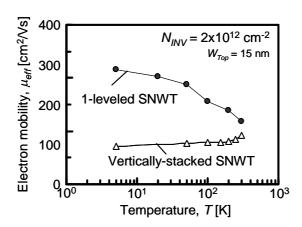

| Figure 5.22 | Temperature dependence of effective mobility at low inversion charge density $(N_{INV}=2x10^{12} \text{ cm}^{-2})$ .                                                                                                                                                                | 102 |

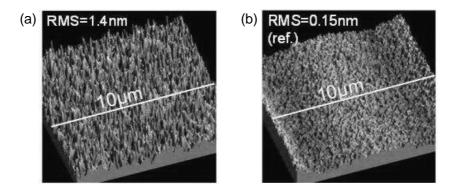

| Figure 5.23 | Atomic force microscopy images of silicon surface after isotropic SiGe dry etching (a) and the reference sample without the etching (b).                                                                                                                                            | 102 |

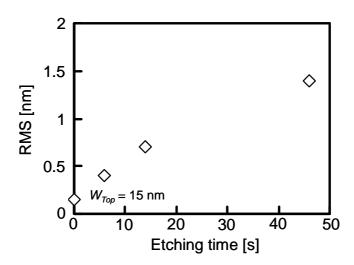

| Figure 5.24 | Root mean square (RMS) values as a function of isotropic SiGe dry etching.                                                                                                                                                                                                          | 103 |

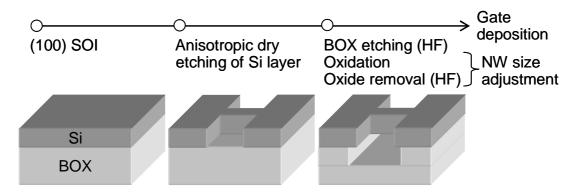

| Figure 5.25 | Brief process flow of 1-level silicon nanowire MOSFET.                                                                                                                                                                                                                              |     |

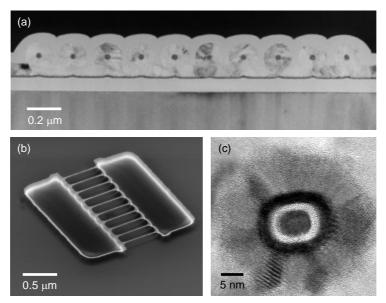

| Figure 5.26 | Gate-all-around 1-level silicon nanowire MOSFETs fabricated without SiGe epitaxy and selective etching.                                                                                                                                                                             | 103 |

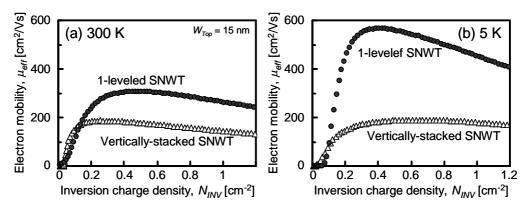

| Figure 5.27 |                                                                                                                                                                                                                                                                                     | 104 |

List of figures

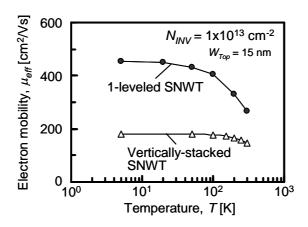

| Figure 5.28 | Temperature dependence of effective mobility at high inversion charge density ( $N_{INV}=10^{13}$ cm <sup>-2</sup> ) for 1-leveled and vertically-stacked silicon nanowire MOSFET.                                                                                                                                                                                                                                                                                                                                                                       | 105 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.29 | Temperature dependence of phonon-limited mobility at high inversion charge density ( $N_{INV}$ = $10^{13}$ cm <sup>-2</sup> ) for 1-leveled and vertically-stacked silicon nanowire MOSFETs.                                                                                                                                                                                                                                                                                                                                                             | 103 |

| Figure 5.30 | Mobility limiting components comparison at high inversion charge density between 1-leveled and vertically-stacked silicon nanowire MOSFETs at 300 K.                                                                                                                                                                                                                                                                                                                                                                                                     | 105 |

| Figure 5.31 | Temperature dependence of effective mobility at low inversion charge density $(N_{INV}=2x10^{12} \text{ cm}^{-2})$ .                                                                                                                                                                                                                                                                                                                                                                                                                                     | 106 |

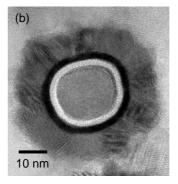

| Figure 5.32 | Cross-sectional TEM images of silicon nanowire (a) without and (b) with hydrogen annealing at 750 °C for two minutes.                                                                                                                                                                                                                                                                                                                                                                                                                                    | 106 |

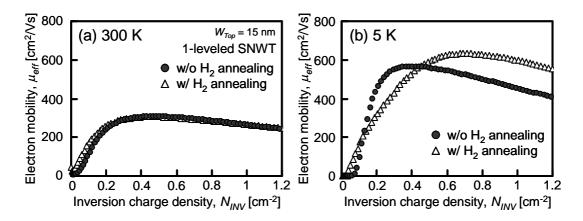

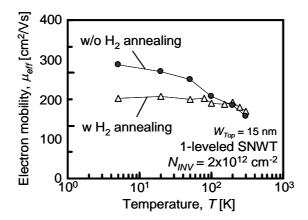

| Figure 5.33 | Electron mobility comparison of 1-leveled silicon nanowire MOSFETs between with and without hydrogen annealing. The measurement temperatures are $300 \text{ K}$ (a) and $5 \text{ K}$ (b).                                                                                                                                                                                                                                                                                                                                                              | 107 |

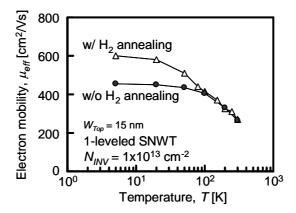

| Figure 5.34 | Temperature dependence of effective mobility at high inversion charge density $(N_{INV}=10^{13} \text{cm}^{-2})$ for 1-leveled nanowire MOSFET with and without $H_2$ anneal.                                                                                                                                                                                                                                                                                                                                                                            | 107 |

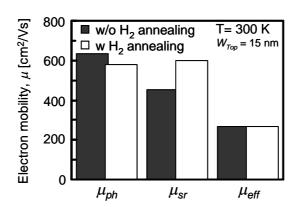

| Figure 5.35 | Mobility limiting components comparison at high inversion charge density and 300 K for 1-leveled silicon nanowire MOSFET between with and without hydrogen annealing.                                                                                                                                                                                                                                                                                                                                                                                    | 108 |

| Figure 5.36 | Temperature dependence of effective mobility at low inversion charge density $(N_{INV}=2x10^{12} \text{ cm}^{-2})$ .                                                                                                                                                                                                                                                                                                                                                                                                                                     | 108 |

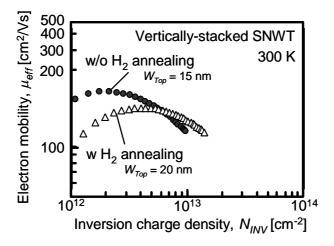

| Figure 5.37 | Electron mobility comparison of vertically-stacked silicon nanowire MOSFETs between with and without hydrogen annealing.                                                                                                                                                                                                                                                                                                                                                                                                                                 | 108 |

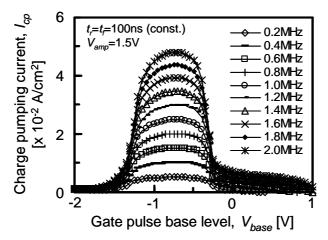

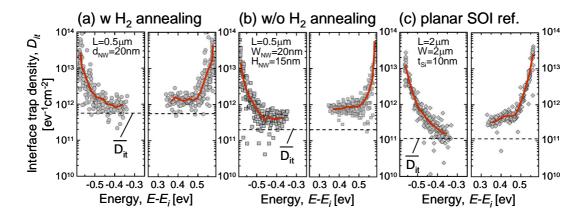

| Figure 5.38 | Charge pumping currents $I_{cp}$ obtained base voltage sweep on nanowire gated-diode with $L_G = 240$ nm and $W_{NW}/H_{NW} = 20$ nm/15 nm. The currents are normalized by $W_{eff}$ obtained from TEM images.                                                                                                                                                                                                                                                                                                                                           | 109 |

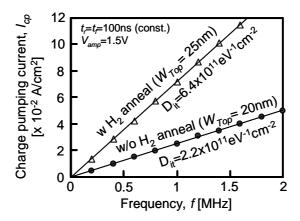

| Figure 5.39 | Charge pumping currents $I_{cp}$ as a function of frequency $f$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 109 |

| Figure 5.40 | Interface trap density as a function of energy for vertically-stacked nanowires with (a) and without (b) hydrogen annealing, and planar SOI devices (c) with the same gate stack (3 nm HfO <sub>2</sub> ALD/10 nm TiN CVD). The profile is obtained by scanning temperature from 300 K down to 25 K by 25 K steps. The bold line represents the mean value of $D_{it}(E)$ . The dashed line is the directly measured mean value of interface trap density over the full energy range at 300 K which evidence the lower density of interface traps in the | 109 |

|             | middle of the gap.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 110 |

List of figures

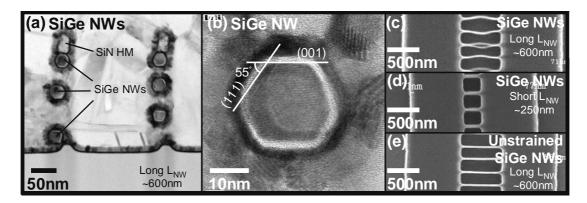

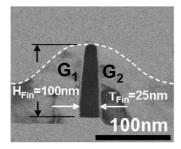

| Figure 5.41       | (a) Cross-sectional TEM micrographs of 3D- stacked compressively(c)- strained SiGe NWTs, (b) enlarged images of c-strained SiGe NW, (c) top view of bended c-strained SiGe NWs with $L_{NW}$ =600nm, (d) top view of c-strained SiGe NWs with $L_{NW}$ =250nm, and (e) top view of un-strained SiGe NWs with $L_{NW}$ =600nm. Short length SiGe NWs are straight, this whatever their strain state. |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

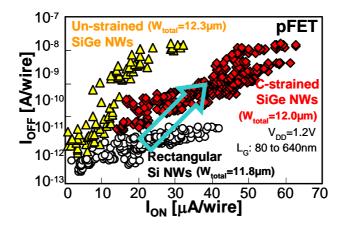

| Figure 5.42       | $I_{ON}/I_{OFF}$ characteristics of Si, c-strained and un-strained SiGe NWs normalized by the number of wires. The total NW surface $W_{total}$ is estimated from the cross-sectional TEM images. The $W_{NW}$ of all NWs is ~20nm.                                                                                                                                                                 |

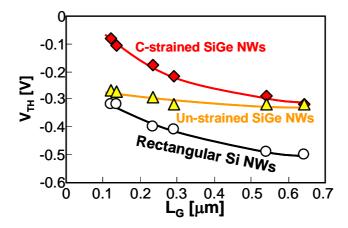

| Figure 5.43       | Threshold voltage of Si, c-strained and un-strained SiGe NWs as a function of gate length. The $W_{NW}$ of all NWs are ~20nm.                                                                                                                                                                                                                                                                       |

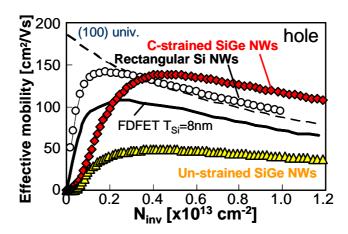

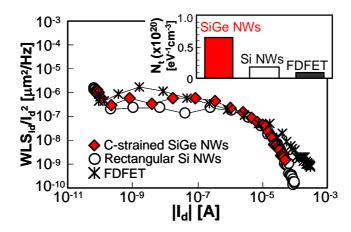

| Figure 5.44       | Effective hole mobility of Si, c-strained and un-strained SiGe NWs. The $W_{NW}$ of all NWs are ~20nm.                                                                                                                                                                                                                                                                                              |

| Figure 5.45       | Low-frequency noise of Si and c-strained SiGe NWs. Inserted figure is a comparison of oxide trap density $(N_t)$ . $L_G$ and $W_{NW}$ are ~290nm and ~20nm, respectively.                                                                                                                                                                                                                           |

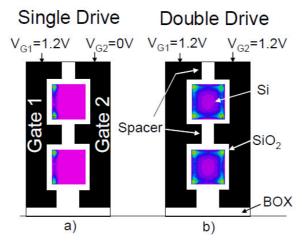

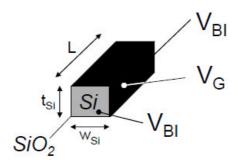

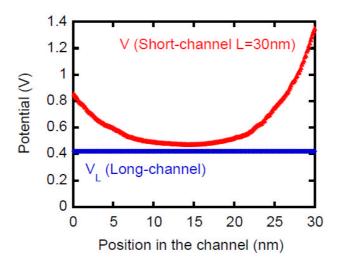

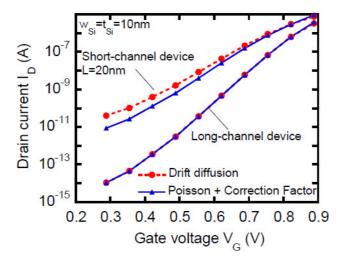

| Chapter 6 MOSFETs | Threshold Voltage Control of Vertically-Stacked Nanowire                                                                                                                                                                                                                                                                                                                                            |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 6.1        | Cross-sectional TEM image of the independent-gate FinFET fabricated by the resist etch back process [6.4].                                                                                                                                                                                                                                                                                          |

| Figure 6.2        | $\Phi$ -FET scheme.                                                                                                                                                                                                                                                                                                                                                                                 |

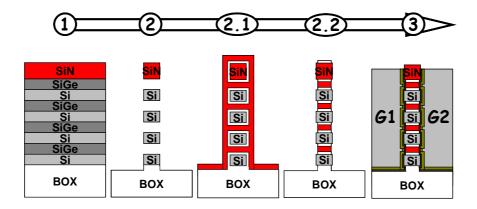

| Figure 6.3        | Schematic fabrication sequence of $\Phi$ -FET.                                                                                                                                                                                                                                                                                                                                                      |

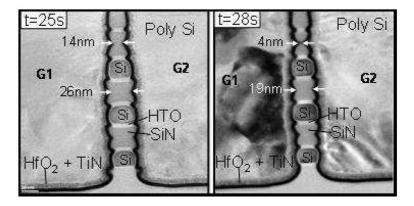

| Figure 6.4        | Cross-sectional TEM pictures of $\Phi$ -FET (3 stacked nanowires).<br>Left: 25s SiN isotropic etching Right: 28s SiN isotropic etching.                                                                                                                                                                                                                                                             |

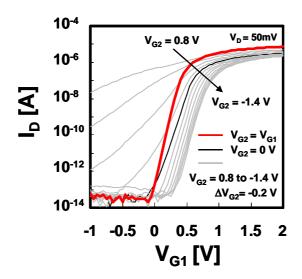

| Figure 6.5        | Experimental $I_d$ - $V_{g1}$ characteristics at various $V_{g2}$ for n-channel $\Phi$ -FET. The gate length and channel width are 550 nm and 25 nm, respectively.                                                                                                                                                                                                                                  |