# Electric properties of CeO<sub>X</sub> /La<sub>2</sub>O<sub>3</sub> stack as gate dielectric in advanced MOSFET technology

M. Kouda<sup>1</sup>, K. Tachi<sup>1</sup>, K. Kakushima<sup>2</sup>, P. Ahmet<sup>1</sup>, K. Tsutsui<sup>2</sup>, N. Sugii<sup>2</sup>, A. N. Chandorkar<sup>1,3</sup>, T. Hattori<sup>1</sup> and H. Iwai<sup>1</sup> FRC<sup>1</sup>, IGSSE<sup>2</sup> Tokyo Institute of Technology 4259-S2-20, Nagatsuta-cho, Midori-ku, Yokohama 226-8503, Japan IIT Bombay<sup>3</sup> Powai, Mumbai-400076, India E-mail: <u>m.kouda@iwailab.ep.titech.ac.jp</u>

### Abstract

The dielectric properties of  $CeO_x/La_2O_3$  gate stack was investigated. The leakage current at the EOT around 1.0 nm was suppressed by one order compare to the leakage current in  $La_2O_3$  by introducing  $CeO_x/La_2O_3$  stack. MOSFETs with  $CeO_x/La_2O_3$  stack as the gate dielectric

were fabricated and its properties were studied.

#### Introduction

CeO<sub>x</sub> has a high dielectric constant of ~ 26 [1], but is has a relatively narrow band gap of 3eV. On the other hand, La<sub>2</sub>O<sub>3</sub> has a large band gap of ~5.4eV, however, EOT increases due to growth of silicate [2] at the interface of La<sub>2</sub>O<sub>3</sub>/Si during the thermal process. It was reported that the interfacial layer growth at the La<sub>2</sub>O<sub>3</sub>/Si interface strongly depend on the supplied oxygen to the La<sub>2</sub>O<sub>3</sub> film[3] and CeO<sub>x</sub> has a excellent oxygen storage properties thanks to the chemical properties Ce ion. Therefore, it is expected that a CeO<sub>x</sub> / La<sub>2</sub>O<sub>3</sub> stacked structure may improve the dielectric properties of La<sub>2</sub>O<sub>3</sub>. In this paper, we report the dielectric properties of CeO<sub>x</sub> / La<sub>2</sub>O<sub>3</sub> gate stack.

#### Experiments

MOS capacitors and MOSFET were fabricated on a ntype Si(100) wafers (resistivity 1~10  $\Omega$ cm). After chemical cleaning with H<sub>2</sub>SO<sub>4</sub>+H<sub>2</sub>O<sub>2</sub> followed by HF dipping, the stacked structures consisting of La<sub>2</sub>O<sub>3</sub> and CeO<sub>x</sub> films were deposited by electron-beam deposition in ultrahigh vacuum (10<sup>-6</sup> Pa) at 300 °C. Thicknesses of the materials were controlled by moving a mechanical shutter during the deposition. Single-layer capacitors of La<sub>2</sub>O<sub>3</sub> and CeO<sub>x</sub> were fabricated as references. Tungsten (W) metal gate electrode was *in-situ* deposited by RF sputtering in order to avoid any moisture or carbonrelated contamination. Post-metallization annealing (PMA) was conducted in forming gas (H<sub>2</sub>:3%, N<sub>2</sub>:97%) at 500 °C for 30 min.

EOT values were derived by fitting capacitance-voltage (C-V) curves using the CVC program. Gate current density-voltage (J-V) properties were measured at the temperatures of 20 to  $120^{\circ}$ C

## **Results and Discussions**

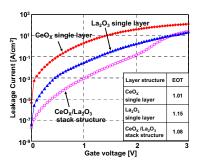

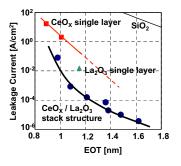

Figure 1 shows the J-V characteristics of the fabricated capacitors with CeO<sub>X</sub> single layer, La<sub>2</sub>O<sub>3</sub> single layer and CeO<sub>X</sub>/La<sub>2</sub>O<sub>3</sub> stack, respectively. All of these samples have similar EOT values. It was observed that the measured leakage current in CeO<sub>X</sub>/La<sub>2</sub>O<sub>3</sub> stack was the smallest among the three types of the measured samples; CeO<sub>X</sub> single layer, La<sub>2</sub>O<sub>3</sub> single layer and CeO<sub>X</sub>/La<sub>2</sub>O<sub>3</sub> stack. Figure 2 shows the relation between Leakage current and EOT in the fabricated capacitors at

a gate voltage of 1 V. Compare to CeO<sub>X</sub> and La<sub>2</sub>O<sub>3</sub> single layer dielectrics, the leakage current at EOT around 1.0 nm was suppressed by two orders compare to former one and was suppressed by one order compare to later one by introducing the CeO<sub>X</sub>/La<sub>2</sub>O<sub>3</sub> stacked insulator, strongly suggests the practical advantages of the CeO<sub>X</sub>/La<sub>2</sub>O<sub>3</sub> in reducing the leakage current.

## Conclusions

We have investigated the dielectric properties of  $CeO_x/La_2O_3$  gate stack. It was observed that the leakage can be suppressed by introducing the  $CeO_x/La_2O_3$  stacked insulator. Our results show that the advantages of the  $CeO_x/La_2O_3$  in reducing leakage current and the superior properties as one of the promising candidate of new high-k materials.

Figure 1 . J-V characteristics in the  $CeO_X$ ,  $La_2O_3$  single layer and  $CeO_X/La_2O_3$  stack structure capacitors.

Figure 2. Jg-EOT plot in the all samples.

#### Reference

- [1] Y. Nishikawa et al., Appl. Phys. Lett. Vol.81 No.23. pp. 4386.

- [2] H. Watanabe et al., Appl. Phys. Lett. Vol.83 No.17.

- [3] Okamoto et al,. ECS-24<sup>th</sup> Meeting-submited