## Hf 層界面挿入による Ni シリサイドのショットキー障壁変調技術

Schottky Barrier Height Control of Ni Silicide by Inserting Hf Interlayer

Tokyo Tech. FCRC <sup>1</sup>, Tokyo Tech. IGSSE <sup>2</sup> e-mail: matano.k.aa@m.titech.ac.jp

[はじめに]次世代 LSI に向けて極浅のソース・ドレイン接合が形成可能で、短チャネル効果を抑制できる Schottky Barrier Source/Drain MOSFET(SB-MOSFET)が期待されている。しかしながら SB-MOSFET では、Metal/Si 界面にできるショットキー障壁により駆動電流が低下する問題があり、障壁高さの低減が求められている。今回、シリサイド化前の Ni/Si 界面に Hf を挿入し、アニールによりシリサイド化させることで電子に対する障壁高さが低減できることがわかったので報告する。

[実験方法] SPM,DHF 処理した p-Si(100)基板(不純物濃度: $1\times10^{15} cm^{-3}$ )上に、スパッタ法により Hf を  $1.8 \sim 12 nm$  堆積した後、Ni(12 nm)を堆積した。そしてフォーミングガス( $N_2$ : $H_2$ =97:3)雰囲気中で RTA 処理( $400 \sim 700$  、60 秒間)を行った。その後、未反応金属を SPM により除去し、裏面電極として AI を蒸着した。製作したショットキー接合の I-V 特性からショットキー障壁高さを算出した。

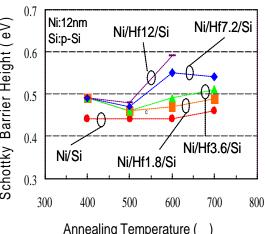

[結果]Fig.1 に正孔に対するショットキー障壁高さの RTA 温度依存性を示す。正孔に対して高いショットキー障壁を持つ Hf の効果[1]で全ての Hf 膜厚において障壁高さが上昇した。また、500 までは Hf 膜厚依存性は見られなかったが、600 以上では Hf 膜厚増加とともに障壁高さは増大し、最大 0.15eV の増大が得られた。以上のように、正孔に対する障壁高さの増加、すなわち、電子に対する障壁高さの低減が確認できた。詳細については当日報告する。

[参考文献]S.Zaima et al. J.Appl. Phys., Vol74,No.11,1 December (1993) 6703-6709

[謝辞]本研究は、科学研究費補助金特定領域研究シリコンナノエレクトロニクスの新展開-ポストスケーリングテクノロジー-の支援で行われた。

Fig. 1 Annealing temperature dependence of schottky barrier height for holes, for initial deposition strucutres of Ni/Hf/Si with various thickness of Hf layer.