**Master Thesis**

### Novel Gate Stack and Process Optimization for La<sub>2</sub>O<sub>3</sub>-MOSFET

Supervisor

Professor Hiroshi Iwai

Professor Nobuyuki Sugii

**Tokyo Institute of Technology**

**Department of Advanced Applied Electronics**

04M36125

Yusuke Kuroki

## **Contents**

| 1.1 Background of This study       2         1.2 Limits of SiO2       4         1.3 Requirements of high-k materials       5         1.4 Properties of La2O3       9         1.5 Purpose of This Study       12         Chapter 2 Fabrication and Characterization Methods       14         2.1 Experimental Procedure       15         2.1.1 Fabrication Procedure for MOS Capacitor       15         2.1.2 Fabrication Procedure for nMOSFET       16         2.2 Fabrication Methods       18         2.2.1 Wet Cleaning Method of Silicon Substrate       18         2.2.2 Electron-Beam Evaporation Method       20         2.2.3 Rapid Thermal Annealing (RTA) Method       22         2.4 Vacuum Evaporation Method       23         2.2.5 RF Magnetron Sputtering Method       26         2.3.1 Spectroscopic Ellipsometry       26         2.3.2 X-ray Photoelectron Spectroscopy (XPS)       28         2.3.3 Transmission Electron Microscopy (TEM)       30         2.4 Characterization of MOS Capacitor       31         2.4.1 Characterization of MOS Capacitor       31         2.4.1 Characterization of MOS Capacitor       31         2.4.1 Characterization of MOS Capacitor       31         2.4.2 Characterization of MOS Capacitor       31   | Chapter 1 Introduction                                    | 1  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----|

| 1.3 Requirements of high-k materials       5         1.4 Properties of La2O3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.1 Background of This study                              | 2  |

| 1.4 Properties of La2O3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.2 Limits of SiO <sub>2</sub>                            | 4  |

| 1.5 Purpose of This Study.       12         Chapter 2 Fabrication and Characterization Methods.       14         2.1 Experimental Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1.3 Requirements of high-k materials                      | 5  |

| Chapter 2 Fabrication and Characterization Methods.       14         2.1 Experimental Procedure       15         2.1.1 Fabrication Procedure for MOS Capacitor       15         2.1.2 Fabrication Procedure for MOS FET       16         2.2 Fabrication Methods       18         2.2.1 Wet Cleaning Method of Silicon Substrate       18         2.2.2 Electron-Beam Evaporation Method       20         2.2.3 Rapid Thermal Annealing (RTA) Method       22         2.4 Vacuum Evaporation Method       23         2.2.5 RF Magnetron Sputtering Method       24         2.2.6 Mask Aligner       25         2.3 Measurement Methods       26         2.3.1 Spectroscopic Ellipsometry.       26         2.3.2 X-ray Photoelectron Spectroscopy (XPS)       28         2.3.3 Transmission Electron Microscopy (TEM)       30         2.4 Characterization of MOS Capacitor       31         2.4.1 Characterization of MOS Capacitor       31         2.4.1 Characterization of MOS Capacitor       33         2.4.2 Characterization of MOSFET       34         2.4.2 Characterization of MOSFET       34         2.4.2 Characterization of MOSFET       34         2.4.2 Subthreshold Slope (S.S.) Measurement       35         2.4.2.3 Split C-V Method       36 | 1.4 Properties of La <sub>2</sub> O <sub>3</sub>          | 9  |

| 2.1 Experimental Procedure       15         2.1.1 Fabrication Procedure for MOS Capacitor       15         2.1.2 Fabrication Procedure for nMOSFET       16         2.2 Fabrication Methods       18         2.2.1 Wet Cleaning Method of Silicon Substrate       18         2.2.2 Electron-Beam Evaporation Method       20         2.2.3 Rapid Thermal Annealing (RTA) Method       22         2.2.4 Vacuum Evaporation Method       23         2.2.5 RF Magnetron Sputtering Method       24         2.2.6 Mask Aligner       25         2.3 Measurement Methods       26         2.3.1 Spectroscopic Ellipsometry       26         2.3.2 X-ray Photoelectron Spectroscopy (XPS)       28         2.3.3 Transmission Electron Microscopy (TEM)       30         2.4 Characterization of MOS Capacitor       31         2.4.1.1 C-V (Capacitance-Voltage) Measurement       31         2.4.2 Characterization of nMOSFET       34         2.4.2.2 Subthreshold Voltage (V <sub>th</sub> ) Measurement       34         2.4.2.3 Split C-V Method       36                                                                                                                                                                                                           | 1.5 Purpose of This Study                                 | 12 |

| 2.1.1 Fabrication Procedure for MOS Capacitor152.1.2 Fabrication Procedure for nMOSFET162.2 Fabrication Methods182.2.1 Wet Cleaning Method of Silicon Substrate182.2.2 Electron-Beam Evaporation Method202.2.3 Rapid Thermal Annealing (RTA) Method222.2.4 Vacuum Evaporation Method232.2.5 RF Magnetron Sputtering Method242.2.6 Mask Aligner252.3 Measurement Methods262.3.1 Spectroscopic Ellipsometry262.3.2 X-ray Photoelectron Spectroscopy (XPS)282.3.3 Transmission Electron Microscopy (TEM)302.4 Characterization of MOS Capacitor312.4.1.1 C-V (Capacitance-Voltage) Measurement312.4.2.1 Threshold Voltage (V <sub>th</sub> ) Measurement342.4.2.2 Subthreshold Slope (S.S.) Measurement352.4.2.3 Split C-V Method36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Chapter 2 Fabrication and Characterization Methods        | 14 |

| 2.1.2 Fabrication Procedure for nMOSFET162.2 Fabrication Methods182.2.1 Wet Cleaning Method of Silicon Substrate182.2.2 Electron-Beam Evaporation Method202.2.3 Rapid Thermal Annealing (RTA) Method222.2.4 Vacuum Evaporation Method232.2.5 RF Magnetron Sputtering Method242.2.6 Mask Aligner252.3 Measurement Methods262.3.1 Spectroscopic Ellipsometry262.3.2 X-ray Photoelectron Spectroscopy (XPS)282.3.3 Transmission Electron Microscopy (TEM)302.4 Characterization of MOS Capacitor312.4.1.1 C-V (Capacitance-Voltage) Measurement312.4.2.1 Threshold Voltage (V <sub>th</sub> ) Measurement342.4.2.2 Subthreshold Slope (S.S.) Measurement352.4.2.3 Split C-V Method36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.1 Experimental Procedure                                | 15 |

| 2.2 Fabrication Methods182.2.1 Wet Cleaning Method of Silicon Substrate182.2.2 Electron-Beam Evaporation Method202.2.3 Rapid Thermal Annealing (RTA) Method222.2.4 Vacuum Evaporation Method232.2.5 RF Magnetron Sputtering Method242.2.6 Mask Aligner252.3 Measurement Methods262.3.1 Spectroscopic Ellipsometry262.3.2 X-ray Photoelectron Spectroscopy (XPS)282.3.3 Transmission Electron Microscopy (TEM)302.4 Characterization Method312.4.1 Characterization of MOS Capacitor312.4.1.2 J-V (Leakage Current Density-Voltage) Measurement332.4.2 Characterization of nMOSFET342.4.2.3 Subthreshold Slope (S.S.) Measurement352.4.2.3 Split C-V Method36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2.1.1 Fabrication Procedure for MOS Capacitor             | 15 |

| 2.2.1 Wet Cleaning Method of Silicon Substrate182.2.2 Electron-Beam Evaporation Method202.2.3 Rapid Thermal Annealing (RTA) Method222.2.4 Vacuum Evaporation Method232.2.5 RF Magnetron Sputtering Method242.2.6 Mask Aligner252.3 Measurement Methods262.3.1 Spectroscopic Ellipsometry262.3.2 X-ray Photoelectron Spectroscopy (XPS)282.3.3 Transmission Electron Microscopy (TEM)302.4 Characterization Method312.4.1 Characterization of MOS Capacitor312.4.1.2 J-V (Leakage Current Density-Voltage) Measurement332.4.2 Characterization of nMOSFET342.4.2.1 Threshold Voltage (V <sub>th</sub> ) Measurement342.4.2.3 Split C-V Method36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.1.2 Fabrication Procedure for nMOSFET                   | 16 |

| 2.2.2 Electron-Beam Evaporation Method202.2.3 Rapid Thermal Annealing (RTA) Method222.2.4 Vacuum Evaporation Method232.2.5 RF Magnetron Sputtering Method242.2.6 Mask Aligner252.3 Measurement Methods262.3.1 Spectroscopic Ellipsometry262.3.2 X-ray Photoelectron Spectroscopy (XPS)282.3.3 Transmission Electron Microscopy (TEM)302.4 Characterization Method312.4.1 Characterization of MOS Capacitor312.4.1.2 J-V (Leakage Current Density-Voltage) Measurement332.4.2 Characterization of nMOSFET342.4.2.1 Threshold Voltage (V <sub>th</sub> ) Measurement342.4.2.3 Split C-V Method36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.2 Fabrication Methods                                   | 18 |

| 2.2.3 Rapid Thermal Annealing (RTA) Method.222.2.4 Vacuum Evaporation Method232.2.5 RF Magnetron Sputtering Method242.2.6 Mask Aligner252.3 Measurement Methods262.3.1 Spectroscopic Ellipsometry262.3.2 X-ray Photoelectron Spectroscopy (XPS)282.3.3 Transmission Electron Microscopy (TEM)302.4 Characterization Method312.4.1 Characterization of MOS Capacitor312.4.1.2 J-V (Leakage Current Density-Voltage) Measurement332.4.2 Characterization of nMOSFET342.4.2.1 Threshold Voltage (V <sub>th</sub> ) Measurement342.4.2.3 Split C-V Method36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2.2.1 Wet Cleaning Method of Silicon Substrate            | 18 |

| 2.2.4 Vacuum Evaporation Method232.2.5 RF Magnetron Sputtering Method242.2.6 Mask Aligner252.3 Measurement Methods262.3.1 Spectroscopic Ellipsometry262.3.2 X-ray Photoelectron Spectroscopy (XPS)282.3.3 Transmission Electron Microscopy (TEM)302.4 Characterization Method312.4.1 Characterization of MOS Capacitor312.4.1.1 C-V (Capacitance-Voltage) Measurement312.4.2.2 Subthreshold Slope (S.S.) Measurement342.4.2.3 Split C-V Method36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2.2.2 Electron-Beam Evaporation Method                    | 20 |

| 2.2.5 RF Magnetron Sputtering Method242.2.6 Mask Aligner252.3 Measurement Methods262.3.1 Spectroscopic Ellipsometry262.3.2 X-ray Photoelectron Spectroscopy (XPS)282.3.3 Transmission Electron Microscopy (TEM)302.4 Characterization Method312.4.1 Characterization Method312.4.1.1 C-V (Capacitance-Voltage) Measurement312.4.1.2 J-V (Leakage Current Density-Voltage) Measurement332.4.2 Characterization of nMOSFET342.4.2.1 Threshold Voltage (Vth) Measurement342.4.2.3 Split C-V Method36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.2.3 Rapid Thermal Annealing (RTA) Method                | 22 |

| 2.2.6 Mask Aligner252.3 Measurement Methods262.3.1 Spectroscopic Ellipsometry262.3.2 X-ray Photoelectron Spectroscopy (XPS)282.3.3 Transmission Electron Microscopy (TEM)302.4 Characterization Method312.4.1 Characterization of MOS Capacitor312.4.1.1 C-V (Capacitance-Voltage) Measurement312.4.1.2 J-V (Leakage Current Density-Voltage) Measurement332.4.2.1 Threshold Voltage (V <sub>th</sub> ) Measurement342.4.2.2 Subthreshold Slope (S.S.) Measurement352.4.2.3 Split C-V Method36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.2.4 Vacuum Evaporation Method                           | 23 |

| 2.3 Measurement Methods262.3.1 Spectroscopic Ellipsometry262.3.2 X-ray Photoelectron Spectroscopy (XPS)282.3.3 Transmission Electron Microscopy (TEM)302.4 Characterization Method312.4.1 Characterization of MOS Capacitor312.4.1.1 C-V (Capacitance-Voltage) Measurement312.4.1.2 J-V (Leakage Current Density-Voltage) Measurement332.4.2 Characterization of nMOSFET342.4.2.1 Threshold Voltage (Vth) Measurement352.4.2.3 Split C-V Method36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.2.5 RF Magnetron Sputtering Method                      | 24 |

| 2.3.1 Spectroscopic Ellipsometry.262.3.2 X-ray Photoelectron Spectroscopy (XPS).282.3.3 Transmission Electron Microscopy (TEM)302.4 Characterization Method.312.4.1 Characterization of MOS Capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.2.6 Mask Aligner                                        | 25 |

| 2.3.2 X-ray Photoelectron Spectroscopy (XPS)       28         2.3.3 Transmission Electron Microscopy (TEM)       30         2.4 Characterization Method       31         2.4.1 Characterization of MOS Capacitor       31         2.4.1 Characterization of MOS Capacitor       31         2.4.1.1 C-V (Capacitance-Voltage) Measurement       31         2.4.1.2 J-V (Leakage Current Density-Voltage) Measurement       33         2.4.2 Characterization of nMOSFET       34         2.4.2.1 Threshold Voltage (V <sub>th</sub> ) Measurement       34         2.4.2.2 Subthreshold Slope (S.S.) Measurement       35         2.4.2.3 Split C-V Method       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2.3 Measurement Methods                                   | 26 |

| 2.3.3 Transmission Electron Microscopy (TEM)       30         2.4 Characterization Method       31         2.4.1 Characterization of MOS Capacitor       31         2.4.1 Characterization of MOS Capacitor       31         2.4.1.1 C-V (Capacitance-Voltage) Measurement       31         2.4.1.2 J-V (Leakage Current Density-Voltage) Measurement       33         2.4.2 Characterization of nMOSFET       34         2.4.2.1 Threshold Voltage (V <sub>th</sub> ) Measurement       34         2.4.2.2 Subthreshold Slope (S.S.) Measurement       35         2.4.2.3 Split C-V Method       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2.3.1 Spectroscopic Ellipsometry                          | 26 |

| 2.4 Characterization Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.3.2 X-ray Photoelectron Spectroscopy (XPS)              | 28 |

| 2.4.1 Characterization of MOS Capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2.3.3 Transmission Electron Microscopy (TEM)              | 30 |

| 2.4.1.1 C-V (Capacitance-Voltage) Measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.4 Characterization Method                               | 31 |

| 2.4.1.2 J-V (Leakage Current Density-Voltage) Measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.4.1 Characterization of MOS Capacitor                   | 31 |

| 2.4.2 Characterization of nMOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.4.1.1 C-V (Capacitance-Voltage) Measurement             | 31 |

| 2.4.2.1 Threshold Voltage (Vth) Measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.4.1.2 J-V (Leakage Current Density-Voltage) Measurement | 33 |

| 2.4.2.2 Subthreshold Slope (S.S.) Measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.4.2 Characterization of nMOSFET                         | 34 |

| 2.4.2.3 Split C-V Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.4.2.1 Threshold Voltage (V <sub>th</sub> ) Measurement  | 34 |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.4.2.2 Subthreshold Slope (S.S.) Measurement             | 35 |

| 2.4.2.4 Charge Pumping Method 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2.4.2.3 Split C-V Method                                  | 36 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2.4.2.4 Charge Pumping Method                             | 37 |

| Chapter 3 Evaluation of Al Gate La <sub>2</sub> O <sub>3</sub> nMOSFETs              | . 38 |

|--------------------------------------------------------------------------------------|------|

| 3.1 The effect of PDA on Al Gate La2O3 nMOSFETs                                      | . 39 |

| 3.1.1 Experimental Procedure                                                         | . 39 |

| 3.1.2 C-V characteristics of MOS Capacitors                                          | . 39 |

| 3.1.3 Electrical Characteristics of nMOSFETs                                         | . 40 |

| 3.1.3.1 $I_d$ - $V_d$ and $I_d$ - $V_g$ Characteristics                              | . 40 |

| 3.1.3.2 Dependence of Annealing Ambient on V <sub>th</sub> and S.S                   | . 42 |

| 3.1.3.3 Effective Electron Mobility ( $\mu_{eff}$ )                                  | . 42 |

| 3.1.4 Investigation at the La <sub>2</sub> O <sub>3</sub> /Si interfaces by XPS      | . 43 |

| 3.1.5 Summery                                                                        | . 46 |

| 3.2 The effect of PMA on Al Gate La2O3 nMOSFETs                                      | . 47 |

| 3.2.1 C-V Characteristics of MOS Capacitors                                          | . 47 |

| 3.2.2 Electrical Characteristics of nMOSFETs                                         | . 47 |

| <b>3.2.2.1</b> $I_d$ - $V_d$ and $I_d$ - $V_g$ Characteristics                       | . 47 |

| 3.2.2.2 $J_g$ - $V_g$ characteristics                                                | . 49 |

| 3.2.2.3 Effective Electron Mobility ( $\mu_{eff}$ )                                  | . 49 |

| 3.2.3 Investigation at the Metal/La <sub>2</sub> O <sub>3</sub> interfaces by XPS    | . 50 |

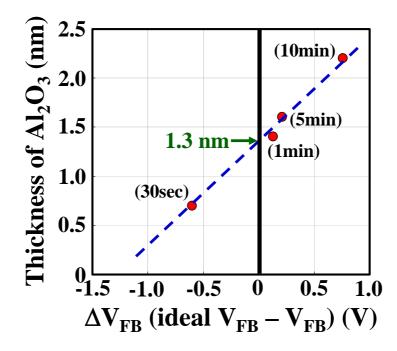

| 3.2.4 Estimation of the Al <sub>2</sub> O <sub>3</sub> thickness after PMA treatment | . 51 |

| 3.2.5 The proposed model for mobility improvement                                    | . 54 |

| 3.2.6 Summary                                                                        | . 54 |

|                                                                                      |      |

| Chapter 4 Evaluation of W Gate La <sub>2</sub> O <sub>3</sub> nMOSFETs               | . 55 |

| 4.1 Investigation of Gate Electrode Materials                                        | . 56 |

| 4.1.1 Experimental Procedure                                                         | . 56 |

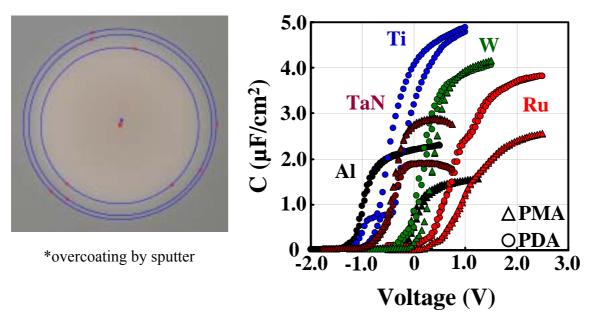

| 4.1.2 C-V Characteristics of Each Electrode                                          | . 56 |

| 4.2 Evaluation of W Gate La <sub>2</sub> O <sub>3</sub> nMOSFETs                     | . 57 |

| 4.2.1 Comparison with Evaporation and Sputter                                        | . 57 |

| 4.2.1.1 Experimental Procedure                                                       | . 57 |

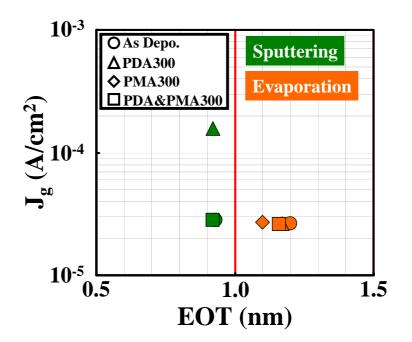

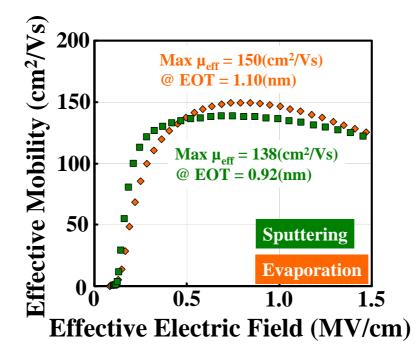

| 4.2.1.2 $J_g$ -EOT characteristics                                                   | . 57 |

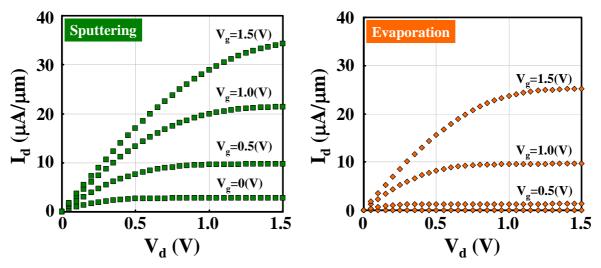

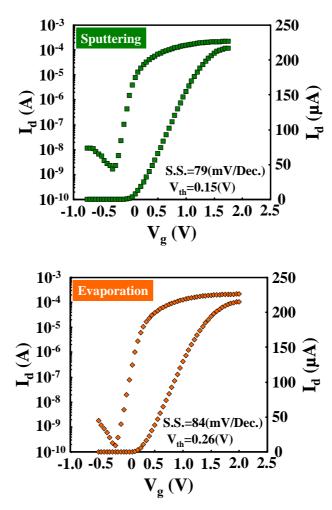

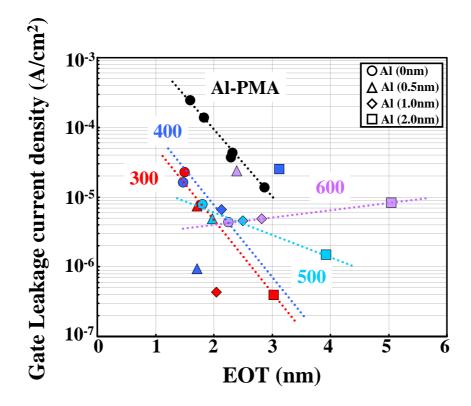

| 4.2.1.3 Electrical Characteristics of W Gate La2O3 nMOSFEs                           | . 58 |

| 4.2.1.4 Summery                                                                      | . 60 |

| 4.3.2 Investigation of W/Al/La <sub>2</sub> O <sub>3</sub> Structure                 | . 61 |

| 4.3.2.1 Experimental Procedure                                                       | . 61 |

| 4.3.2.2 $J_g$ -EOT Characteristics                                                   | . 61 |

| 4.3.2.3 S.S. and V <sub>th</sub>                                                     | . 62 |

| 4.3.2.4 Effective Electron Mobility ( $\mu_{eff}$ )                                  | 64   |

| 4.3.2.4 Interface Trap Density (D <sub>it</sub> )       |  |

|---------------------------------------------------------|--|

| 4.3.2.5 Low Temperature Measurement                     |  |

| 4.3.2.6 Summery                                         |  |

| Chapter 5 Conclusions                                   |  |

| 5.1 Results of This Study                               |  |

| 5.1.1 Al Gate La <sub>2</sub> O <sub>3</sub> nMOSFETs   |  |

| 5.1.2 W Gate La <sub>2</sub> O <sub>3</sub> nMOSFETs    |  |

| 5.2 Future Prospects for La <sub>2</sub> O <sub>3</sub> |  |

| Acknowledgments                                         |  |

| References                                              |  |

## **Chapter 1**

## **Introduction**

#### **1.1 Background of This study**

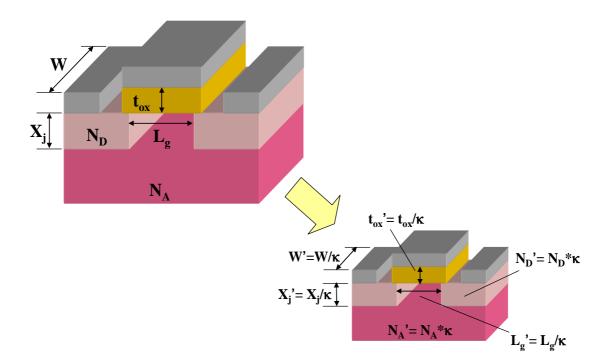

In recent years, our lives are becoming affluent with the global promotion of Information Technology (IT) as represented by computers, internets and cell-phones. As it is now, these are fundamental part of everyday life. These information equipments are realized by astonishing progress in silicon LSI (Large-Scale Integration) technology. The performance of silicon LSI depends capability of on the the Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET) which is core part of LSI systems. In order to obtain high performance devises, it is necessary to miniaturize the MOSFET with the scaling method. The scaling method is based on reducing the device dimension in both lateral and vertical. The consensus scenario of how the device parameters are scaled for the next technology is provided in the International Technology Roadmap for Semiconductor (ITRS). A simple description of miniaturization with scaling factor of  $\kappa$  is shown in Figure 1.1 and Table 1.1. To gain  $\kappa$ times of the device performance, the physical device dimensions are reduced by  $\kappa$  times, while the electrical parameters are increased by  $\kappa$  times.

Figure 1.1 : Scaling Method.

| Parameter            | Inisial                    | Scaled             |

|----------------------|----------------------------|--------------------|

| Channel Length       | L                          | L/κ                |

| Channel Width        | W                          | W/ĸ                |

| Total Device Area    | Α                          | A/κ <sup>2</sup>   |

| Gate Oxide Thickness | t <sub>ox</sub>            | t <sub>ox</sub> /κ |

| Gate Capacitance     | C <sub>ox</sub>            | C <sub>ox</sub> *к |

| Junction Depth       | Xj                         | X <sub>j</sub> /κ  |

| Power Supply Voltage | $\mathbf{V}_{\mathbf{dd}}$ | $V_{dd}/\kappa$    |

| Threshold Voltage    | $\mathbf{V_{th}}$          | $V_{th}/\kappa$    |

| Doning Concentration | N <sub>A</sub>             | N <sub>A</sub> *κ  |

| Doping Concentration | N <sub>D</sub>             | N <sub>D</sub> *κ  |

Table 1.1 : Scaling of MOSFET by the scaling factor  $\kappa.$

#### **1.2 Limits of SiO<sub>2</sub>**

As is well known, Silicon dioxide film  $(SiO_2)$  is the most common materials as gate insulator film. However, a big hurdle is confronted to miniaturize the element size as in the past with keeping high performance and high integration.

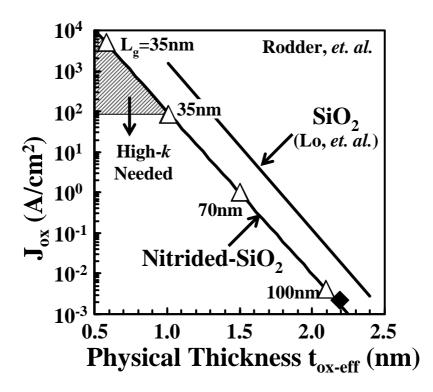

From ITRS 2004 up date (Table 1.2), Equivalent Oxide Thickness (EOT) will rise to the below 1nm level in near future. On the other hand, the direct-tunneling leakage current is too increasing to be neglected as shown in Figure 1.2. Therefore,  $SiO_2$  gate insulator film is to be replaced with an alternative material, which can be suppressed leakage current.

| Year of Production                                   | 2005                 | 2007                 | 2010                 | 2014                 | 2018                        |

|------------------------------------------------------|----------------------|----------------------|----------------------|----------------------|-----------------------------|

| Physical Gate Length (nm)                            | 32                   | 25                   | 18                   | 11                   | 7                           |

| EOT (nm)                                             | 1.1                  | 0.9                  | 0.7                  | 0.6                  | 0.5                         |

| Gate Leakage Current<br>Density (A/cm <sup>2</sup> ) | 5.20*10 <sup>2</sup> | 9.30*10 <sup>2</sup> | 1.90*10 <sup>3</sup> | 9.09*10 <sup>3</sup> | <b>2.40*10</b> <sup>4</sup> |

| Power Supply Voltage (V)                             | 1.1                  | 1.1                  | 1.0                  | 0.9                  | 0.7                         |

Table 1.2 : ITRS 2004 up date.

Figure 1.2 : Relations between gate leakage current and physical thickness of SiO<sub>2</sub> film.

#### **1.3 Requirements of high-k materials**

To overcome this problem, high-k (high dielectric constant) materials have been attracted much attention. The key guidelines for selecting an alternative gate dielectric material are high dielectric constant, large band gap and band alignment to silicon, thermodynamic stability, film morphology, interface quality, process compatibility, and reliability. Among them, high dielectric constant and large band gap are the minimum required characteristics to suppress the gate leakage current. The direct-tunneling leakage current ( $J_{DT}$ ) flow through a gate insulator film is determined by the tunneling probability of carrier. The tunneling probability of carrier ( $D_{DT}$ ) is shown in below equation where physical thickness of insulator (d), electron effective mass in the gate insulator film ( $m^*$ ) and barrier height of insulator ( $\phi_b$ ).

$$J_{DT} \propto D_{DT} \propto \exp\left\{-\frac{4\pi d \left(2m * \phi_b\right)^{\frac{1}{2}}}{h}\right\}$$

Relationship between physical thickness of SiO<sub>2</sub> ( $d_{EOT}$ ) and physical thickness of high-k gate insulator (d) obtained by the same gate capacitance value (C) is shown in below equation where dielectric constant of SiO<sub>2</sub> ( $\varepsilon_{ox}$ ) and high-k gate insulator ( $\varepsilon_{high-k}$ ).

$$C = \frac{\varepsilon_{high-k}}{d} = \frac{\varepsilon_{ox}}{d_{EOT}}$$

$$d = \frac{\varepsilon_{ox}}{\varepsilon_{high-k}} d_{EOT}$$

Therefore, the gate leakage current can be suppressed by using high-k materials, which means that the physical thickness of high-k films can be thicken without changing EOT. In addition, the gate leakage current can also be suppressed by using large band gap materials.

The possible candidate of several metal oxides system for the use of gate dielectric materials is shown in white spaces of Table 1.3.

| Н  | <ul> <li>= Not a solid at 1000 K</li> <li>= Radioactive</li> <li>= Failed reaction 1: Si + MO<sub>x</sub> M + SiO<sub>2</sub></li> </ul> |    |        |        |        |         |      |     |        |                                 |    |    | Не |    |    |    |    |

|----|------------------------------------------------------------------------------------------------------------------------------------------|----|--------|--------|--------|---------|------|-----|--------|---------------------------------|----|----|----|----|----|----|----|

| Li | Be                                                                                                                                       |    |        |        |        |         | - MO | ~   |        | - SiO <sub>2</sub>              | 2  | В  | С  | N  | 0  | F  | Ne |

| Na | Mg                                                                                                                                       | =  | Failed | l reac | tion 6 | 5: Si - | + MO | x N | /I + M | [Si <sub>x</sub> O <sub>y</sub> | y  | Al | Si | Р  | S  | Cl | Ar |

| K  | Ca                                                                                                                                       | Sc | Ti     | v      | Cr     | Mn      | Fc   | Co  | Ni     | Cu                              | Zn | Ga | Ge | As | Se | Br | Kr |

| Rh | Sr                                                                                                                                       | Y  | Zr     | Nb     | Мо     | Тс      | Ru   | Rb  | Pd     | Ag                              | Cd | In | Sn | Sb | Те | Ι  | Xe |

| Cs | Ba                                                                                                                                       | R  | Hf     | Та     | w      | Re      | Os   | Ir  | Pt     | Au                              | Hg | Tl | Pb | Bi | Ро | At | Rn |

| Fr | Ra                                                                                                                                       | А  | Rf     | Ha     | Sg     | Ns      | Hs   | Mt  |        |                                 |    |    |    |    |    |    |    |

| R | La | Ce | Pr | Nd | Pm | Sm | Eu | Gd | Tb | Dy | Но | Er | Tm | Yb | Lu |

|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| A | Ac | Th | Pa | U  | Np | Pu | Am | Cm | Bk | Cf | Es | Fm | Md | No | Lr |

Table 1.3 : Candidate of metal oxides that has possibility to be used as high-k gate insulator.

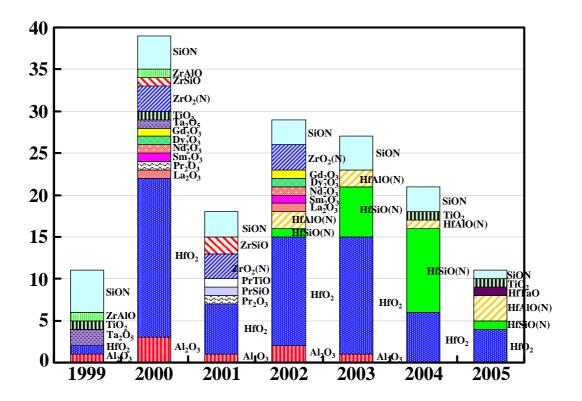

Among the candidate of high-k materials, Hf-based materials are the most promising candidate of them. As shown in Figure 1.3, many papers on high-k materials are submitted in the primary conferences up to 2002. However, from 2003 to now, the candidate of high-k materials have narrowed down to Hf-based materials. Therefore, Hf oxides (HfO<sub>2</sub>) and Hf-based silicates or nitrides (HfSiON), with dielectric constants of 25 and 10 to 15 respectively, are among the promising materials for the 65 or 45-nm-technology nodes.

Usually, when the EOT becomes small, the effective carrier mobility tends to decrease due to scattering in the high-k layer or at the interface between the high-k layer and the substrate. It has reported that Hf-based films have reduced scattering when a SiO<sub>2</sub>-based interfacial layer of 0.5 to 0.7 nm is inserted, however, this attempt increases

the EOT.

Consequently, in this work, Lanthanum Oxide  $(La_2O_3)$ , one of the rare earth oxides, has been tried as a gate insulator, because it has a relatively high dielectric constant of 27, which is slightly higher than that of HfO<sub>2</sub> and a high band offset of 2.3 eV from the conduction band of silicon to La<sub>2</sub>O<sub>3</sub> has the advantage of further reducing the leakage current.

Figure 1.3 : Reported High-k materials.

#### 1.4 Properties of La<sub>2</sub>O<sub>3</sub>

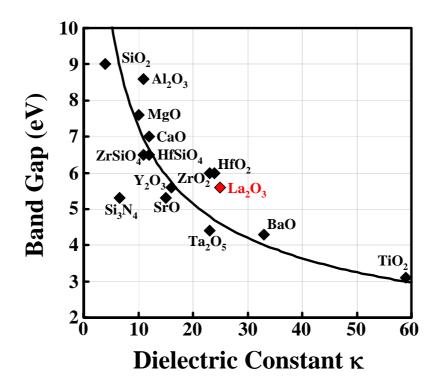

To perform a low EOT, high-k gate dielectrics materials must have high enough dielectric constant. However, material with very high dielectric constant tends to have narrower band gap that allows higher Schottky conduction currents and tunneling currents. Figure 1.4 shows band gap energy of several metal oxide and silicate materials as a function of dielectric constants. La<sub>2</sub>O<sub>3</sub> gives high dielectric constant of 27 and wide band gap of 5.6 eV that is suitable for the use of gate dielectrics.

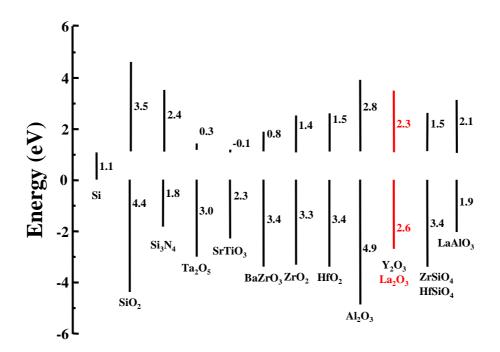

To inhibit a low leakage current due to Schottky emission conduction mechanism, the high- $\kappa$  gate dielectric materials must have wide band gap and high barrier of more than 1 eV for both electrons and holes. Figure 1.5 predicted band offset of several binary and ternary metal oxides in alignment with silicon band energy. La<sub>2</sub>O<sub>3</sub> has a good symmetrical band barrier of more than 2 eV for both electrons and holes that is compatible for CMOS devices.

Figure 1.4 : Band gap energy of several metal oxide and silicate materials as a function of dielectric constant.

Figure 1.5 : Predicted band offset of several binary and ternary metal oxides in alignment with silicon band energy.

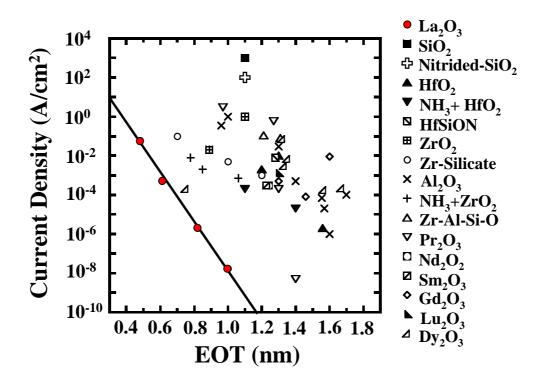

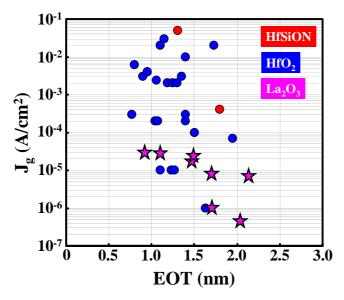

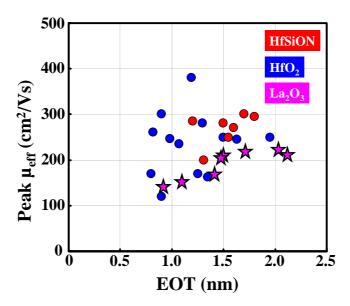

Previously, excellent results on several high-k gate dielectrics materials have been reported. Figure 1.6 shows reported leakage current density of various high-k gate materials as a function of EOT. From Figure 1.6, the superiority of La<sub>2</sub>O<sub>3</sub> is obvious, low EOT with low leakage current can be achieved with La<sub>2</sub>O<sub>3</sub>.

Finally,  $La_2O_3$  is considered to be the most promising gate dielectric material for the next generation gate dielectric technology.  $La_2O_3$  material shows good physical properties, high dielectric constant of 27, wide band gap of 5.6 eV, symmetrical band offset for electrons and holes of more than 2 eV, and good thermal stability in contact with silicon. In this study, the electrical properties of MOSFET with  $La_2O_3$  gate dielectrics will be evaluated.

Figure 1.6 : Reported leakage current density of various high-k gate materials as a function of EOT.

#### 1.5 Purpose of This Study

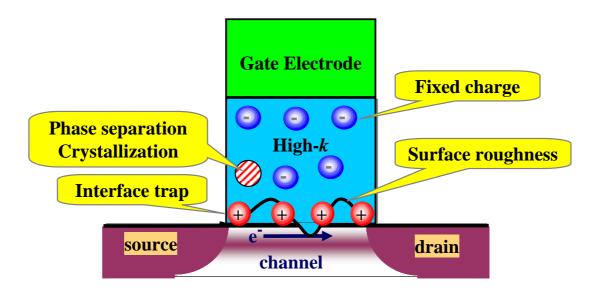

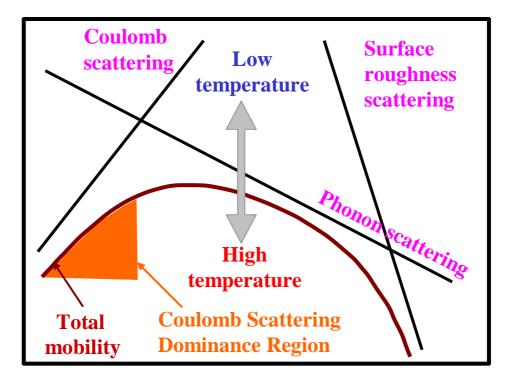

One of the serious problems for the high-k gate insulator is mobility degradation. The mobility is the most important factor to achieve the high performance MOSFET. However, using high-k materials as gate insulator, mobility degradation become more and more prominent as compared to the  $SiO_2$  film, which is due to the high amount of fixed charge, interface trapped charge and so on (Figure1.7). As shown in Figure 1.8, these defects become center of the Coulomb Scattering to degrade mobility.

Thus, in this work, we mainly discuss the mobility and study on process optimization for  $La_2O_3$  nMOSFETs to improve the mobility.

Figure 1.7 : The factor of mobility degradation.

Figure 1.8 : Metric for Mobility Progress.

## **Chapter 2**

# <u>Fabrication</u> <u>and</u> Characterization

## **Methods**

In this chapter, we describe the details of procedures, instrumentations, appliances, and tools for fabrications and characterizations of  $La_2O_3$  Metal-Oxide-Substrate Capacitor (MOS Capacitor) and n-channel Metal-Oxide-Semiconductor Field Effect Transistor (nMOSFET).

#### **2.1 Experimental Procedure**

#### 2.1.1 Fabrication Procedure for MOS Capacitor

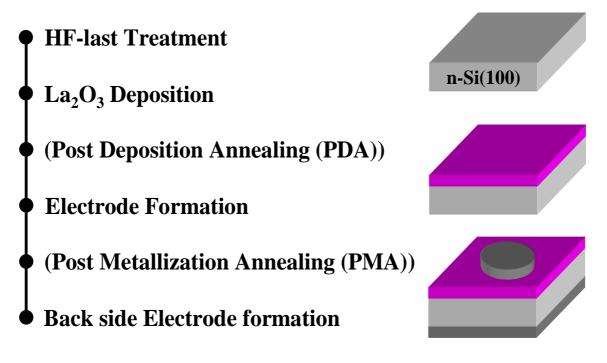

The fabrication procedure for MOS Capacitor is shown in Figure 2.1. La<sub>2</sub>O<sub>3</sub> thin films were deposited on n-type silicon (100) substrate by Electron-Beam Evaporation. at substrate temperature 250°C followed by H<sub>2</sub>SO<sub>4</sub>/H<sub>2</sub>O<sub>2</sub> mixture (SPM) cleaning and HF-dip processes. Then, upper electrode and back side electrode were formed by Vacuum Evaporation Method or RF Magnetron Sputtering Method. In this experiment, we performed two type of the annealing method using Rapid Thermal Annealing (RTA) method. One is the Post Deposition Annealing (PDA) and the other is the Post Metallization Annealing (PMA). Detailed explanation of each process and experimental equipment will be described in next section.

Figure 2.1 : The fabrication procedure for MOSCAP.

#### 2.1.2 Fabrication Procedure for nMOSFET

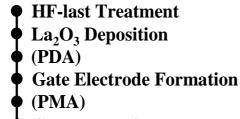

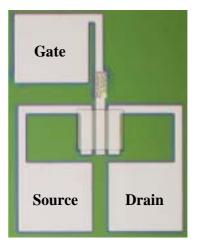

The fabrication procedure for nMOSFET is shown in Figure 2.2 and the cross-sectional description in La<sub>2</sub>O<sub>3</sub> nMOSFET fabrication is shown in Figure 2.3. nMOSFET fabrication was started from S/D implanted Si(100) substrate. La<sub>2</sub>O<sub>3</sub> thin film was deposited by Electron-Beam Evaporation followed by substrate cleaning. After metal gate formation, the gate area was defined with photolithography followed by metal gate etching. The Al-Pad area was formed with lift-off process under acetone solution and Al back side electrode were formed afterwards.

- Gate Patterning

- Gate Etching

- S/D Pad Patterning

- Al Pad Deposition

- Pad Formation with Lift-off

- Back side Electrode formation

Figure 2.2 : The fabrication procedure for nMOSFET.

Figure 2.3 : Cross section description in La<sub>2</sub>O<sub>3</sub> nMOSFET fabrication procedure.

#### **2.2 Fabrication Methods**

#### 2.2.1 Wet Cleaning Method of Silicon Substrate

Prior to deposit of high-k gate thin films for LSI fabrication process, the ultra-pure surface of a bare Si-substrate should be chemically cleaned to remove particles contamination, such as metal contamination, organic contamination, ionic contamination, water absorption, native oxide and atomic scale roughness. It is considered that this substrate cleaning process is very important to realize desirable device operation and its reproducibility.

In full fabrication processes as well as substrate cleaning, DI (de-ionized) water is one of the most important because DI water is highly purified and filtered to remove all traces of ionic, particulate, and bacterial contamination. Theoretical resistively of pure water at 25°C is 18.3 MQ·cm. The resistively value of ultra-pure water (UPW) used in this study achieve more than 18.2 MQ·cm and have fewer than 1.2 colony of bacteria per milliliter and no particle larger than 0.25 um.

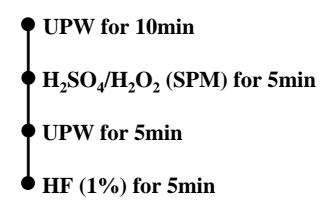

In this study, the method of substrate cleaning process was used a typical processing using hydrofluoric acid, which is usually called RCA cleaning method, was proposed by W. Kern et al. But some steps were reduced. The steps were shown in Fig.2.4. Firstly, a cleaning steps in solution of sulfuric acid  $(H_2SO_4)$  / hydrogen peroxide  $(H_2O_2)$  ( $H_2SO_4$ : $H_2O_2 = 1:4$ , called by SPM) performed to remove any organic material and metallic impurities after UPW cleaning. Secondly, the step in a solution of dilated hydrofluoric acid ( $HF:H_2O=1:100$ ) was performed to remove chemically and native oxides which might have been formed on Si surface. Final step was dipped in UPW

because hydrogen-terminated surface.

Figure 2.4 : Si Surface cleaning process.

#### **2.2.2 Electron-Beam Evaporation Method**

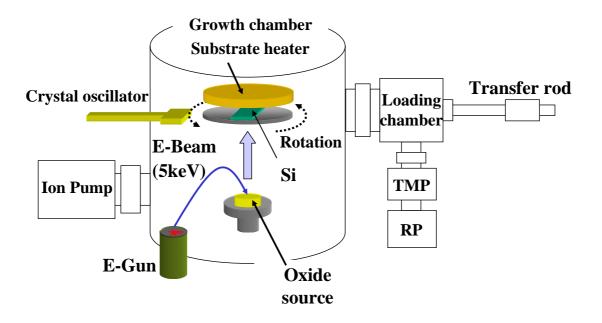

Electron-Beam Evaporation method using MBD equipment is employed for depositing  $La_2O_3$  in this study.

Figure 2.5 shows the schematic drawings of the equipment and inside of its growth chamber. Air in the loading chamber is removed to degree of a vacuum of  $10^{-8}$  Torr by a turbo molecular pump connected to a rotary pump. Vacuum in the growth chamber reaches as high as  $10^{-10}$  Torr by the removal of air with an ion pump and the introduction of liquid N<sub>2</sub> trap.

In the growth chamber, sintered  $La_2O_3$  target, which is evaporation source, is irradiated with electron beam accelerated by -5 kV. The target is heated up and  $La_2O_3$ molecules are evaporated. Then ultra thin  $La_2O_3$  film is deposited on the Si-substrate. The degree of a vacuum is from  $10^{-7}$  to  $10^{-8}$  Torr while deposition. The substrate rotates 10 times per 1 minute horizontally to uniform the film thickness. Physical thickness of the film is monitored with a film thickness counter using crystal oscillator. The temperature of the substrate is controlled by a substrate heater and is measured by a thermocouple.

Figure 2.5 : Schematic drawing of e-beam evaporation system.

#### 2.2.3 Rapid Thermal Annealing (RTA) Method

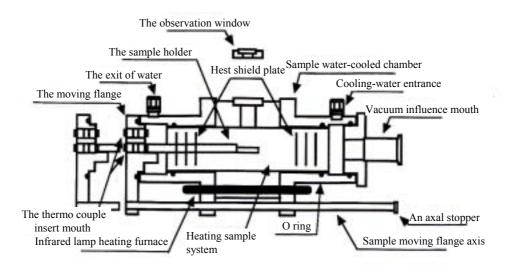

Thermal processes are often used for defects recovery or molecular introduction to dielectric thin films, for lattice recovery or impurity electrical activation of doped or ion implanted wafers. In this experiment, Rapid Thermal Processing MILA-3000 from ULVAC is used for annealing deposited  $La_2O_3$  thin films. Figure 2.6 illustrated the schematic drawing for MILA-3000. High purity gas ambience can be obtained by pumping out and purging with the in use ambient gas. This RTP system is heated-up by infrared lamp heating furnace and cooled-down by flowing water radiator. The furnace temperature is of the range from room temperature to around 1200°C with ramp-up of less than 50°C/sec and much slower on cooling-down. The available of ambient gases are  $N_2$  and  $O_2$  at atmospheric pressure by keeping the flowing gas at the rate of 1 lt./min.

Figure 2.6 : Schematic drawing for Rapid Thermal Annealing (RTA) MILA-3000.

#### **2.2.4 Vacuum Evaporation Method**

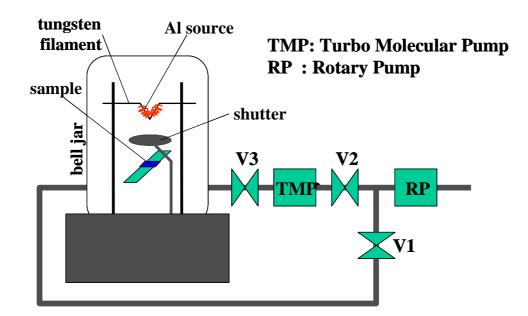

All of Al metals in this work were obtained from deposition with bell jar vacuum thermal evaporation. Figure 2.7 illustrates a schematic drawing for vacuum thermal evaporation system. The system is utilized with Turbo Molecular Pump (TMP) to pump down to several  $10^{-5}$  Torr. In case of MOS capacitor fabrication, metal shadow mask with circle opening of 200 µm diameters was used. Filament is made of tungsten, was used for heating the Al source up to its vapor temperature. Both filaments and Al sources are made of Nilaco, inc. with material purity of 99.999%.

Figure 2.7 : Schematic drawing for vacuum thermal evaporation system.

#### 2.2.5 RF Magnetron Sputtering Method

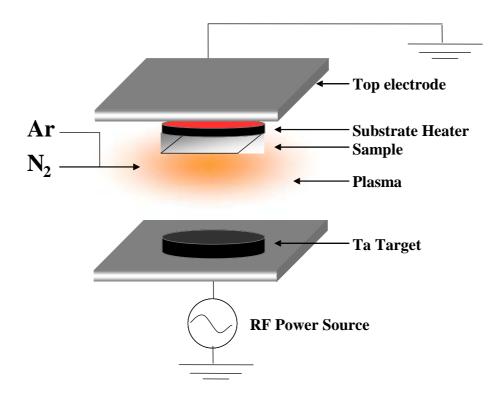

Some of a gate electrode material was deposited by RF magnetron sputtering method. Figure 2.8 illustrates a schematic drawing for RF magnetron sputtering system. This equipment deposits metal film by means of physical sputtering that occurs in a magnetically-confined RF plasma discharge of an inert Ar gas. Before the introduction of gases (Ar, Kr, N<sub>2</sub> or O<sub>2</sub>), the process chamber was evacuated to degree of  $10^{-5}$  Pa by a turbo molecular pump connected to a rotary pump and a liquid N<sub>2</sub> trap. The flow rate of gases is (7sccm) controlled by mass flow. The RF power supply system has auto impedance matching equipment and its capability of power supply is ~ 500W.

Figure 2.8 : Schematic drawing for RF magnetron sputtering system.

#### 2.2.6 Mask Aligner

The spin-coated photoresist was exposed through the mask with high-intensity ultraviolet light (405 nm). In this study, the exposure process was performed by contact-type mask aligner, MJB3 (Karl Suss Co. Ltd.). The exposure time was set to 12 sec. The photo-resist was developed using the specified developer (NMD-3, Tokyo Ohka Co. Ltd.).

#### **2.3 Measurement Methods**

#### 2.3.1 Spectroscopic Ellipsometry

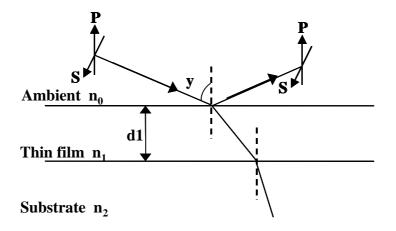

Spectroscopic Ellipsometry is used predominantly to measure the thickness of thin dielectric films on highly absorbing substrates but can also be used to determine the optical constants of films or substrates. Figure 2.9 shows the plane-polarized light incident on a plane surface. The incident polarized light can be resolved into a component p, parallel to the plane of incidence and a component s perpendicular to the plane of incidence. The light propagates as a fluctuation in electric and magnetic fields at right angles to the direction of propagation. The reflection coefficients

$$R_{p} = \frac{E_{p}(reflected)}{E_{p}(incident)}$$

$$R_{s} = \frac{E_{s}(reflected)}{E_{s}(incident)}$$

are not separately measurable. However, the complex reflection ratio  $\rho$  defined in terms of the reflection coefficients  $R_p$  and  $R_s$  or ellipsometric angles  $\psi$  and  $\Delta$

$$\rho = \frac{R_p}{R_s} = \tan(\psi)e^{j\Delta}$$

is measurable. Then,  $\psi$  and  $\Delta$  are called ellipso parameter.

For the air(n<sub>0</sub>)-thin film(n<sub>1</sub>)-substrate(n<sub>2</sub>-jk<sub>2</sub>) substrate system, where n<sub>x</sub> is the index of refraction and k<sub>x</sub> the extinction coefficient. In case of Si substrate, n<sub>2</sub> and k<sub>2</sub> are known, then n<sub>1</sub> and film thickness may be calculated from the result of  $\psi$  and  $\Delta$  measurement.

Figure 2.9 : Principle of Ellipsometry.

#### 2.3.2 X-ray Photoelectron Spectroscopy (XPS)

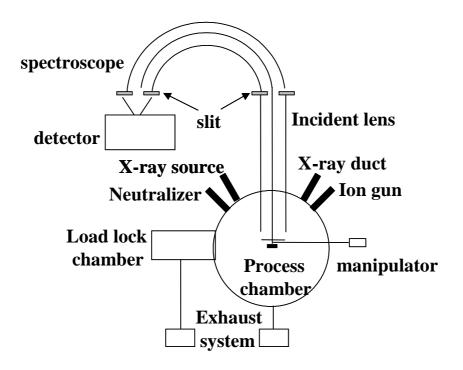

Chemical state of a few nm surface layers is analyzed by X-ray Photoelectron Spectroscopy (XPS) as shown in Fig.2.10. An electron is emitted by the photoelectric effect when homogeneous light is applied material. The measuring method of electron energy and intensity distribution is called XPS method.

$$E_{kin}^{\nu} = h\nu - E_b - \phi$$

where  $E_{kin}^{\nu}$ ,  $h\nu$ ,  $E_b$  and  $\phi$  are kinetic energy of liberated photoelectron, incident X-ray energy, binding energy of emitted electron for sample and work function for sample. If  $h\nu$  is constant, binding energy can be obtained by measuring the kinetic energy of emitted electron. Identification of element is easily possible by measuring  $E_{kin}^{\nu}$  because binding energy of each electron orbit is different. On the other hand, binding energy of same orbit of same element is changed a little by an atomic surrounding state and environment. State analysis of element is possible by measuring this change variation called chemical shift.

Additionally, mean free path of electron is not so long because of scattering and absorption process of electron in solid. Therefore, since XPS method can observe only the surface of nm order, it is suitable for thin film evaluation.

Figure 2.10 : Schematic diagram of XPS system.

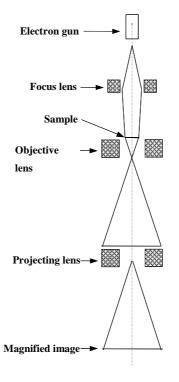

#### 2.3.3 Transmission Electron Microscopy (TEM)

Cross section of the sample is observed by Transmission Electron Microscope (TEM). TEM is microscopic equipment for observing internal structure of a thin sample by radiating electron beam to it. Figure 2.11 shows schematic cross section of a TEM. The principle of TEM is similar to that of optical microscope. In case of TEM, observation is made in a high vacuum, and an electron gun and electromagnetic lenses are used in place of a light source and optical lenses, respectively. Because wavelength of electron beam is less than that of visible ray, resolution of TEM is higher than that of optical microscope. The thickness of sample must be not greater than 0.1 µm so as to transmit electron beam. In some case, Focused Ion Beam (FIB) equipment is used for the lamination of the sample.

Figure 2.11 : Schematic cross section of TEM.

#### **2.4 Characterization Method**

#### 2.4.1 Characterization of MOS Capacitor

#### 2.4.1.1 C-V (Capacitance-Voltage) Measurement

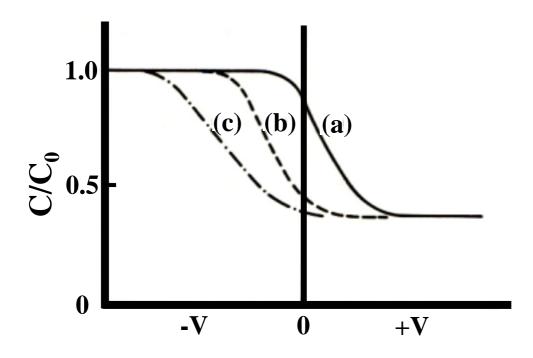

Figure 2.12 shows the ideal of C-V characteristic of p-type MOS diode. Here, "ideal" MOS diode means that there is no interface-trapped charge  $(Q_{it})$ , fixed charge  $(Q_{f})$ , oxide trap charge  $(Q_{ot})$  and mobile ion charge  $(Q_m)$ . The total capacitance (C) of MOS diode equals the oxide capacitance  $(C_0)$  which is accumulated and the silicon capacitance  $(C_{Si})$  connected in series as follows,

$$C = \frac{C_0 C_{Si}}{C_0 + C_{Si}} \quad \text{F/cm}^2.$$

And we obtain

$$\frac{C}{C_0} = \frac{1}{\sqrt{1 + \frac{2\varepsilon_{ox}^2 V}{q N A \varepsilon_{si} d^2}}},$$

where we have written out  $C_{Si}$  explicitly. This equation indicates that the capacitance decreases with increase of the gate voltage.

If applied voltage is negative, depletion layer is not generated but hole is accumulated in surface of silicon. As a result, the total capacitance equals approximately the oxide capacitance ( $\varepsilon_{ox}/d$ ). Beyond strong inversion, even if the voltage increases more than that, the thickness of depletion layer doesn't increase any longer. The gate voltage is called threshold voltage ( $V_T$ ) in this condition as follows.

$$V_T = \frac{\sqrt{2\varepsilon_{Si}qN_A(2\psi_B)}}{C_0} + 2\psi_B$$

Moreover, capacitance is as follows

$$C_{\min} = \frac{\mathcal{E}_{ox}}{d + (\mathcal{E}_{ox} / \mathcal{E}_{Si})W_m}$$

In conventional MOS diode, however, the difference of work function between metal and oxide ( $\phi_{ms}$ ) is not zero and there are varies space charges, such as  $Q_{it}$ ,  $Q_{f}$ ,  $Q_{ot}$ and  $Q_m$ , in oxide and interface of oxide-semiconductor, therefore those affect characteristics of ideal MOS diode. As a result, flat band voltage ( $V_{FB}$ ) is shifted from ideal that as follows,

$$V_{FB} = \phi_{ms} - \frac{Q_f + Q_m + Q_{ot}}{C_0}$$

And C-V carve is parallel shifted as shown in Figure 2.12 (b) because  $\phi_s$ ,  $Q_m$ ,  $Q_{ot}$  is not zero. And in addition to that, when there are much  $Q_{it}$ , that is changed by surface potential. Therefore, curve (c) as shown in Figure 2.12 is shifted and bended by  $Q_{it}$  value.

CET (Capacitance-equivalent-thickness) in other words,  $T_{ox}$  electrical equivalent means the thickness of equivalent SiO<sub>2</sub>, can be calculated from accumulated capacitance of C-V characteristic as follows,

$$CET = \varepsilon_0 \varepsilon_{Si} \frac{S}{C_0}$$

where  $\varepsilon_0$ ,  $\varepsilon_{Si}$  and *S* are permittivity of vacuum, dielectric constant of SiO<sub>2</sub> and area of a capacitor.

In this study, HP4284A (Hewlett-Packard Co. Ltd.) is used for measurement C-V characteristics. The range of measurement frequency is from 10k to 1MHz.

Figure 2.12 : The ideal of C-V characteristics of p-type MOS diode.

# 2.4.1.2 J-V (Leakage Current Density-Voltage) Measurement

It is important to suppress the leakage current of the gate dielectric film as small as possible in order to lower the power consumption of LSI. To estimate the leakage current density, J-V characteristics are measured using semiconductor-parameter analyzer (HP4156A, Hewlett-Packard Co. Ltd.).

# 2.4.2 Characterization of nMOSFET

# 2.4.2.1 Threshold Voltage $(V_{th})$ Measurement

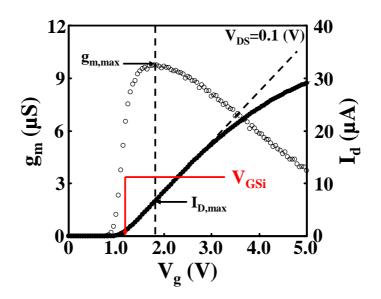

One of the common threshold voltage ( $V_{th}$ ) measurements is the linear extrapolation method with the drain voltage of typically 50-100 (mV) to ensure operation in the linear MOSFET region.

The threshold voltage is determined from the extrapolated or intercepts gate voltage  $V_{GSi}$  by

$$V_T = V_{GSi} - \frac{V_{DS}}{2},$$

where

$$V_{GSi} = V_{GS,\max} - \frac{I_{D,\max}}{g_{m,\max}}.$$

Figure 2.13 : The linear extrapolation method.

# 2.4.2.2 Subthreshold Slope (S.S.) Measurement

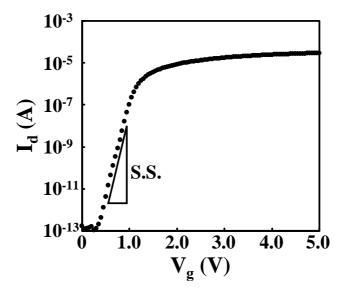

The subthreshold slope (S.S.) is calculated from below equation.

$$S.S. = \left(\frac{d(\log_{10} I_{ds})}{dV_g}\right)^{-1}$$

Figure 2.14 : The subthreshold slope calculated from  $I_d\mbox{-}V_g$  characteristic.

# 2.4.2.3 Split C-V Method

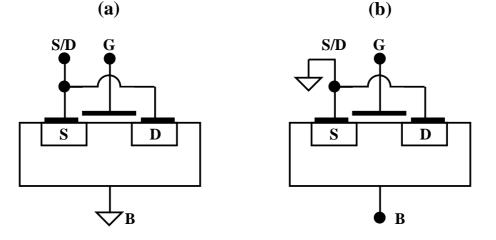

One of the most common measurements to obtain the effective mobility ( $\mu_{eff}$ ) is the split C-V method, which combines gate-to-channel capacitance ( $C_{gc}$ ) and gate-to-bulk capacitance ( $C_{gb}$ ).

$\mu_{eff}$  is obtained from below equation,

$$\mu_{eff} = \frac{g_d L}{WQ_n}$$

where the drain conductance  $g_d$  and the inversion charge density  $Q_n$  are defined as

$$g_{d} = \frac{\partial I_{D}}{\partial V_{DS}}\Big|_{V_{GS} = constant}$$

$$Q_n = \int_{V_{FB}}^{V_{GS}} C_{gc} dV_{GS}$$

$E_{eff}$  is obtained from below equation,

$$E_{eff} = \frac{1}{\varepsilon_{Si}} \left( \left| Q_d \right| + \left| Q_n \right| \right)$$

where  $\varepsilon_{Si}=11.9$  and the depletion charge density  $Q_d$  are defined as

$$Q_d = \int_{V_{FB}}^{V_{th}} C_{gb} dV_{GS}$$

Figure 2.15 : Configuration for (a) gate-to-channel, (b) gate-to-substrate capacitance measurements.

#### 2.4.2.4 Charge Pumping Method

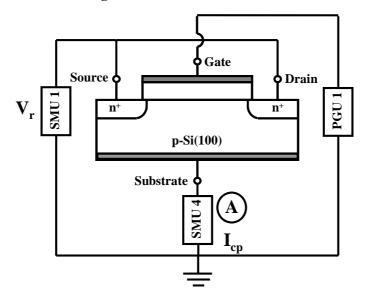

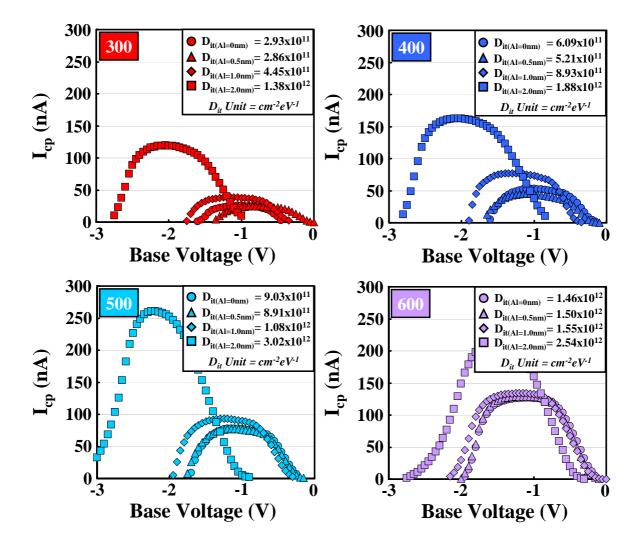

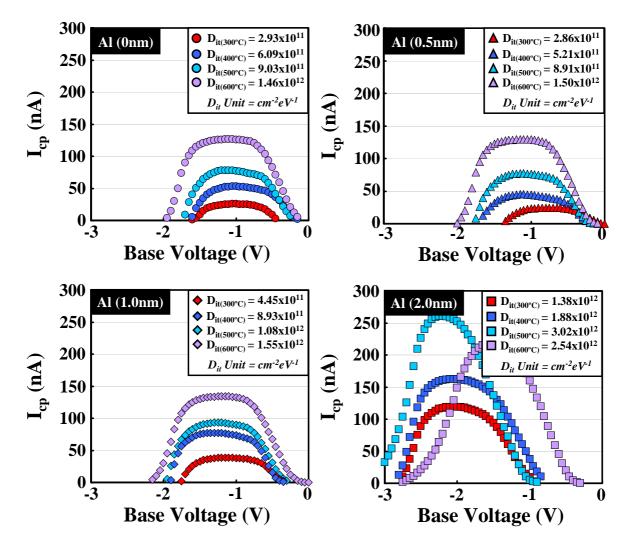

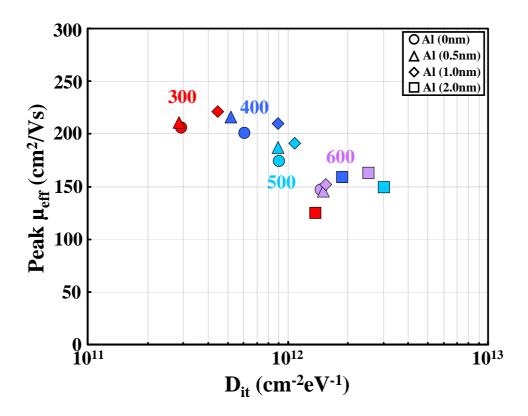

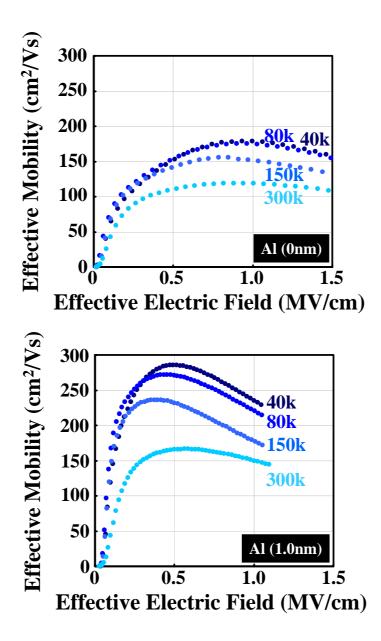

Charge pumping is one of the measurement methods that extract the interface trapped density ( $D_{ii}$ ). Figure 2.16 shows the measurement circuit diagram of charge pumping. The gate of a MOSFET is connected to a pulse generator, a reverse bias (Vr) is applied to the source and the drain, while the substrate current is measured. This current is caused by the repetitive gate pulses the channel between inversion and accumulation.

In this work, we used the square pulse method that extracts the  $D_{it}$  from the charge pumping current  $(I_{cp})$  vs. the pulse base voltage  $(V_{base})$  curve.

$D_{it}$  is obtained from below equation.

$$D_{it} = \frac{I_{cp}}{f * q * Ag}$$

where,

*I<sub>cp</sub>* : Maximum charge pumping current

f: Pulse frequency

Ag : Channel area of MOSFET

Figure 2.16 : Measurement circuit diagram of charge pumping method.

# **Chapter 3**

# **Evaluation of** Al Gate La<sub>2</sub>O<sub>3</sub> nMOSFETs

In this chapter, we discuss electrical characteristics and chemical characteristics at the interface of  $La_2O_3/Si$  and gate electrode/ $La_2O_3$ . Firstly, we investigated the effect of PDA on several heat treatments to select appropriate annealing condition. Then, we performed PMA with this annealing condition and compared with PDA.

# 3.1 The effect of PDA on Al Gate La<sub>2</sub>O<sub>3</sub> nMOSFETs

#### **3.1.1 Experimental Procedure**

La<sub>2</sub>O<sub>3</sub> thin films with physical thickness of 4.5 nm were deposited by MBE systems. These films were subsequently annealed by RTA at 300°C for 5min. Ambient of PDA were N<sub>2</sub>, O<sub>2</sub>, F.G. (Forming Gas) (N<sub>2</sub>:H<sub>2</sub>=97:3). Then, Al electrode was evaporated by bell jar. In nMOSFETs fabrication process, Al metal etched on H<sub>3</sub>PO<sub>4</sub> solution at 45°C.

#### **3.1.2 C-V characteristics of MOS Capacitors**

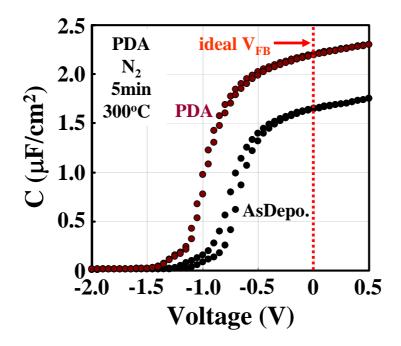

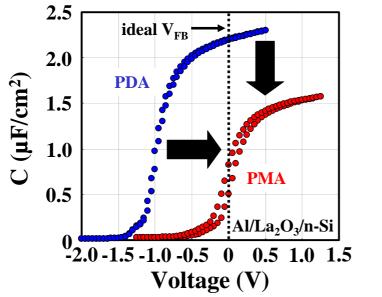

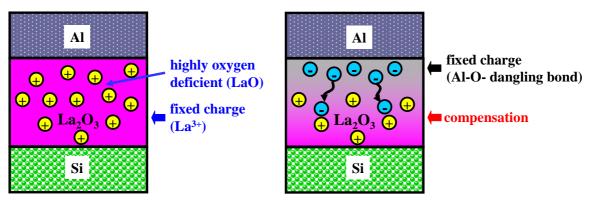

Figure 3.1 shows the C-V characteristics of La<sub>2</sub>O<sub>3</sub> MOS Capacitors with PDA performed in N<sub>2</sub> ambient for 5min. As compared to the without PDA sample (AsDepo.), the flat band voltage ( $V_{FB}$ ) of the PDA sample shifted in a negative direction and the capacitance value increased. Increment of the capacitance value is considered that La<sub>2</sub>O<sub>3</sub> films are densified by PDA treatment. The shifted in a negative direction of  $V_{FB}$  is due to the increment of positive fixed charges (La<sup>3+</sup>) induced during the PDA treatment.

Figure 3.1 : High frequency (100MHz) C-V characteristics of La<sub>2</sub>O<sub>3</sub> MOS Capscitors after PDA treatment.

#### **3.1.3 Electrical Characteristics of nMOSFETs**

# **3.1.3.1** $I_d$ - $V_d$ and $I_d$ - $V_g$ Characteristics

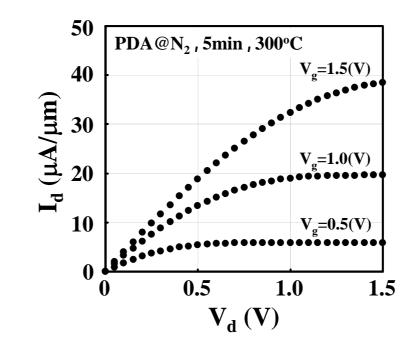

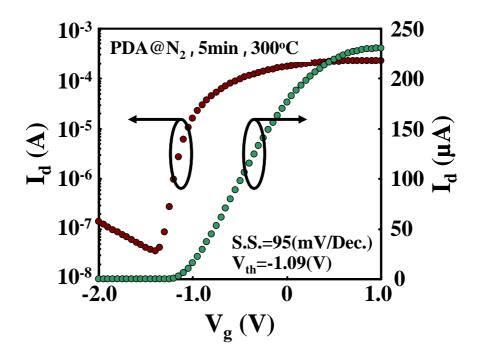

Figure 3.2 and 3.3 show the  $I_d$ - $V_d$  and  $I_d$ - $V_g$  characteristics of Al gate La<sub>2</sub>O<sub>3</sub> nMOSFETs with PDA performed in N<sub>2</sub> ambient for 5 min. From Figure 3.2, we confirmed normal operating as a transistor by well behaved  $I_d$ - $V_d$  characteristic. From Figure 3.3, we confirmed *Normally-ON* characteristic with  $V_{th}$ =-1.09 V and the S.S. of 95 mV/Dec. was obtained.

Figure 3.2 :  $I_d$ - $V_d$  characteristics of Al gate  $La_2O_3$  nMOSFETs after PDA treatment.

Figure 3.3 :  $I_d$ - $V_g$  characteristics of Al gate  $La_2O_3$  nMOSFETs after PDA treatment.

# **3.1.3.2 Dependence of Annealing Ambient on** $V_{th}$ and S.S.

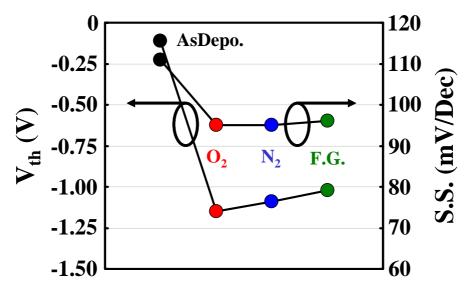

Figure 3.4 shows the dependence of annealing ambient on  $V_{th}$  and S.S.. As compared to the AsDepo., the significant  $V_{th}$  shift towards a negative direction was confirmed in all PDA samples. On the other hand, good property on the value of S.S. was obtained by PDA treatment. From this behavior, PDA has effect on the formation of fairly good quality at the La<sub>2</sub>O<sub>3</sub>/Si interface.

Figure 3.4 : The dependence of annealing ambient on V<sub>th</sub> and S.S..

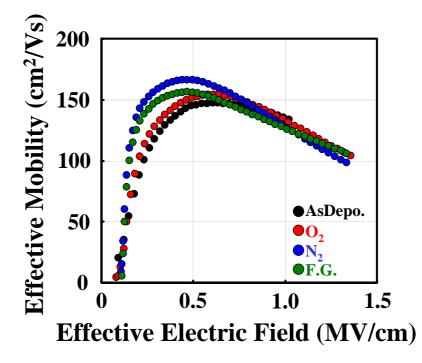

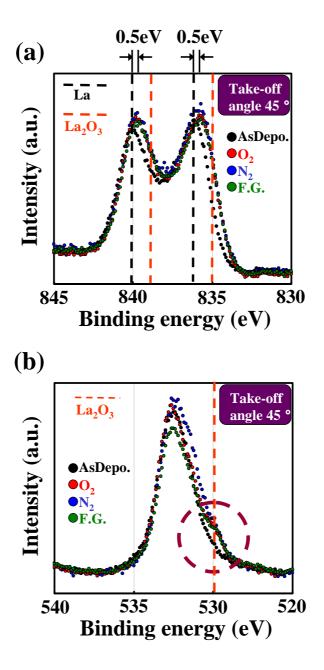

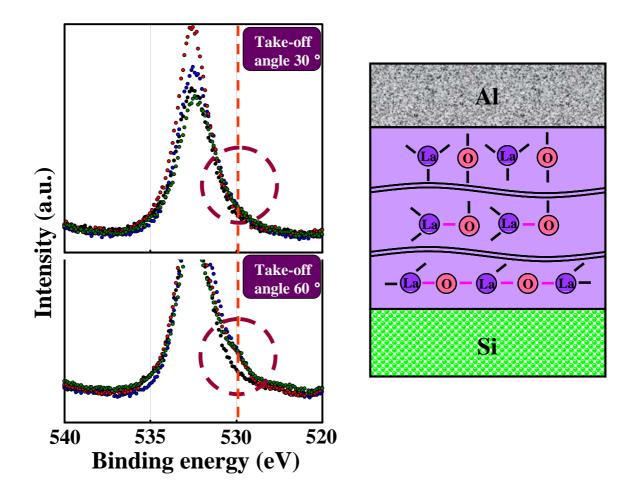

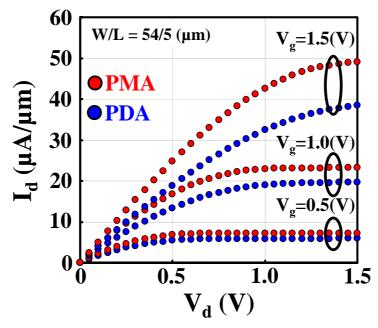

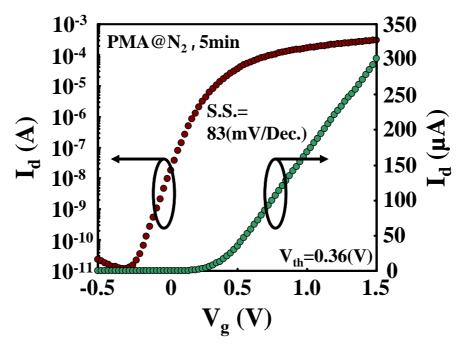

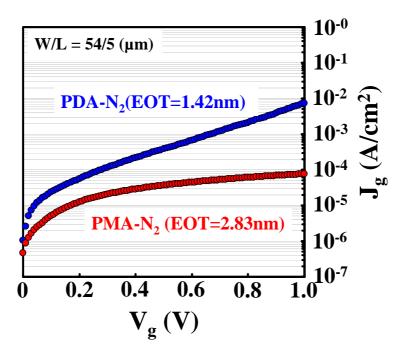

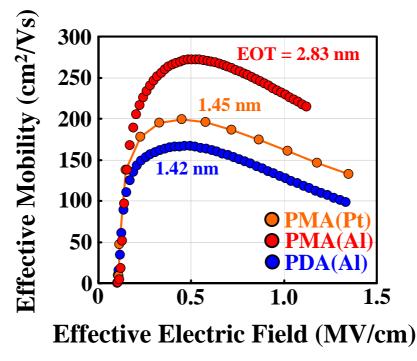

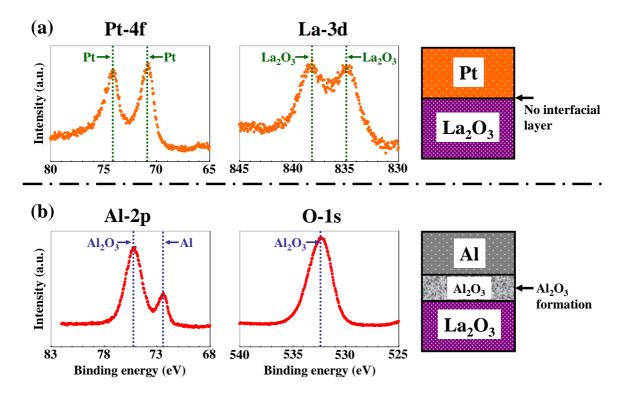

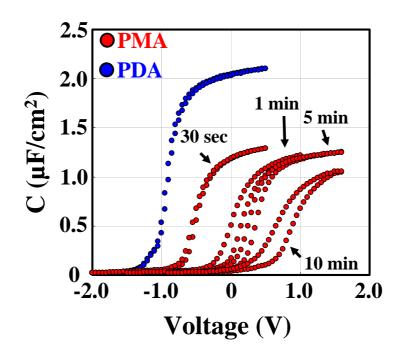

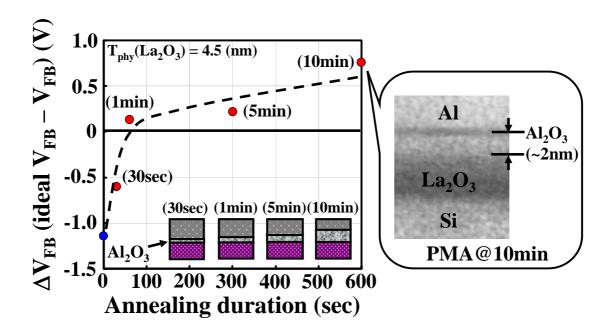

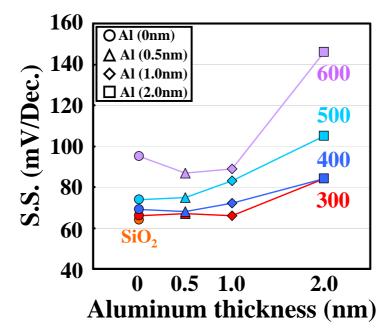

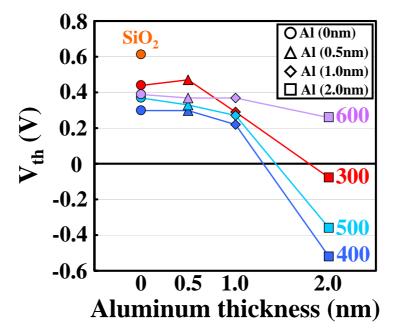

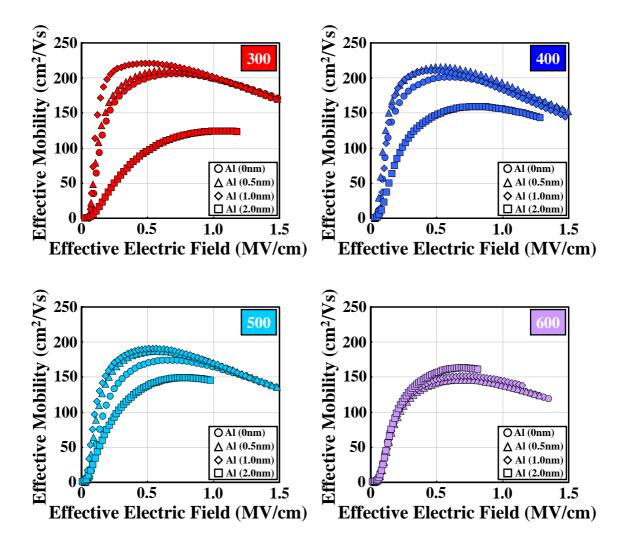

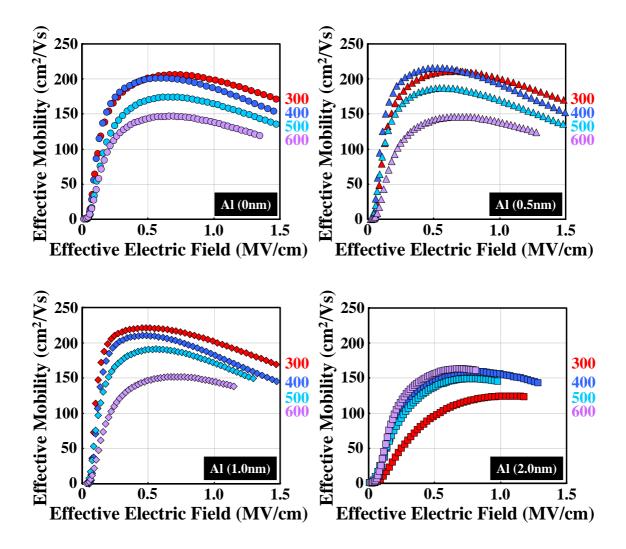

# 3.1.3.3 Effective Electron Mobility ( $\mu_{eff}$ )