東京工業大学 フロンティア研究センター 岩井研究室

TEL:045-924-5471

FAX:045-924-5584

最終更新日:2008.3.16

最終更新日:2008.3.16

|

研究内容 研究内容

● 研究背景

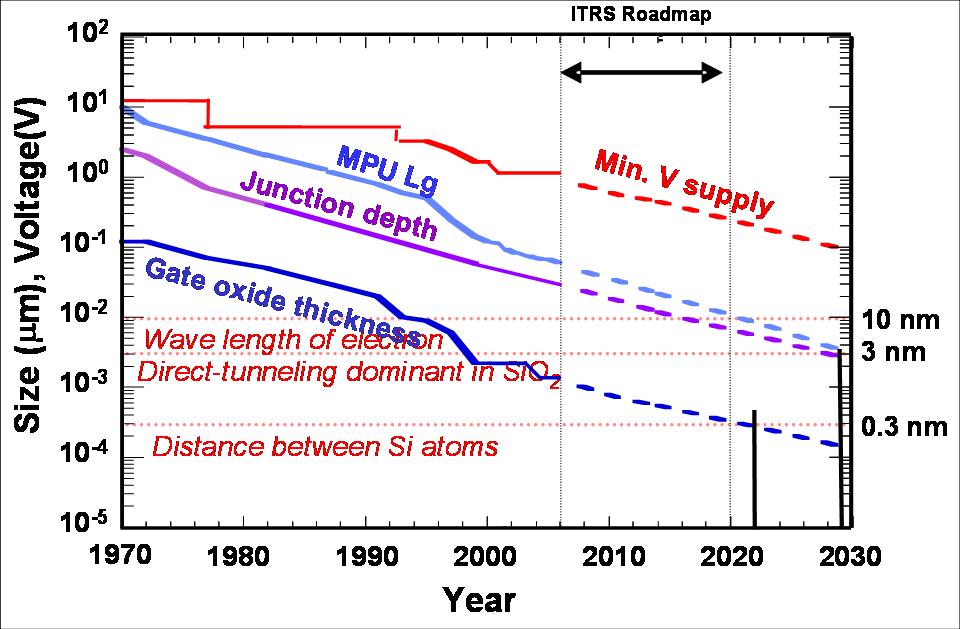

【最先端CMOSの現状】

ゲート長:30nm

ゲート絶縁膜:0.8nm

拡散層:20nm

最先端のCMOSではゲート絶縁膜が0.8nmのデバイスが発表されております。さらなる薄膜化のためにはhigh-kの導入が必須です。

【High-k材料】

現在、有望視されているhigh-kはHfO2, La2O3, MgO, Al2O3などです。EOT<1nmを実現するためにはさらなる新材料が導入される可能性があります。

【CMOS微細化限界の探索】

ゲート長、ソース/ドレインの深さも限界を迎えようとしていまうす。

三次元構造のトランジスタ、特にSiナノワイヤFETやカーボンナノチューブFETの研究が期待されています。

● 研究テーマ

● 研究方針

産業界との緊密な連携

● 国内提携先

SELETE、東芝、日立、アルバック、アルバックファイ

● 国際共同研究

フランス(LETI, LPCS)、米国(NCSU)、台湾(NCTU)、シンガポール(Nanyang大)共同研究中、

● 実験設備

【Simulator】

Synopsys社Taurusを導入したワークステーション。プロセスシミュレーションからデバイスシミュレーションまで行える総合デバイスシミュレータ。

Agilent社のIC-CAPを用いたトランジスタのパラメータ抽出も可能。

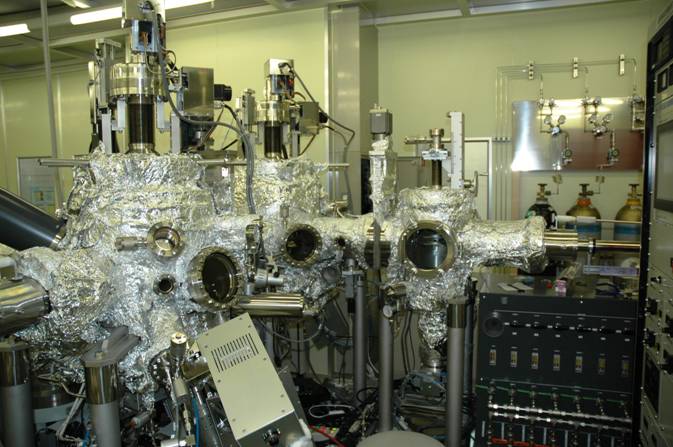

【MBE】

超高真空中(~10-10Torr)で高純度の薄膜を堆積させることが可能。

電子銃を4つ装備しており、同時に堆積することも可能。

現在は酸化物を堆積するために使用している。

【熱処理装置】

赤外線によるイメージ加熱炉。酸化性、還元性雰囲気での処理が可能。

【熱酸化炉】

熱酸化炉。1100℃までのドライ、ウェット、パイロ酸化が可能。

【Sputtering】

5元のターゲットを有しており、in-situで積層膜の堆積が可能。

【蒸着器】

ジュール熱による金属の蒸着が可能。

【RIE】

F系ガスによる反応性エッチング、Arによるスパッタエッチングが可能。

【FESEM】

表面形状、断面形状を観察。透過電子の検出器も装備。

【エリプソ】

誘電体の積層薄膜の膜厚測定。

【測定装置】

トランジスタの電気特性を測定することが出来るシステム。

低周波ノイズ(1/fノイズ)の測定も可。

【高周波測定装置】

40GHzまでのSパラメータ、NF、パワー特性、歪み特性が可能。

|